電子發(fā)燒友網(wǎng)核心提示:對于系統(tǒng)設(shè)計人員而言,提高積體電路的整合度既是好消息,也帶來新問題。好消息是,在每一個硅晶片的新制程節(jié)點(diǎn),晶片設(shè)計人員都能夠在一個晶片中封裝更多的元件,例如更多的處理器、加速器和周邊控制器。一個晶片內(nèi)建更多的元件,意味著更好的性能、更低的功率消耗以及更小的體積。

但是,更高的整合度也意味著以前由系統(tǒng)設(shè)計人員所做出的決定,現(xiàn)在是由晶片設(shè)計人員來完成,系統(tǒng)設(shè)計團(tuán)隊能夠?qū)崿F(xiàn)的創(chuàng)新會越來越少,也不太容易突出產(chǎn)品優(yōu)勢。更重要的是,系統(tǒng)設(shè)計人員要能夠理解晶片設(shè)計人員的思路,同時還可以自由地突顯自己產(chǎn)品的優(yōu)勢。

根據(jù)應(yīng)用分類 采用對應(yīng)方式

目前俄羅斯電子市場很多最重要的應(yīng)用都符合某種模式,包括視訊監(jiān)控、無線和有線通訊,以及高階工業(yè)控制等。在這些應(yīng)用中,系統(tǒng)收集寬頻訊號,處理這些訊號以提取出資料,進(jìn)行大運(yùn)算量的分析,做出判斷,然后實施判斷。

例如,監(jiān)控系統(tǒng)須要處理來自攝影機(jī)的1,080條逐行掃描視訊。系統(tǒng)對視訊串流進(jìn)行處理、增強(qiáng)邊緣、識別出目標(biāo),最后分離出感興趣的目標(biāo)。此一處理過程通常使用標(biāo)準(zhǔn)化,雖然相對簡單,但是需要大運(yùn)算量的演算法。

在下一階段,處理單元的目標(biāo)分析功能將更強(qiáng)大,例如探測是否有入侵,或識別出某些特定的人。這些演算法可能是專用的,會經(jīng)常變化。最后經(jīng)過分析,確定目前的狀態(tài)是否須要觸發(fā)警鈴、鎖閉大門,或者向公共安全機(jī)構(gòu)發(fā)出警報。

以軟體實現(xiàn)系統(tǒng)功能易被復(fù)制

設(shè)計團(tuán)隊採用叁種不同的途徑來實現(xiàn)這些系統(tǒng)。第一種途徑最初是透過運(yùn)行在微處理器上的軟體來實現(xiàn),最近,則採用特定應(yīng)用標(biāo)準(zhǔn)產(chǎn)品(ASSP),或者功能強(qiáng)大的32位元微控制器。

設(shè)計團(tuán)隊對軟體進(jìn)行除錯、確定演算法,然后檢查系統(tǒng)性能。如果任務(wù)運(yùn)行太慢,設(shè)計人員會將其移動到獨(dú)立的中央處理器(CPU)上。或者,如果有數(shù)位訊號處理(DSP)核心等合適的加速器,IC上有向量處理器,則將其移動到加速器上,進(jìn)而對其進(jìn)行加速。當(dāng)所有的任務(wù)滿足其時序要求后,可以在功能、時序和功率消耗上對系統(tǒng)進(jìn)行最終的驗證。

在監(jiān)控實例中,系統(tǒng)控制軟體會運(yùn)行在一顆CPU核心上。標(biāo)準(zhǔn)影像處理演算法可以運(yùn)行在DSP核心標(biāo)準(zhǔn)函式庫的程式上,還可以手動編寫更復(fù)雜的專用演算法,在所有可用CPU核心并存執(zhí)行。

這種設(shè)計方法有很大的優(yōu)勢。其重點(diǎn)一直是軟體,也就是系統(tǒng)功能。由于大部分系統(tǒng)功能體現(xiàn)在軟體上,因此當(dāng)出現(xiàn)問題或須要進(jìn)行改動時,就比較容易對系統(tǒng)進(jìn)行修改。

但是,透過CPU或DSP核心上的軟體來執(zhí)行一種演算法,是最慢而且最耗損效能的方法。因此,對于性能或效率要求較高的系統(tǒng),以軟體為中心的方法并不是最佳方法。系統(tǒng)不同的特性體現(xiàn)在軟體上,因此有同樣硬體的競爭對手很容易復(fù)製這些軟體,或者軟體有可能被敵方所利用。

以硬體當(dāng)作解決方案 設(shè)計彈性差

系統(tǒng)設(shè)計的另一種方法是直接根據(jù)系統(tǒng)要求來開發(fā)硬體設(shè)計,同時編寫在此一硬體上運(yùn)行的軟體。這是開發(fā)大部分特殊應(yīng)用積體電路(ASIC)所採用的方法。一開始,系統(tǒng)規(guī)劃人員確定需要哪些CPU、加速器、記憶體和控制器,把這些需求告訴晶片設(shè)計團(tuán)隊,由他們來開發(fā)ASIC。

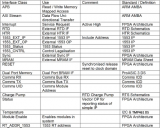

在實例系統(tǒng)中,規(guī)劃人員可以選擇一對安謀國際(ARM)核心來運(yùn)行系統(tǒng)軟體,授權(quán)協(xié)力廠商影像處理引擎來處理最初的影像處理任務(wù),在進(jìn)程最后,針對復(fù)雜演算法設(shè)計訂製韌體編寫DSP管線程式碼。當(dāng)進(jìn)行IC設(shè)計時,軟體團(tuán)隊會針對設(shè)計中完全不同的叁種引擎來使用叁組程式設(shè)計和除錯工具。

以硬體為中心的方法有很大的優(yōu)勢。在所有方法中,它能夠?qū)崿F(xiàn)最大系統(tǒng)速率及最高功能效率。但這需要熟練的IC設(shè)計團(tuán)隊,且在高階製程節(jié)點(diǎn),投入也會很大。而且,一旦設(shè)計好ASIC,就很難修改硬體或改正錯誤,也很難應(yīng)對需求的變化,此一過程會很慢而且成本很高。軟體方案能夠節(jié)省時間,但是犧牲了ASIC方法的優(yōu)點(diǎn)--速度和功率消耗。

因此,雖然在理論上以硬體為中心的方法最適合對性能和功率消耗要求較高的設(shè)計,但在實際情況下,設(shè)計團(tuán)隊只有在預(yù)期會有很大的銷售量能夠滿足成本要求,降低風(fēng)險時,或者他們知道系統(tǒng)硬體在產(chǎn)品生命週期過程中不會有太大的變化時,才會開發(fā)ASIC。實際上,面臨關(guān)鍵設(shè)計難題的團(tuán)隊很難實現(xiàn)系統(tǒng)IC設(shè)計時,通常會放棄ASIC方法,轉(zhuǎn)而購買與系統(tǒng)IC設(shè)計功能相近的ASSP。

活用現(xiàn)場可編程門陣列

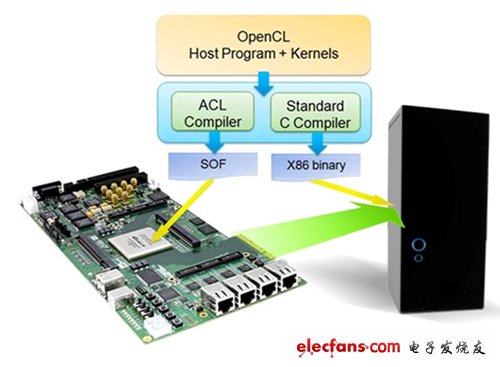

現(xiàn)場可編程門陣列(FPGA)是系統(tǒng)設(shè)計人員的第三種方案(圖1)。在很多方法中,F(xiàn)PGA一直是以軟體為中心採用CPU架構(gòu)的方法,與以硬體為中心的ASIC方法之間的一種做法。在FPGA中實現(xiàn)的演算法,并不像軟體那么容易進(jìn)行修改,但是修改FPGA配置要比投入生產(chǎn)新版ASIC容易得多,即使這種修改只是在幾個金屬層上。

圖1 現(xiàn)場可編程門陣列發(fā)展藍(lán)圖

相反地,與在軟體中運(yùn)行任務(wù)相比,在FPGA中運(yùn)行相同的任務(wù)會非常快,而且功率消耗也很低。但是FPGA通常要比相等價格的ASIC速度慢,功能效率也要低一些。

因此,當(dāng)一種僅採用軟體的解決方案無法滿足速度和功率消耗要求,無法找到能夠突出產(chǎn)品優(yōu)勢的ASSP,或者使用ASIC不能滿足預(yù)算要求,達(dá)不到預(yù)期的產(chǎn)量,無法支援往后的系統(tǒng)改動時,系統(tǒng)設(shè)計人員會轉(zhuǎn)向採用FPGA。對于FPGA供應(yīng)商,這種情況經(jīng)常出現(xiàn),在最近幾年,F(xiàn)PGA的銷售要比其替代方案好得多。

在監(jiān)控實例中,設(shè)計人員可以結(jié)合使用運(yùn)行系統(tǒng)軟體的工業(yè)標(biāo)準(zhǔn)微處理器,以及實現(xiàn)商用硅智財(IP)進(jìn)行標(biāo)準(zhǔn)影像處理和訂製設(shè)計DSP管線的FPGA。這樣一來,F(xiàn)PGA中的設(shè)計在功能模組層級上類似于ASIC,而在閘級實現(xiàn)起來卻是完全不同。

針對任務(wù)選擇最佳實現(xiàn)方法

在理想情況下,系統(tǒng)開發(fā)人員不必在多種方法上進(jìn)行選擇。開發(fā)人員可以針對每個任務(wù)來選擇最佳實現(xiàn)方法。可以在相應(yīng)的CPU軟體中實現(xiàn)很少改變而且不關(guān)鍵的任務(wù)。透過標(biāo)準(zhǔn)定義性能和功率消耗非常關(guān)鍵的任務(wù),如此一來,這些任務(wù)不會改變,成為固定硬體。而有可能改變并且需要硬體支援的任務(wù),則在FPGA可程式設(shè)計邏輯架構(gòu)內(nèi)實現(xiàn)。

在過去的幾個硅晶片製程世代中,這實際上是常用的方法。那時的整合度較低,微處理器、加速器、復(fù)雜介面控制器及FPGA都是獨(dú)立的晶片。但是在90奈米(nm)製程世代,除了FPGA架構(gòu)外,系統(tǒng)單晶片(SoC)包括這些所有功能,而且由SoC設(shè)計人員而不是系統(tǒng)設(shè)計人員來確定大部分實現(xiàn)方法。系統(tǒng)設(shè)計人員選擇最合適的SoC,編寫自己的軟體,實現(xiàn)FPGA與SoC靈活的介面,進(jìn)而突出產(chǎn)品優(yōu)勢。

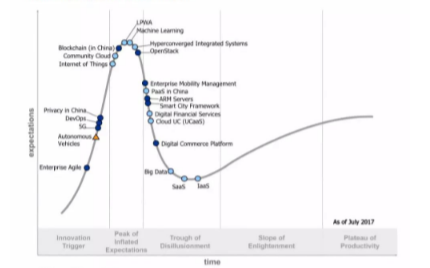

現(xiàn)在,情況又發(fā)生了變化。晶片開發(fā)人員能夠使用大量的電晶體,支援FPGA的硅晶片融合。功能強(qiáng)大的微控制器增加專用硬體,因此它們看起來像是ASIC SoC。ASIC和ASSP能夠含有功能強(qiáng)大的32位元CPU,因此看起來像高階微控制器。新的SoC FPGA系列同時含有多核心CPU和專用硬體模組,契合實際需求,可支援系統(tǒng)設(shè)計人員根據(jù)不同的任務(wù)要求來選擇軟體、專用硬體或是可程式設(shè)計邏輯。

設(shè)計人員可以採用這類融合晶片,在一對功能強(qiáng)大的CPU核心上實現(xiàn)系統(tǒng)軟體及影像處理演算法的多執(zhí)行緒部分。他們可以在DSP硬式核心和可程式設(shè)計架構(gòu)上實現(xiàn)其他演算法,這些都是在一個晶片上實現(xiàn)。

日益攀升的開發(fā)成本,使得ASIC的應(yīng)用領(lǐng)域越來越少,而硅晶片融合發(fā)展趨勢可支援實現(xiàn)叁種系統(tǒng)層級解決方案。微控制器、ASSP和FPGA變得幾乎是一樣的,但有一個重要的不同點(diǎn)。出于技術(shù)和智慧財產(chǎn)權(quán)法律的考慮,只有FPGA能夠?qū)崿F(xiàn)最先進(jìn)的可程式設(shè)計邏輯架構(gòu)。因此只有FPGA支援系統(tǒng)設(shè)計人員可在硬體層級實現(xiàn)其突出產(chǎn)品優(yōu)勢的策略。

硅晶片融合帶來各種可能

硅晶片融合將為今后幾年的系統(tǒng)開發(fā)確定方向。一方面,將看到高階微控制器和ASSP成為系統(tǒng)的硬體基礎(chǔ),這些系統(tǒng)硬體將實現(xiàn)商品化,在市場上系統(tǒng)產(chǎn)品之間的不同體現(xiàn)在軟體上。另一方面,也會看到突出硬體優(yōu)勢、採用FPGA架構(gòu)的系統(tǒng)脫穎而出。

這種趨勢會進(jìn)一步加速,塬因是兩種新出現(xiàn)的技術(shù):叁維(3D)IC和異質(zhì)結(jié)構(gòu)程式設(shè)計系統(tǒng)。3D IC技術(shù)支援完全不同技術(shù)的IC整合,例如FPGA、微處理器、動態(tài)隨機(jī)存取記憶體(DRAM)和射頻(RF)等,在一個堆疊中實現(xiàn)這些技術(shù),沒有獨(dú)立IC的晶片間時序和電源成本問題。此一趨勢的一個早期例子是英特爾(Intel)凌動(Atom)E6x5C系列,其整合Atom CPU和Altera FPGA。Atom為軟體提供業(yè)界標(biāo)準(zhǔn)架構(gòu),而FPGA能夠建立專用加速器和介面控制器。

E6x5C系列還滿足另一種新出現(xiàn)的技術(shù)的需求--異質(zhì)結(jié)構(gòu)程式設(shè)計環(huán)境。理想情況下,系統(tǒng)開發(fā)人員只須要編寫并除錯一個CPU的軟體就可以開始設(shè)計。然后,開發(fā)平臺會幫助他們找到關(guān)鍵程式碼片段,在多個CPU核心上分配任務(wù),共用快取記憶體,為關(guān)鍵程式碼核心建立硬體加速器。透過這種方法,設(shè)計團(tuán)隊能夠細(xì)緻地調(diào)整設(shè)計,直至其滿足時序和功率消耗要求。

這種開發(fā)環(huán)境的一個例子是Altera現(xiàn)在正在進(jìn)行的OpenCL-FPGA計畫(圖2)。其目的是提供單一的環(huán)境,讓系統(tǒng)開發(fā)人員能夠在其中採用C語言開發(fā)程式,隔離需要大量運(yùn)算的核心,產(chǎn)生平行硬體引擎來加速核心,整合最終的硬體軟體系統(tǒng)。

圖2 OpenCL-FPGA計畫

在提高硅晶片整合度需求的推動下,融合功能逐漸將系統(tǒng)所有主要電子模組整合到一個封裝內(nèi),讓系統(tǒng)開發(fā)人員能夠集中精力來突顯其最終產(chǎn)品的優(yōu)勢。FPGA表面上看起來越來越像ASSP和微控制器,而實際上增強(qiáng)系統(tǒng)開發(fā)人員突出硬體優(yōu)勢的能力。新出現(xiàn)的3D IC技術(shù)及異質(zhì)結(jié)構(gòu)開發(fā)環(huán)境將加速FPGA系統(tǒng)級IC從傳統(tǒng)微電子世界中脫穎而出。

圖3 硅晶片融合將為FPGA開創(chuàng)出更多應(yīng)用可能。

電子發(fā)燒友App

電子發(fā)燒友App

評論