本文核心提示:在設計上能減少結構探索時間的C語言平臺,在結構上如何以新思考突破?如何形成一個具有特色的C語言平臺,是的SoC設計達到最佳化呢?

以往半導體業者大多使用FPGA(Field Programmable Gate Array)製作樣品(Prototype),接著鎖定幾項晶片重要規格,依此找出最適合該晶片的結構,這種方式最大缺點是作業時間非常冗長。然而,C語言平臺的設計方式則是,利用軟體模擬分析檢討晶片結構,以往FPGA平臺的樣品,大約需要半年左右的結構探索時間,如果採用C語言平臺的設計方式,只需要花費約2周~1個月的時間。

目前開發最快的是日本沖電氣,以ARM為基礎的整合平臺及設計環境可應用在晶圓專工的先進技術,根據沖電氣的規劃,在內部適用C語言平臺設計技術的SoC,是使用了三種架構,分別是:「μPLAT」+軟體、「μPLAT」+專用加速器度(accelerator)+軟體、硬體連線(hard wired)電路。

在「μPLAT」+軟體的部份,傳統FPGA也有支援此功能,因此IC設計公司可以利用IP來源業者的Process Core,再以μPLAT為基礎開發SoC,例如目前ARM已經將ProcESS Core,封裝成軟體提供客戶使用。而關于「μPLAT」+專用加速器度(accelerator)+軟體、硬體連線(hard wired)電路結構開發的晶片的部份,就是利用C語言平臺設計方式使開發更效率化。此外,「μPLAT」+專用加速器度(accelerator)+軟體中,專用加速器度還分成兩種執行方式,分別是:將C語言資料轉換成System C,再將SySTem C輸入至動作合成工具內,最后嵌入硬體連線(hard wired)電路,以及利用合成使Process Core特定化,接著在該Process Core進行C語言演算作業。采用第一種方式的合成動作方式,可以使晶片發揮低耗功化效果,第二種的特定化Process Core合成方式,以資源共用的觀點而言確實相當有效,不過耗功上經常不如第一種的合成動作方式。

圖說:半導體業者大多使用FPGA制作樣品,依此找出最適合該晶片的結構,這種方式最大缺點是作業時間非常冗長。(School of Computer Science)

C語言平臺擺脫傳統刻板觀念

關于C語言平臺的SoC設計方式的流程是,首先需要從客戶端接收要求,以SoC處理的「C語言/C++描述的演算」與該SoC使用方法的「use case」,并收取「演算(Algorithm)測試環境」然后再開始進行SoC開發作業。此時必需先檢查收取的原始碼(Source Code),確認是否適合動作合成或是組合軟體,不適合的場合,則檢討原始碼的修正進行架構探討。由于該工程被賦予「高精度評估」的角色,因此已經擺脫傳統「設計」的刻板印象,此時短期可量產的優先度比品質更高,例如1個月內完成探索的設計,只進行代表性項目的驗證,如此就能夠縮短探索工程的驗證時間,至于驗證品質則在探索之后的后段工程透過設計方式維持。

結構探索工程又分成:結構草案的檢討,以及結構初期模型的制作與檢驗。結構草案的檢討是根據原始碼的分析結果,決定使用「動作合成的硬體連接」,或是專用處理器。功能不太複雜的晶片,要求低制作成本與低耗功時,大多選擇動作合成方式;要求相似功能進行復合性處理時,通常會選擇專用處理器方式。決定基本方針后立即檢討包括,演算位元的寬度、并聯處理電路的結構、動作頻率、與軟體的搭配等等問題,接著制作晶片的結構模型,再利用虛擬樣品模擬器(virtual prototyping simulator)驗證,模擬器除了晶片功能之外,還能夠分析包含晶片外部的資料轉送等系統整體與晶片的所有效能。

采用C語言平臺的設計方式,只需要花費2周~1個月的時間,就可以完成模擬分析檢討晶片的結構。(National Center for Ecological Analysis and Synthesis)

目前在進行合成所面臨的問題

選擇動作合成方式時會面臨下列問題,分別是:演算轉換至System C化的工程數減少、轉換后以System C化為對象的高速化與高精度化等問題,因此System C化時演算部位必需以UnTImed模型封裝,介面的部位則以定時模型封裝,利用上述溷合封裝追加埠,加上變數的有效位元長度設定等最低限度追加處理作業,就可以達成System C化目標。

目前動作合成工具技術上還不成熟,若直接轉換成System C,閘道(gate)規模與消費電流值會變大,為了達成System C化必需特別設置Guide Line。有關介面部分,就可以使用原先慣用的雛型,透過再利用方式有效減少工程數,如此一來數千行的演算,大約一周就能夠轉換成System C。

有關專用處理器,利用一般的處理器制作工具,同樣能夠輕易進行最適化探索作業,進而使處理器的開發時間,從以往6個月壓縮至2~3個月。實際開發時必需先進行Profiling描述、決定管線結構,再根據Profiling描述結果,對各SoC進行複合指令等,最佳指令追加作業,依此使參考用處理器達成SoC要求的最佳化目標,最后再利用指令設定,模擬分析估算成本、耗功等效能。

結構探索作業結束后,再整合客戶的要求規格,評估客戶提出的規格時,此時為防與止晶片出現怪異現象,除了動作等級的System C之外,必需使用低抽象度RTL(Register TraNSfer Level)等級的設計資料。一旦取得客戶的許可后就可以同時進行System C的硬體、軟體設計。由于C語言平臺設計方式使用了,C語言演算、System C模型和RTL模型等多種模型,因此必需維持模型之間的理論等價性,然而實際上「形式驗證工具」還未達到實用階段,必需使用一般理論模擬分析,驗證上述設計資料的等價性,其中RTL等級的理論模擬分析非常耗時,因此它已經成為C語言平臺設計有待克服的問題。

目前動作合成工具技術上還不成熟,若直接轉換成System C,Gate規模與消費電流值會變大。(IntercONnect Systems)

C語言平臺的設計的特色

實際上利用C語言平臺的設計方式方面,例如日本某業者,曾經開發以Pentium微處理器使用的壓縮處理技術硬體化的SoC,使其具備MPEG-4單壓縮功能,基于資料處理并聯化對降低動作頻率非常有效等考慮,因此使用動作合成方式使SoC整體達成的硬體連線化目的。由于在結構探索工程中已經針對并聯處理段數,等相異多結構進行評估,因此檢驗結果與實際晶片的量測結果幾乎完全相同,證實C語言平臺設計方式可以實現高精度的結構探索目的。

另外,也有業者在開發應用在行動電話的長時間MP3音樂播放晶片,同樣具備MPEG-4單壓縮功能時,設計上被要求盡量降低耗功,因此設計人員決定採用動作合成方式,使SoC整體達成的硬體連線化目的。此外,該業者為了減少耗功與晶片面積,因此進行演算處理位元寬度最佳化設計,就展開調查各處理作業的資源消耗量,與演算位元寬度的關係,依此制作演算位元寬度、建立調整方桉、進行音質檢驗、決定位元寬度,根據實測結果證實傳統同等級SoC的耗功為60mW,可以降至7mW。

東芝成立小組導入C語言設計平臺

目前可以感受到,隨著半導體制程的微細化,SoC的開發時間越來越長,在此同時短交期、低成本的要求依然沒變,因此大幅提高SoC的設計效率,成為開發SoC時非常重要的課題。以往SoC大多利用高抽象度動level設計硬體,設計資料使用C語言平臺描述,如此就能夠在SoC樣品晶片完成前,開始進行軟體驗證、修正作業。

所以,東芝在2005年就成立「R-CUBE」小組專研新晶片的前期設計規劃,來因應此一變化,R-CUBE高階設計環境主要是由,軟、硬體協調驗證環境、結構探索環境、高階驗證環境、高階合成環境,和整體驗證環境等等,5個次環境構成。

實際的想法是,設計流程中最初會使用結構探索環境,此時規格書中會將所有功能當作ANSIC語言/C++演算描述,并將該演算分成實現軟硬體兩大單元。至于分割的妥當性則利用效能分析工具驗證,如果驗證無誤就進入下個階段。此時設計流程可分成, 軟、硬體協調驗證,以及硬體的執行(ImplementATIon)兩大部份,軟、硬體協調驗證環境會整合了可以實現硬體部份的C語言平臺描述,以及微處理器核心的C語言平臺描述,并製作SoC整體的硬體模型。上述驗證會先確認軟、硬體之間的介面是否有不妥,接著進行軟體整體的驗證與修正作業,由于此時要求實機的1/10~1/100左右的模擬分析速度,因此硬體的模式必需使用高抽象度C語言平臺進行描述。

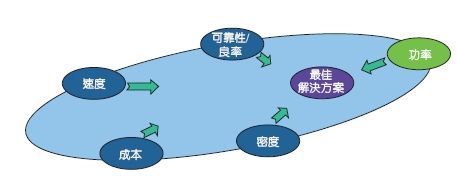

圖說:沖電氣採用「μPLAT」+軟體的合成動作方式,可以使晶片發揮低耗功化效果。(Tanner Research)

在硬體的執行設計方式方面,首先以人工方式將硬體的演算C語言平臺轉換成System C,再使用高階驗證環境驗證此System C的描述,該環境包含多種工具,例如,利用形態檢查器驗證System C描述意義的工具,以及是否已經成為高階合成用資料的工具等等。高階驗證環境還包含東芝開發的可以檢查驗證進度(coverage)的工具, 它可以防止遺漏檢查,進行Line Coverage)、分岐含蓋范圍、條件含蓋范圍等檢查,經過驗證的System C的描述,再利用高階合成環境轉換成RTL描述。

目前高階合成工具無法以一次的合成作業,獲得令人滿意的高品質輸出,必需對C語言平臺描述進行修正,并作反覆數次的高階合成動作。如果晶片已經備妥全模組的RTL描述,就利用整體驗證環境進行晶片整體驗證作業,在該環境下使用理論模擬器(Emulator)與硬體加速器(accelerator)等驗證專用電腦,再以時脈循環(clock cycle)的時序(timing)精度驗證SoC整體,若驗證沒有異常就結束高階設計作業,接下來的晶片設計則與傳統RTL設計完全相同。

整體開發時間只有傳統的1/3左右

在實際設計例子上,東芝所開發的液晶電視用SoC,就此採用這樣的架構平臺開發設計,此晶片有三個設計作業適合上述設計環境,分別是,統一平臺的開發、減少開發軟體的TAT(Turn Around Time),以及使用高階合成獲得的RTL描述。

在統一平臺的開發部分,由于晶片目標是廣用衍生型的SoC,并且主要訴求是開發容易,因此必需將共通部位定義成統一平臺,此時最重要的是On Chip匯流排的結構,與記憶體次系統的定義,設計人員利用上述環境,討論出如何能夠定義成最適宜的統一平臺。

具體步驟首先檢查匯流排的存取流通量(Throughput)、延遲、仲裁(Arbitration)功能、匯流排的擴充性(Scalability),接著利用C語言平臺描述進行效能模擬分析,再透過

定性優劣比較作定量性分析,透過該分析就能夠定義最適當的統一平臺。

在減少開發軟體的TAT,由于是以廣用SoC為目標,所以必需充分應用軟、硬體協驗證,因此在樣品晶片完成前,就需要成功驗證大部份的軟體,因此從樣品晶片公佈,一直到發佈軟體工具為止,整個的開發時間只有傳統的1/3左右,主要原因是Stream data能夠使用協調驗證所致。

此外即使使用應用協調驗證環境,并不表示如此一來就不需要進行樣品晶片的實機驗證,因為C語言平臺描述的精度還有無法驗證Bug,例如記憶體初期化與電晶體的初期化設定錯誤,以及有關插入時序的不協調,一般協調驗證都無法檢查。

在高階合成取得RTL的描述部分,這顆晶片的MPEG2解碼器后處理部分,非常適合使用高階合成,尤其是將動作頻率高達266Mhz的后處理方塊,當作82K閘道(gate)規模的電路合成,可以獲得媲美人工設計的結果。至于軟、硬體協調驗證使用的硬體部位C語言平臺描述,就可以利用這顆晶片的C語言平臺描述作基礎,只改寫變更部分即可。

IC設計業者已經開始建立C語言設計平臺

目前許多IC設計公司已經開始建立C語言平臺設計技術,應用在半導體晶片的設計,該技術除了能夠使晶片架構在短時內進行比較、檢討作業,同時還可以應用在各種SoC(System On a Chip)結構的最佳化設計。以行動電話的語音處理晶片為例,C語言平臺設計技術可以使晶片的耗功降至1/10,預定今后2~3年內,市場上將會有20~30%的SoC,是採用C語言平臺設計技術。所以,通常SoC的開發要求同時滿足各式各樣規格,然而同時滿足高效能、低耗功、低制作成本的特性.

電子發燒友App

電子發燒友App

評論