雖然在技術上仍然是新事物,但用于主機到設備連接的 Compute Express Link (CXL) 標準已迅速在服務器市場占據(jù)一席之地。

據(jù)報道,該標準旨在提供建立在現(xiàn)有 PCI-Express 標準之上更豐富的 I/O 功能集,其最顯著的是優(yōu)勢在于設備之間的緩存一致性。從相關組織處獲悉,CXL的主要應用方向是把CPU連接到服務器中的加速器,但希望能夠在物理上仍然是通過 PCIe 接口上連接 DRAM 和非易失性存儲。

這是一個雄心勃勃但得到廣泛支持的路線圖,在短短三年內使,CXL 便成為事實上的先進設備互連標準,這就導致競爭對手標準 Gen-Z、CCIX 以及截至昨天的 OpenCAPI 都退出了競爭。

雖然 CXL 聯(lián)盟在贏得互連戰(zhàn)爭后快速取得勝利,但聯(lián)盟及其成員還有很多工作要做。假如在產(chǎn)品方面,第一批帶有 CXL 的 x86 CPU 幾乎沒有出貨——這很大程度上取決于你所說的英特爾 Sapphire Ridge 芯片所處的邊緣狀態(tài)。

來到功能方面,設備供應商要求獲得比比 CXL 的原始 1.x 版本更多的帶寬和更多的功能。贏得互連戰(zhàn)爭使 CXL 成為互連之王,但在此過程中,這意味著 CXL 需要能夠解決競爭對手標準設計的一些更復雜的用例。

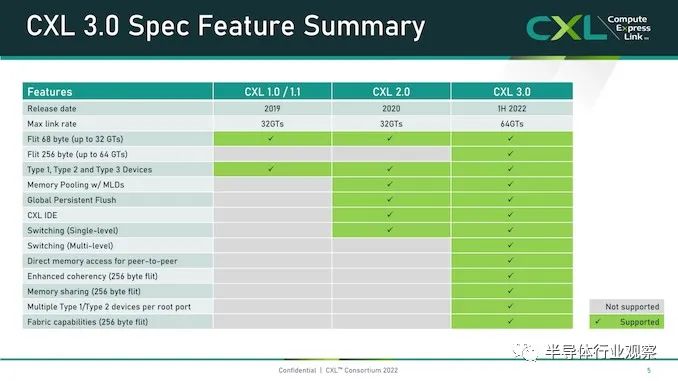

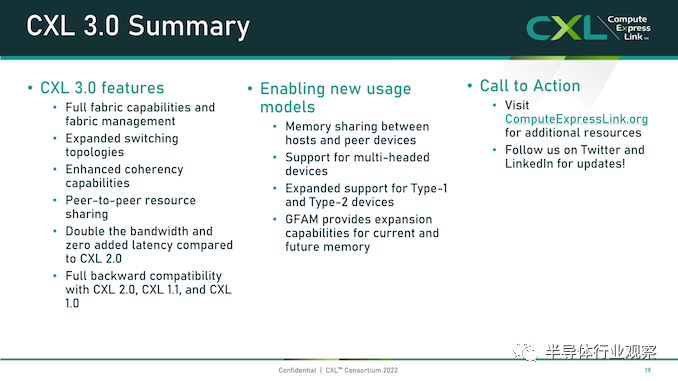

為此,在本周的 2022 年閃存峰會上,CXL 聯(lián)盟在展會上宣布了 CXL 標準的下一個完整版本 CXL 3.0。這是繼2020 年底發(fā)布 2.0 標準并引入了內存池和 CXL 開關等功能之后的一次重要更新。

報道指出,CXL 3.0 側重于互連的幾個關鍵領域的重大改進。第一個是物理方面,CXL 將其每通道吞吐量翻了一番,達到 64 GT/秒。同時,在邏輯方面,CXL 3.0 大大擴展了標準的邏輯能力,允許復雜的連接拓撲和結構,以及在一組 CXL 設備內更靈活的內存共享和內存訪問模式。

? ?

CXL 3.0:建立在 PCI-Express 6.0 之上

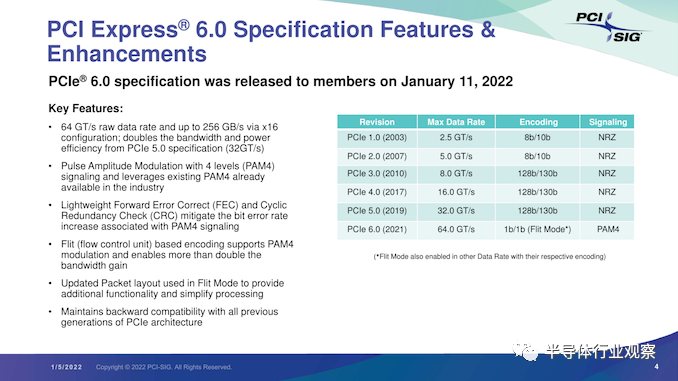

首先,我們從物理方面開始了解新版本的CXL 技術。資料顯示,新版本的標準提供了期待已久的更新,以合并 PCIe 6.0。CXL 之前的兩個版本,也就是 1.x 和 2.0,都是建立在 PCIe 5.0 之上的,所以這是自 2019 年 CXL 推出以來,其物理層的首次更新。 ? PCIe 6.0本身是對 PCI-Express 標準內部工作的重大更新,它再次將總線上的可用帶寬量翻了一番,達到 64 GT/秒,對于 x16 卡來說,這可以達到 128GB/秒。據(jù)報道,這個速度是通過將 PCIe 從使用二進制 (NRZ) 信號轉換為四態(tài) (PAM4) 信號并結合固定數(shù)據(jù)包 (FLIT) 接口來實現(xiàn)的。借助這種方法,能使其速度翻倍而不會在更高頻率下運行的缺點。由于 CXL 反過來構建在 PCIe 之上,這意味著需要更新標準以應對 PCIe 的操作變化。 ?

? CXL 3.0 的最終結果是它繼承了 PCIe 6.0 的全部帶寬改進——以及前向糾錯 (FEC) 等所有有趣的東西——與 CXL 2.0 相比,CXL 的總帶寬增加了一倍。 ? 值得注意的是,根據(jù) CXL 聯(lián)盟的說法,他們能夠在不增加延遲的情況下完成所有這些工作。這是 PCI-SIG 在設計 PCIe 6.0 時面臨的挑戰(zhàn)之一,因為必要的糾錯會增加進程的延遲,導致 PCI-SIG 使用低延遲形式的 FEC。盡管如此,CXL 3.0 在嘗試減少延遲方面更進了一步,導致 3.0 具有與 CXL 1.x/2.0 相同的延遲。 ? 除了基本的 PCIe .60 更新之外,CXL 聯(lián)盟還調整了他們的 FLIT size。CXL 1.x/2.0 使用了一個相對較小的 68 字節(jié)數(shù)據(jù)包,而 CXL 3.0 將其增加到了 256 字節(jié)。更大的 FLIT size是 CXL 3.0 的關鍵通信變化之一,因為它在header FLIT 中為標準提供了更多位,而這些位又是啟用 3.0 標準引入的復雜拓撲和結構所必需的。盡管作為一項附加功能,CXL 3.0 還提供了一種低延遲“變體”FLIT 模式,該模式將 CRC 分解為 128 字節(jié)“sub-FLIT granular transfers”,旨在減輕物理層中的存儲和轉發(fā)開銷. ? 值得注意的是,256 字節(jié)的 FLIT 大小使 CXL 3.0 與 PCIe 6.0 保持一致,后者本身使用 256 字節(jié)的 FLIT。和它的底層物理層一樣,CXL 不僅支持在新的 64 GT/秒傳輸速率下使用大型 FLIT,而且還支持 32、16 和 8 GT/秒,本質上允許新協(xié)議功能以更慢的傳輸速率使用. ? 最后,CXL 3.0 完全向后兼容早期版本的 CXL。因此,設備和主機可以根據(jù)需要降級以匹配硬件鏈的其余部分,盡管在此過程中會失去更新的功能和速度。 ? ?

CXL 3.0 特性:增強的一致性、

內存共享、多級拓撲和結構

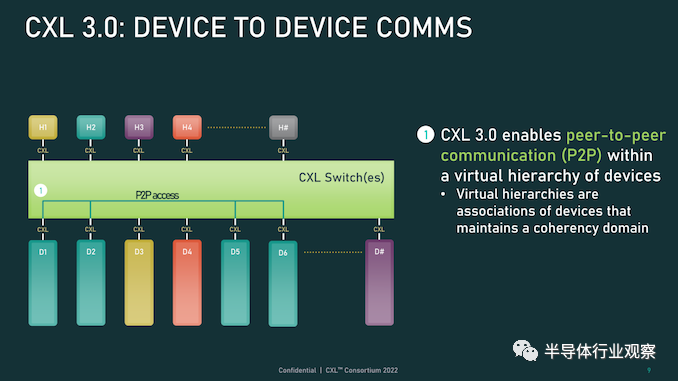

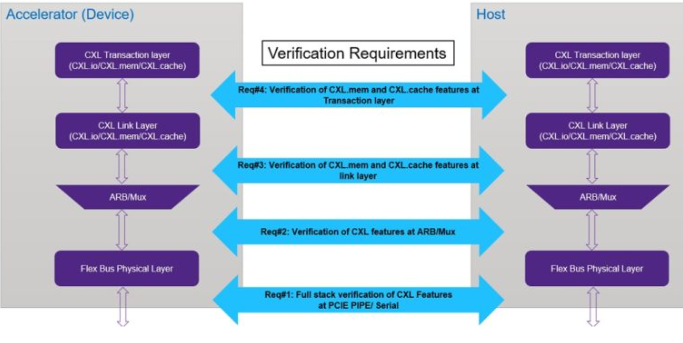

除了進一步提高整體 I/O 帶寬外,上述針對 CXL 的協(xié)議更改也已實施,以支持標準內的新功能。CXL 1.x 是作為(相對)簡單的主機到設備標準而誕生的,但現(xiàn)在 CXL 是服務器的主要設備互連協(xié)議,它需要擴展其功能以適應更高級的設備,并最終適應更大的用例。 ? 從特性級別開始,這里最大的新聞是該標準更新了具有內存的設備的緩存一致性協(xié)議(Type-2 和 Type-3,用 CXL 的說法)。正如 CXL 所說,增強的一致性允許設備支持使主機緩存的數(shù)據(jù)無效。這取代了 CXL 早期版本中使用的基于偏差的一致性方法,為了保持簡潔,保持一致性不是通過共享內存空間的控制,而是通過讓主機或設備負責控制訪問。相比之下,Back invalidation更接近真正的共享/對稱方法,允許 CXL 設備在設備進行更改時通知主機。 ? 包含Back invalidation也為設備之間的新對等連接打開了大門。在 CXL 3.0 中,設備現(xiàn)在可以直接訪問彼此的內存,而無需通過主機,使用增強的一致性語義來通知彼此它們的狀態(tài)。從延遲的角度來看,跳過主機不僅速度更快,而且在涉及交換機的設置中,這意味著設備不會通過請求占用寶貴的主機到交換機帶寬。雖然我們稍后會進入拓撲,但這些變化與更大的拓撲密切相關,允許將設備組織成虛擬層次結構,其中層次結構中的所有設備共享一個一致性域。 ?

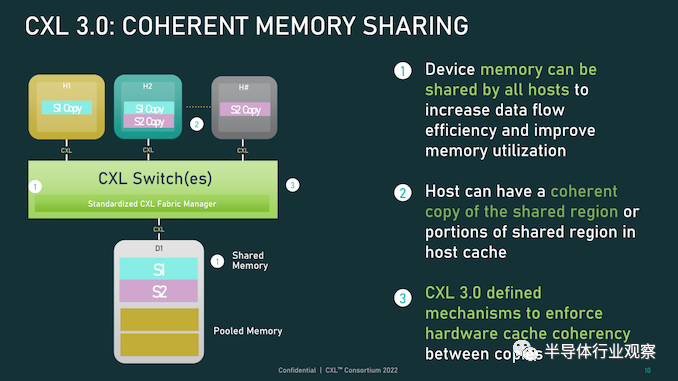

? 除了調整緩存功能外,CXL 3.0 還對主機和設備之間的內存共享進行了一些重要更新。CXL 2.0 提供了內存池,其中多個主機可以訪問設備的內存,但必須為每個主機分配自己的專用內存段,而 CXL 3.0 引入了真正的內存共享。利用新的增強一致性語義,多個主機可以擁有一個共享段的一致副本,如果設備級別發(fā)生變化,可以使用反向失效來保持所有主機同步。 ?

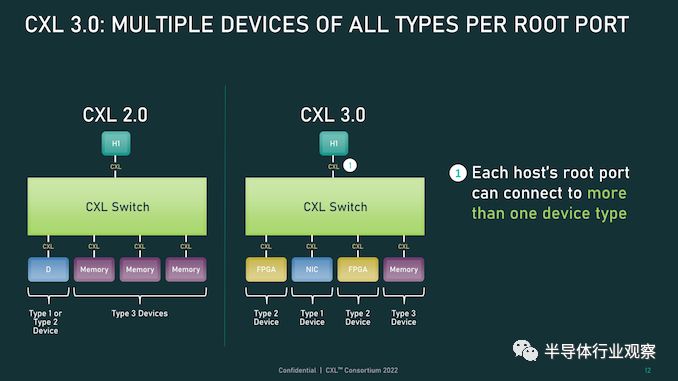

? 然而,應該注意的是,這并不能完全取代池化。在某些用例中,CXL 2.0 風格的池更可取(保持一致性需要權衡取舍),并且 CXL 3.0 支持根據(jù)需要混合和匹配這兩種模式。 ? CXL 3.0 進一步增強了這種改進的主機設備功能,消除了之前對可以連接到單個 CXL 根端口下游的 Type-1/Type-2 設備數(shù)量的限制。 ? CXL 2.0 只允許這些處理設備中的一個出現(xiàn)在根端口的下游,而 CXL 3.0 則完全解除了這些限制。現(xiàn)在,CXL 根端口可以支持 Type-1/2/3 設備的完全混合匹配設置,具體取決于系統(tǒng)構建者的目標。值得注意的是,這意味著能夠將多個加速器連接到單個交換機,提高密度(每個主機更多的加速器),并使新的點對點傳輸功能更加有用。 ?

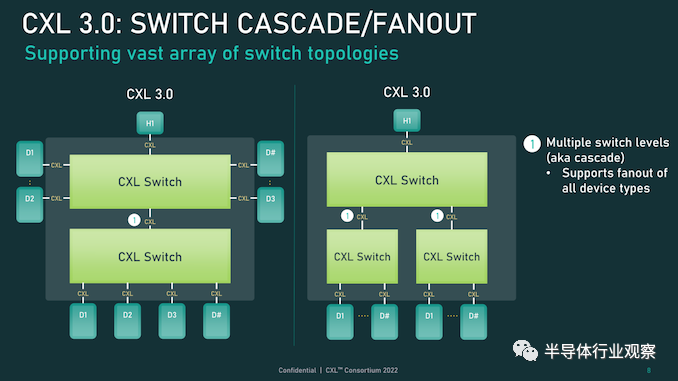

? CXL 3.0 的另一大特性變化是支持多級切換。這建立在 CXL 2.0 的基礎上,該版本引入了對 CXL 協(xié)議交換機的支持,但僅允許單個交換機駐留在主機及其設備之間。另一方面,多級交換允許多層交換機——也就是說,交換機饋入其他交換機——這極大地增加了所支持的網(wǎng)絡拓撲的種類和復雜性。 ?

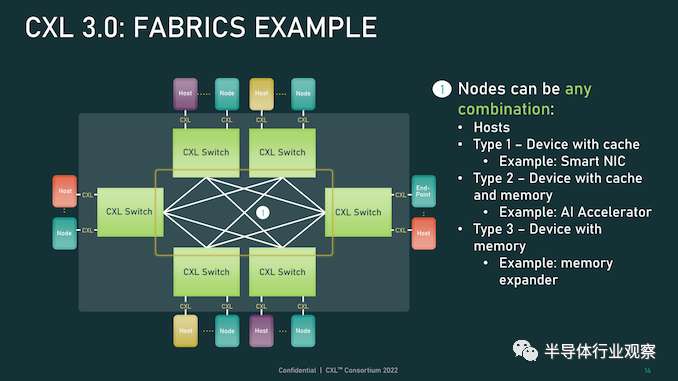

? 即使只有兩層交換機,這也足以實現(xiàn)非樹狀拓撲結構,例如環(huán)形、網(wǎng)狀結構和其他結構設置。并且各個節(jié)點可以是主機或設備,對類型沒有任何限制。 ?

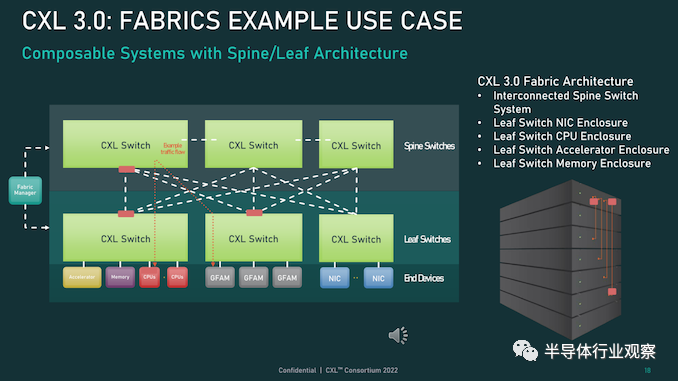

? 同時,對于真正奇特的設置,CXL 3.0 甚至可以支持主干/葉架構,其中流量通過頂級主干節(jié)點路由,其唯一工作是將流量進一步路由回包含實際主機的低級(葉)節(jié)點/設備。 ?

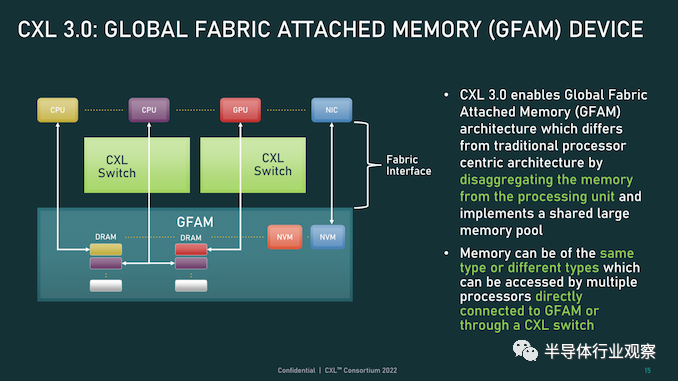

? 最后,所有這些新的內存和拓撲/結構功能都可以在 CXL 聯(lián)盟所稱的全球結構附加內存 (GFAM) 中一起使用。簡而言之,GFAM 通過進一步分解來自給定主機的內存,將 CXL 的內存擴展板(Type-3)理念提升到了一個新的水平。在這方面,GFAM 設備在功能上是它自己的共享內存池,主機和設備可以根據(jù)需要訪問它。GFAM 設備可以同時包含易失性和非易失性存儲器,例如 DRAM 和閃存。 ?

? 反過來,GFAM 將使 CXL 能夠有效地支持大型多節(jié)點設置。正如 Consortium 在他們的一個示例中使用的那樣,GFAM 允許 CXL 3.0 為在 CXL 連接的機器集群上實施 MapReduce 提供必要的性能和效率。當然,MapReduce 是一種非常流行的用于加速器的算法,因此擴展 CXL 以更好地處理集群加速器常見的工作負載是標準的下一步明顯(并且可以說是必要的)。盡管它確實模糊了 CXL 等本地互連的結束位置和 InfiniBand 等網(wǎng)絡互連的開始位置之間的界限。 ? 最終,最大的區(qū)別可能是支持的節(jié)點數(shù)量。CXL 的尋址機制,聯(lián)盟稱之為基于端口的路由 (PBR),最多支持 2^ 12(4096) 個設備。因此,CXL 設置只能擴展至此,尤其是當加速器、附加內存和其他設備迅速占用端口時。 ? 總結一下,完整的 CXL 3.0 標準將于今天,即 FMS 2022 的第一天向公眾發(fā)布。官方上,該聯(lián)盟沒有提供任何關于何時期望 CXL 3.0 出現(xiàn)在設備中的指導——這取決于設備制造商- 但有理由說它不會馬上。隨著 CXL 1.1 主機剛剛交付——更不用說 CXL 2.0 主機——CXL 的實際產(chǎn)品化比標準落后幾年,這對于這些大型行業(yè)互連標準來說是典型的。 ?

? ?

編輯:黃飛

?

電子發(fā)燒友App

電子發(fā)燒友App

評論