功能選擇。2.1 I/O 的簡單配置430I/O 的配置是用軟件來實現的,是通過相應的配置寄存器來實現的。(用到某個 I/O 時,一定要先配置好該 I/O,否則易出錯)2.2.1 I/O 方向設定寄存器 PXDIR如設定 P1.1和 P1.2為 輸出狀態 拉高設定為輸出,拉低設定為輸入(默認)

2022-02-15 06:12:42

計算機的并行打印口上,另一端接在PCB板上的一個十芯插頭,PLD芯片有四個管腳(編程腳)與插頭相連。(如圖) 它向系統板上的器件提供配置或編程數據,這就是所謂的在線可編程(ISP,如下

2012-02-27 10:42:53

(&hfdcan1);HAL_FDCAN_Start(&hfdcan1);這就是我進行初始配置所需的全部。現在,當我想稍微更改設置時,比如重新配置,我使用這種流程:uint32_t

2023-02-06 08:09:04

)放置flash 偏移地址0x50000處,關閉看門狗,重新配置后,發現fpga只更新了硬核,軟核沒有運行。通過測試,發現更新完硬核后,軟核還是找到的第一個程序軟核入口。沒有找到要更新程序軟核入口地址。不知道如何設置,使重新配置后,能夠找到更新程序軟核地址?希望大神幫助。。感激

2017-07-30 10:21:09

CC2530的I/O外部中斷CC2530有18個中斷源,這些中斷源在手冊中如圖,我們一般說的I/O外部中斷,一般是指序號 6、13、15外部輸入中斷,Port x inputs。通用I/O 引腳設置

2016-04-15 16:03:27

主要區別有二點:1、FPGA基本有可編程I/O單元、基本可編程邏輯單元、嵌入式塊RAM、豐富的布線資源、底層嵌入功能單元和內嵌專用硬核等6部分組成。CPLD的結構相對比較簡單,主要由可編程I/O單元

2018-08-28 09:15:53

我有一個系統接收配置文件并將其寫入閃存。之后,所有需要的是重置或電源循環,因此它將加載'升級'并保持'黃金'以防萬一它失敗。我想過使用HWICAP IP,但在我看來,更適合部分重新配置和重新配置而

2020-06-10 13:18:41

“PLL 復位和重新配置”部分。問:是否允許將 Lane D 從 PLL2 切換到 PLL1?是否有我可能忽略的陷阱?問題 2:車道重新配置:我的方法可以嗎?我使用 10G-RCW (XFI) 啟動

2023-04-18 10:32:26

如何用PLL對時鐘進行配置呢?PLL配置時鐘喚醒后還需要重新配置RCC嗎?

2021-11-22 06:30:33

(void)改寫。 我希望在主循環里面重新配置RTC喚醒時間。 因為我發現在RTC中斷中更改這個RTC時間,有的時候會讓我的數據采集出問題,感覺有些時候這部分耗時可能會長一些,會倒是我數據采集的時候丟數據。

我是在系統喚醒后第一時間就調用了rtc重新配置的函數。 希望能夠幫忙解決一下此問題。 感謝!

2024-02-21 06:53:16

你好,我懷疑重新配置PSoC的財產。我已經知道,這個系統的硬件有能力根據PSoC Creator的軟件進行配置。我不知道,一旦你配置了系統,并且你正在運行這個項目,會發生什么,你可以重新配置它,例如

2019-03-28 14:07:42

大家好,我正在使用控制器:PIC18F45K80,IDE:MPLABX IDE和編譯器:XC8 pro。在目前的工作項目中,RB0引腳配置成上電時的上升沿外部中斷。要求重新配置相同的引腳用于上升沿

2019-05-13 12:01:28

。但是,當我再次打開電源時,它不會重新配置。關于在哪里尋找問題的任何建議?現在,FPGA的電源和IO bank的電源來自獨立的電源。這可能是問題嗎?

2020-06-04 16:30:14

第一:STM32 I/O 口的配置1-.1:I/O可以配置成8中不同的模式,輸入四種:模擬輸入,輸入上拉,輸入下拉,輸入浮空; 輸出四種:推挽輸出,開漏輸出,推挽式復用輸出,開漏復用輸出。具體的配置

2021-11-23 07:40:28

我正在使用 STM32L475RC 開發一個項目。根據運行狀態,STM32 在運行模式、低功耗運行模式和關機模式等不同運行模式之間切換。當從運行模式切換到低功耗運行模式時,時鐘也會重新配置。我面臨

2023-01-16 08:50:25

你好我有一個任務是在VC709板上進行部分重新配置的演示。完成所有配置的實現后,生成比特流的準備就可以了。我發出了打開檢查點的命令,然后發出了“write_bitstream”命令。但是,他們就是

2020-06-04 11:10:48

; 通過使用LabVIEW FPGA 模塊和可重新配置I/O(RIO)硬件,NI 為您提供了一種直觀可用的解決方案,它可以將FPGA技術的靈活性整合到測量和控制系統

2009-05-30 17:32:27

用vhdl實現cpld配置fpga,配置成功后在usermode下設置一個重新配置信號,當信號有效時對fpga進行重新配置;fpga配置程序放在flash內;現在遇到的問題是,上電cpld能夠正常配置fpga并且進入usermode ,但是加上重新配置語句過后就不能成功配置fpga,求高人指點~

2013-01-17 22:35:39

嗨,我是學生我研究了如何在SPARTAN6中設計部分重新配置好幾個月,但仍然不知道如何使用它。有我的知識: - 通過planAhead實施設計PlanAhead的部分重新配置設計。 (我

2019-02-22 08:22:33

我每次用vscode打開工程時都需要重新配置esp-idf插件的配置,設置esp-idf與工具鏈的路徑。這是為什么?這是正常的嗎?而且我如果沒打開某個文件夾就進行配置還會出現報錯。如下圖所示。

2023-02-21 07:44:38

為什么配置I/O口:I/O端口寄存器復位后默認為輸入(輸出高阻態);為實現I/O端口功能需要先對端口進行I/O口初始化配置I/O口需要的幾種寄存器:ANSELx(模擬選擇寄存器):0 = 數字I/O

2021-11-24 06:19:54

前言此實驗是通過STM32CubeMX來配置stm32實現按鍵輸入,以此來了解stm32I/O的輸入操作及如何使用HAL庫來實現I/O輸入。本實驗中的按鍵操作使用的是軟件中斷,并未用到stm32

2022-03-01 06:58:08

視野范圍內顯示相關的駕駛信息最終,根據當前的駕駛情況,在中央視野內顯示相關內容 上面描述的內容被我們稱為可重新配置數字儀表板,它實際上具有無限的顯示可能性。“Jacinto 6”系列是支持此類儀表板運行

2018-09-04 14:48:25

請教大家一個問題:做電路原理圖設計時,CPU的I/O接到其他芯片的配置引腳時一般采用何種設計方式?有何設計規則?例:STM32F103VET的I/O接到一款SRAM(IS62WV51216BLL

2016-05-05 11:26:57

無可用I/O服務器類型,以前可以正常使用,后來就不能使用了,有高手知道怎么解決嗎?DSC和OPC都重裝過,還是不行。服務里面NI該啟動的都啟動了,也是不行。DAQ也重新安裝,依舊不行。[/tr]

2018-04-04 10:10:30

回顧之前編程教程,第1篇是I/O篇,I/O主要說明I/O的引腳特性以及如何通過C51控制I/O的電平輸入輸出;第2篇是中斷篇,中斷篇中介紹了中斷系統必要性以及如何使用單片機中的中斷系統(外部中斷0

2022-01-27 07:26:05

喜我使用ICAP原語實現了部分重配置。 (VCU1525板,xcvu9p)我的問題是,IO引腳在重新配置期間是否會出現高阻抗?例如,在我的設計中,部分重配置區域內有DDR4 MIG IP內核。如果

2020-06-10 07:18:05

能否告訴我在 CapSense 按鈕觸發時是否有可能重新配置 I/O 的操作?

我想使用一個 CapSense 按鈕并啟用/禁用電路上的另一個 IC。

這意味著,如果按下 CapSense 按鈕,輸出將永久保持高電平,而如果再次按下,輸出將變為低電平。

我正在使用CYUSBS236開發工具包。

2024-02-23 06:20:57

復用器被送至最終的視頻解碼器播放。u*** 2.0 phy芯片可被輕松連接至pld的任意i/o引腳。大多數pld的i/o引腳都可被編程實現3.3、2.5、1.8或1.5v lvttl/lvcmos

2018-12-28 07:00:06

大家好!我正在使用Spartan6 FPGA為高速DAC提供數據。必要的高速I / O時鐘由PLL實例完成。在我的申請中,我有兩種不同的情況:case1:我需要從80MHz參考(M = 12)產生

2019-07-31 10:59:14

你好Xilinx收發器使用CML IOSTANDARD。在xilinx 7系列示例設計中,有固定的GTREFCLK位置,但其他引腳未配置(txdata / rxdata)在下面的I / O表中,txdata和rxdata引腳未配置CML I / O標準。我如何配置CML I / O標準?

2020-08-13 10:10:53

,我們最初使用.bit文件對FPGA進行編程。當用戶信號觸發重新配置時,我們希望程序從WBSTAR寄存器中提到的地址再次啟動。你能幫忙了解一下設置地址出了什么問題嗎?謝謝你。拉格米PS:我們的目標是最終

2020-06-04 15:10:44

經常重新配置FPGA,并希望在主機系統運行時這樣做。為了澄清,ML555板插入到與我的開發環境不同的系統中。我有一個獨立的平臺電纜USB從我的開發機器到ML555板,它是一個單獨的測試機器。我想在

2019-08-22 09:58:51

新比特流的FPGA。任何人都可以告訴我這是否可能?我只能找到有關使用ICAP進行部分重新配置或從外部Flash進行完整配置的文檔。我想從RAM重新配置,所以我給MicroBlaze一個解壓縮比特流的機會。如果之前有人問過這個問題,我會道歉,但我自己搜索了幾天,卻找不到關于這個主題的任何內容。謝謝!

2020-05-29 17:12:21

是否有任何教程顯示如何使用PowerPC或microblaze作為重配置控制器?我目前使用Impact工具使用部分比特流(ISE和Planahead 12.1)重新配置FPGA,但我想要一個重配置

2019-01-22 11:05:28

我是使用virtex 4的先行者。我正在使用ISE xilinx13.1和verilog。我通過配置LVCOM33,拉式無,轉換速率快,為j6端口的pin2分配了一個時鐘輸入信號。但我無法觀察到波形。任何人都可以指導我 - 如何使用I / O?

2019-09-04 10:35:35

尊敬的先生/女士,我沒有在新項目設計源中指定合成(edif或ngc)網表選項下設置PR項目,使用planahead進行部分重新配置..我在設置分區階段面臨問題..當我在網表視圖中選擇分區時..i沒有設置用于可重新配置分區的分區向導..請告訴如何啟用PR..please幫助

2019-11-05 07:14:38

我們如何在xilinx FPGA中執行運行時重新配置?

2020-07-16 10:24:37

); 如果(adc_raw > 1500)nRelay = 2;// 重新配置 GPIO 作為輸出PIN_FUNC_SELECT(GPIO_PIN_MUX_REG[PIN_LED_RELAY2

2023-03-01 07:25:21

); 如果(adc_raw > 1500)nRelay = 2;// 重新配置 GPIO 作為輸出PIN_FUNC_SELECT(GPIO_PIN_MUX_REG[PIN_LED_RELAY2

2023-04-12 07:57:28

問候語!你能告訴我如何將PIN B5重新配置為常規GPIO嗎?數據表說DEVCFG3寄存器控制這一點。我用這個:但是它不起作用!USB堆棧拋出一個普通的異常!我不使用這個函數,我想用它作為一個普通的PIN。謝謝!

2020-03-18 09:22:50

嗨,我想知道是否可以動態地將ISERDES2重新配置為不同的序列化比率。我檢查了SelectIO用戶指南,但找不到這樣的選項。任何想法都表示贊賞。謝謝湯姆以上來自于谷歌翻譯以下為原文Hi, I am

2019-07-08 08:02:51

嗨,我可以使用內部配置訪問端口(ICAPE2 Primitive)來重新配置FPGA。我的意思是說我有一個加載了一些設計的位文件,我想加載一個全新的位文件/設計,例如存儲在DDR3或一些NAND閃存

2019-03-26 15:37:47

ISERDES2的并行輸入連接到OSERDES2的并行輸出,則會在路徑中添加太多延遲。如果我只使用IBUFDS和OBUFDS并將它們連接在一起,透明模式工作正常(即延遲足夠低)。但是,我需要能夠在不重新配置

2019-06-10 11:55:37

嗨,伙計們,我正在使用CYBL10563,我想知道是否有可能改變UARTTX/RXPIN到數字引腳?我到底想做什么啟用UART。當設備Goesto睡眠時,禁用UARTAND配置TX作為輸出,RX作為

2019-09-24 14:15:54

控制器)。現在,我希望FPGA在啟動時從閃存(SPI或BPI,無關緊要)加載其配置,像往常一樣,但我也希望能夠使用BeagleBone重新編程閃存。我已經閱讀了XAPP583,它講述了微處理器如何重新

2019-03-04 07:35:35

嗨,我有設計工具的浮動許可證,我獲得了另一個節點鎖定許可證,用于部分重新配置。我使用Ubuntu,我無法安裝部分重新配置的許可證。我試過這個:export LM_LICENSE_FILE

2019-01-23 06:45:50

嗨,是否可以完全重新配置具有不同硬件門的FPGA?目前,我沒有PR功能。我想用不同的設計完全重新配置我的Zynq板。假設,我有和門和xor門,兩者都在PL中單獨工作,但可以完全重新配置zynq,以便

2019-04-11 11:55:05

0x00000000

0x81600081 0x00000000 0x000000E7

此重新配置數據在我們的電路板上不起作用。這導致在上電后從 bootROM 進行一些 QSPI 傳輸,然后進行

2023-05-22 09:35:01

嗨,我是學生 我嘗試使用virtex5與部分重新配置教程UG702,但本教程設計為virtex6(ML605)所以我需要修復它 為virtex5創建新的綜合和網表(從源代碼復制.v文件并運行合成

2020-06-16 07:28:38

你好我可以測量將.bit重新配置到PR區域所需的時間嗎?我在論壇中搜索,我得到了使用.bit文件大小和處理器頻率測量時間的近似計算。我正在尋找更準確的近似值。就像盯著計時器并在重新配置后結束它。謝謝阿努普。

2020-04-02 09:21:18

如題,ESP8266每次啟動都要重新配置熱點名稱、加密方式、密鑰、IP、端口號等這些信息嗎?哪位大俠來給講解一下!

2019-04-10 06:35:50

Virtex-5 - 通過DRP動態重新配置DCM的地址和值是什么?我有PLL的電子表格,但沒有DCM的電子表格。

2020-06-16 16:25:11

目前,我的程序實現了RTC的配置,但是因為擔心實時時鐘的精度無法滿足要求,想再程序中加入一些功能,能夠通過上位機重新設置RTC,或者進行校準,剛剛嘗試過第一種方法,可惜沒有實現,直接調用了設置函數,但是調試過程中發現RTC_TimeSet()返回的是錯誤,請問在程序中重新配置RTC應如何實現?

2018-10-10 08:44:08

想通過EDMA來訪問EMIFA,請問此時的EMIFA的時序是否要重新配置,以適應EDMA和CPU的速度?期待ing……

2018-08-07 07:12:02

需要上拉、下拉或漏極開路。

上圖是 GIO 的方框圖,所有通用的 IO口都可以根據需要配置成輸入 / 輸出 或中斷方式,當然也可以根據需要選擇內部上拉或下拉,如果使能I/O口中斷, 則一旦有設定的邊沿

2018-05-25 01:18:28

嗨,我正在進行部分重新配置,我測試了一個不規則形狀的分區(例如L形),在映射步驟中,實現失敗并出現此錯誤:PhysDesignRules:0- 組件:microblaze_0

2019-01-25 10:36:59

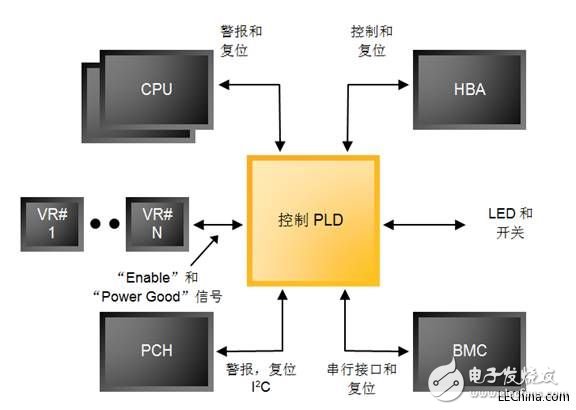

功能。這些是當今面向大邏輯單元、DSP塊和閃存的PLD的完美應用。 大多數消費電子產品都提供了用于控制和配置的I2C接口。有很多參考設計可以下載和重用。為Altera的PLD產品系列優化的VHDL語言

2019-05-14 07:00:12

使用LabVIEW FPGA 模塊和可重新配置I/O 設備開發測量與控制應用通過使用LabVIEW FPGA 模塊和可重新配置I/O(RIO)硬件,NI 為您提供了一種直觀可用的解決方案,它可以將

2009-07-23 08:15:57

供應PCA9555PWR,SMBus I/O 擴展器 PCA9555PWR,具有中斷輸出和配置寄存器的 PCA9555 遠程 16 位 I2C 和 SMBus I

2022-02-09 22:25:43

使用 LabVIEW FPGA 模塊和可重新配置I/O 設備開發測量與控制應用通過使用LabVIEW FPGA 模塊和可重新配置I/O(RIO)硬件,NI 為您提供了一種直觀可用的解決方案,它可以將FPGA技術的靈活性

2009-07-23 08:09:28 66

66 機器和模塊的快速安裝以及不中斷運行情況下的任意重新配置和操作能力是生產靈活性的核心要求之一。Han? ES Press HMC系列讓浩亭打造出能夠無需工具即可進行快速安裝并且極為可靠耐用的接口,其至少可承受10000次插拔操作。

2018-12-06 15:51:09 1171

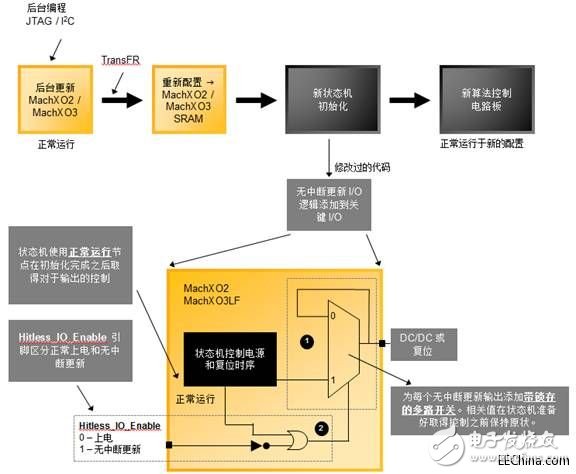

1171 關鍵詞:1200ZE , Lattice , MachXO2 , PLD Lattice公司的MachXO2系列是非易失性的無限制重新配置的可編程邏輯器件(PLD),具有低容量PLD,低成本,低功耗

2019-02-11 09:45:01 919

919

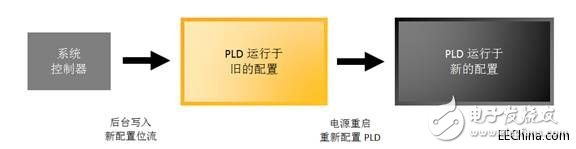

關鍵詞:PLD , SRAM , 可重配置電路 由于SRAM的可重配置PLD(可編程邏輯器件)的出現,為系統設計者動態改變運行電路中PLD的邏輯功能創造了條件。PLD使用SRAM單元來保存字的配置

2019-02-23 14:30:01 675

675

CompactRIO是美國國家儀器(NI)公司生產的一款可重新配置的嵌入式測控系統。CompactRIO系統擁有堅固的硬件架構,其中包含:I/O模塊、帶有可重新配置的現場可編程門陣列(FPGA

2020-07-01 08:20:00 2986

2986 瑞士洛桑聯邦理工學院光子系統實驗室的研究人員發明了一種無需外部設備就能重新配置微波光子的濾波器。這為更緊湊、更環保的濾波器鋪平了道路,這些濾波器將更實用、更便宜。潛在的應用包括檢測和通信系統。

2020-09-08 15:44:42 890

890

以色列一所大學的仿生和醫療機器人實驗室的研究人員設計了一種可重新配置的機器人RTCR,這種機器人能夠利用最小數量的驅動器在空中跟蹤爬臺階和克服障礙。RTCR(可重構連續跟蹤機器人)可以通過一系列鏈接和一個單驅動器改變其整個身體的形狀,并利用它在前進過程中建立自己的軌道。

2020-11-05 14:23:28 1734

1734 真是一段漫長的旅程:從阿基米德到可重新配置儀表板

2022-11-03 08:04:40 0

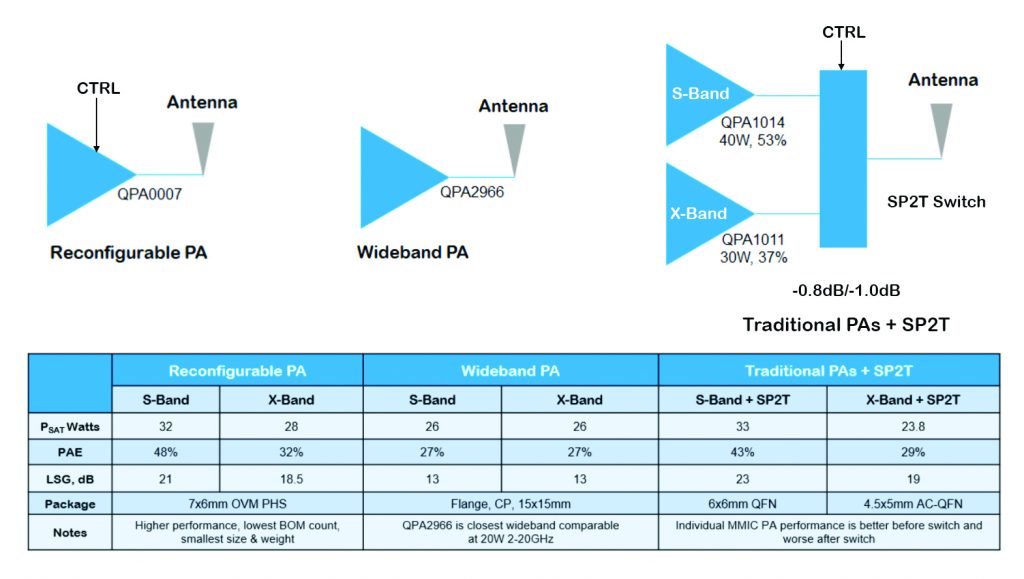

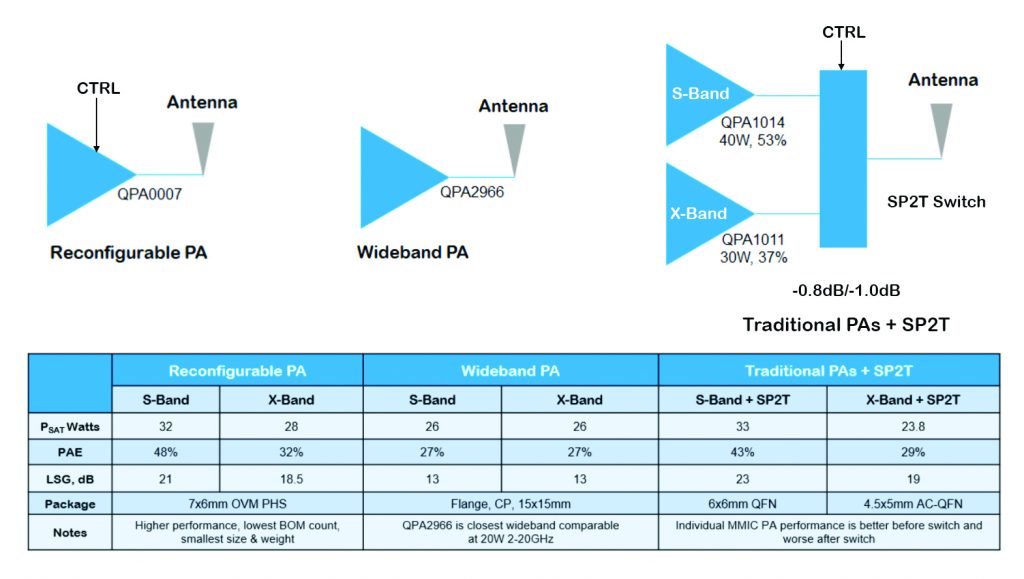

0 本文首次展示了一種基于多頻段發射器設計的可靠商用大功率放大器,該放大器采用了 Charles Campbell 演示的可重新配置的 PA 專利技術 [2,3,4]。可重新配置的 PA 采用可根據每個相關頻段的控制位設置重新配置的單輸入和單輸出匹配網絡。

2023-02-22 11:50:27 417

417

通常情況下,一個IS-IS進程下配置一個NET即可。當區域需要重新劃分時,例如將多個區域合并,或者將一個區域劃分為多個區域,這種情況下配置多個NET可以在重新配置時仍然能夠保證路由的正確性。由于

2023-05-04 11:31:46 696

696

電子發燒友App

電子發燒友App

評論