IP核生成文件:XilinxAlteraIP 核生成文件:(Xilinx/Altera同) IP 核生成器生成ip 后有兩個文件對我們比較有用,假設生成了一個 asyn_fifo 的核,則

2012-08-12 12:21:36

本帖最后由 eehome 于 2013-1-5 09:59 編輯

IP核簡介IP核是指:將一些在數字電路中常用但比較復雜的功能塊,如FIR濾波器、SDRAM控制器、PCI接口等等設計成可修改

2011-07-06 14:15:52

IP核簡介IP核是指:將一些在數字電路中常用但比較復雜的功能塊,如FIR濾波器、SDRAM控制器、PCI接口等等設計成可修改參數的模塊,讓其它用戶可以直接調用這些模塊,以避免重復勞動。隨著CPLD

2011-07-15 14:46:14

你好,我在使用Xilinx網站的IP核時遇到了一些問題。我已經下載了Vivado Webpack,也為此同時下載了IP-Core的許可證。Vivado Webpack工作正常,但我看不到我下載

2018-12-24 13:50:01

XILINX ISE 14.7,我想建立一個工程,里面要調用之前別人的包含SRAM IP核的模塊,需要使用.v和.ngc文件,可是不知道那個.ngc文件該怎么使用,是copy到自己工程目錄然后在工程里面添加進去嗎?為什么加進去后我的工程文件層次就亂了。。。

2015-04-18 14:21:49

`Xilinx系列FPGA芯片IP核詳解(完整高清書簽版)`

2017-06-06 13:15:16

用的xilinx的FFT 9.1版本的ip核 , 仿真出來的結果和我MATLAB算出來的結果差的很多,也沒有倍數關系,scaled因數改了好幾次,沒有溢出,波形大致相同,但是數值上差的太多,已經弄了快兩周了,求做過這個的講講經驗。

2018-07-10 16:16:31

有沒有大神可以提供xilinx FPGA的FFT IP核的調用的verilog 的參考程序,最近在學習FFT的IP核的使用,但是仿真結果有問題,所以想找些參考設計,謝謝

2016-12-25 17:05:38

xilinx dds IP核輸出能不能改為無符號數,因為一般DA轉化器只能轉化正數

2015-09-29 18:30:23

的模擬信號,通過選擇不同的頻率成分來實現信號濾波。濾波器是一種電路,它只允許一定頻率范圍內的信號成分正常通過,而阻止另一部分頻率成分通過的電路,也叫做經典濾波器或濾波電路。實際上,任何一個電子系統都具有

2019-06-28 04:20:07

本人在做電磁兼容試驗時,臨時搭配的濾波器,臨時搭配濾波器沒有外殼,將濾波器放在電源處,CE102效果很好,但是將濾波器放在客戶產品機殼內,濾波器感覺沒有效果,CE102過不了,跟不放效果一樣,請問怎么回事?

2017-12-31 20:32:29

濾波器如何延緩信號?如何設計一款可預測的濾波器?

2021-04-06 09:39:32

什么是濾波器?濾波器分類分類和作用1.濾波器工程上根據輸出端口對信號頻率范圍的要求,設計專門的網絡,置于輸入—輸出端口之間,使輸出端口所需要的頻率分量能夠順利通過,而抑制或削弱不需要的頻率分量,這種

2017-04-22 21:49:23

一、從功能上分;低、帶、高、帶阻。 二、從實現方法上分:FIR、IIR。 三、按元件分類:濾波器可分為:有源濾波器、無源濾波器、陶瓷濾波器、晶體濾波器、機械濾波器、鎖相環濾波器

2020-06-24 16:06:54

求:RC濾波器,LC濾波器設計,橢圓低通濾波器設計資料???1106765606@qq.com

2013-08-18 19:51:23

AD9854官方設計的濾波器將50ohm電阻并聯在濾波器輸入端,而濾波器設計軟件一般都是濾波器輸入串聯電50ohm電阻,輸出并聯50ohm電阻負載,請問二者有什么區別?

2015-12-11 21:45:55

BRAM IP核包括哪幾種類型?Vivado中xilinx_BRAM IP核怎么使用?

2021-03-08 07:11:54

請問C濾波器和RC濾波器在特性和用途上有什么區別嗎?IC的電源管處只用C來濾波。但在很多單片機的AD輸入管腳和傳感器的輸出管腳,有時候會只用C,而有時候也會用RC來濾波。查了產品手冊并無特殊的濾波要求,請問為什么會使用這兩種不同的濾波器。感謝各位大俠賜教!

2015-06-18 11:35:37

我在用fir 核做半帶插值濾波器時,自己寫好tb后,直接用quartus ii 調用modelsim仿真時,出錯,提示說找不到auk_dspip_lib 庫怎么解決呀,謝謝大家

2017-11-24 19:28:15

濾波器使用的比較多。 6、相較于IIR濾波器, FIR濾波器有以下的優點: (1) 可以很容易地設計線性相位的濾波器,線性相位濾波器延時輸入信號,卻并不扭曲其相位,實現簡單, 在大多數DSP處理器

2011-09-24 16:05:53

。iir濾波器運算結構通常由延時、乘以系數和相加等基本運算組成,可以組合成直接型、正準型、級聯型、并聯型四種結構形式,都具有反饋回路。由于運算中的舍入處理,使誤差不斷累積,有時會產生微弱的寄生振蕩。3

2018-03-12 13:21:07

的線性相位濾波器IIR濾波器有以下幾個特點:1、IIR數字濾波器的系統函數可以寫成封閉函數的形式。2、IIR數字濾波器采用遞歸型結構,即結構上帶有反饋環路。IIR濾波器運算結構通常由延時、乘以系數

2016-08-08 08:49:32

第一個問題的基礎上,我是設置unsigned還是signed?3、濾波器的設計,我要給他什么樣子的輸入,仿真看得出什么樣子的結果?部分代碼如下

2017-05-09 14:18:17

剛接觸FPGA,想用EP4CE6F17C8這個型號的altera芯片實現低通濾波器設計,我看能直接調用IP實現,但是網上的資料都是調用MATLAB生成濾波器所需的系數,還只是用于仿真,但是我想用

2017-08-04 19:25:28

形式,分為直接型、級聯型、頻率取樣型和快速卷積型。其中直接型又可以采用串行結構、并行結構、分布式結構。本案例實現了具有線性相位的半串行結構的FIR濾波器。所謂串行結構,即串行實現濾波器的累加運算,將每級延時

2017-08-02 17:35:24

RC濾波器和LC濾波器的區別

2020-12-23 07:34:04

RT所示,這兩個數字濾波器怎么使用呢?目前想濾掉5khz后面的波形進行處理,這兩個濾波器應該怎么操作最好呢?

2018-08-20 07:12:59

Vivado中xilinx_courdic IP核(求exp指數函數)使用

2021-03-03 07:35:03

最近在使用altera的FIR IP核做半帶濾波器,quartus ii軟件也破解了,firIP核也破解了,modelsin仿真也通過了,但是下載不了.sof文件到開發板,大家有用FIR IP核成功實現下板的經驗嗎,求大神指點呀。謝謝!

2018-05-11 16:01:15

fpga實現濾波器fpga實現濾波器在利用FPGA實現數字信號處理方面,分布式算法發揮著關鍵作用,與傳統的乘加結構相比,具有并行處理的高效性特點。本文研究了一種16階FIR濾波器的FPGA設計方法

2012-08-12 11:50:16

。本文研究了一種16階FIR濾波器的FPGA設計方法,采用Verilog HDI語言描述設計文件,在Xilinx ISE 7.1i及ModelSim SE 6.1b平臺上進行了實驗仿真及時序分析,并探討了實際工程中硬件資源利用率及運算速度等問題。

2012-08-11 18:27:41

testbench進行仿真分析,預計第五講或第六講開始編寫verilog代碼設計FIR濾波器,不再調用IP核。這的圖發不出來。1. 添加DDS的IP核(1) 新建一個原理圖文件,添加DDS的IP。(2) DDS

2020-01-18 22:05:50

請教各位大師,quartus ii 中調用fir數字濾波器IP核,可不知道如何設置參數,比如如何設置濾波器的系數

2013-11-23 20:54:41

本人想使用一個verilog低通濾波器,IPCore設置好了,在程序中怎么實例化,第一次使用低通濾波器,不知道怎么實例化,書上鎖相環實例化有例子我會實例化,書上沒有濾波器例子,怎么實例化。或者說

2017-05-17 21:57:11

的主要性能指標7.2 離散傅里葉變換基礎7.2.1 離散傅里葉變換7.2.2 頻域應用7.2.3 FFT/IFFT IP Core的使用7.3 XtremeDSP模塊功能介紹7.4 乘累加結構的FIR濾波器

2012-04-24 09:23:33

除了在Xilinx官網上在哪里能下載到Xilinx IP Core 及license? 如FFTFIRCORDIC核等!

2013-06-20 23:51:39

實現技術,以此為參考,來評估現有的各種實現技術的優劣。RC有源濾波器是由時不變電阻、電容和有源器件組成,根據這個定義,它是不包含電感器的,這樣是可以避免電感龐大笨重的外形,以及相關的磁場和非線性行為。即便是綜合問題,考慮電感器的繞組的電阻和核損,網絡設計也會因此變的復雜。

2019-04-23 12:14:50

通過數字濾波器可以獲得很窄的帶寬。和模擬濾波器相比,理想的高斯濾波器可以實 現。數字濾波器在可接受的價格內有更好的選擇性,如5級電路模擬濾波器的形狀因 子為10,高斯濾波器為4.6。另外,數字濾波器

2017-10-13 09:22:59

FIR濾波器如何定義?為什么要使用FIR濾波器?

2021-04-06 07:48:45

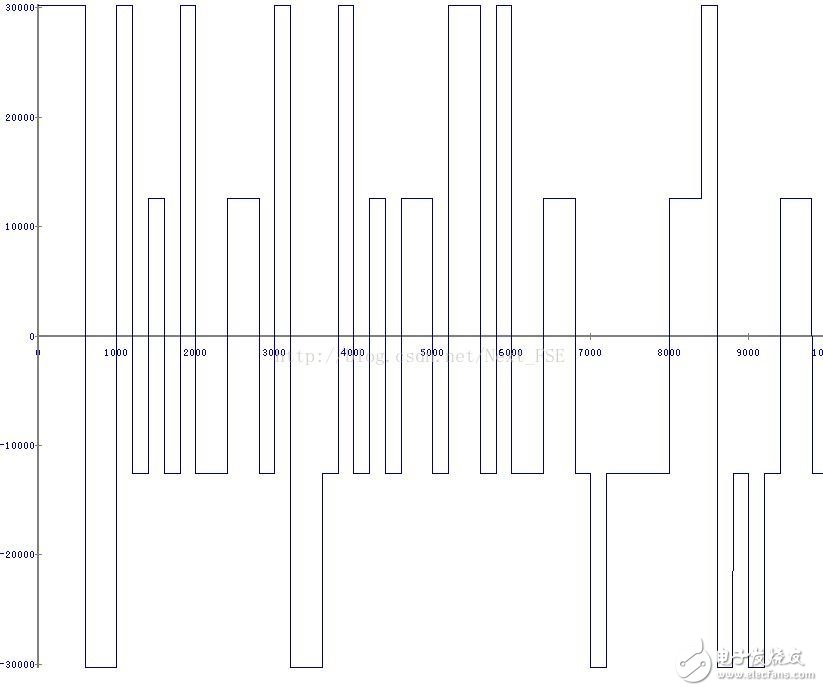

新手見諒使用IP核設計了一個10階3級的CIC濾波器,輸入數據位寬12位,輸出最大22位但是仿真出來的結果有種溢出的感覺,想不通是怎么回事,求各位前輩幫忙分析~~貼出來IP核設置界面,還有matlab處理的結果{:4_108:}

2013-10-13 16:56:12

我們使用quartusII的fir ip核生成了一個濾波器,用AD采集了單頻正弦信號輸入,可是不管輸入頻率多少,濾波器的輸出端口都沒有輸出,不知道這是為什么啊?

2013-08-12 22:49:58

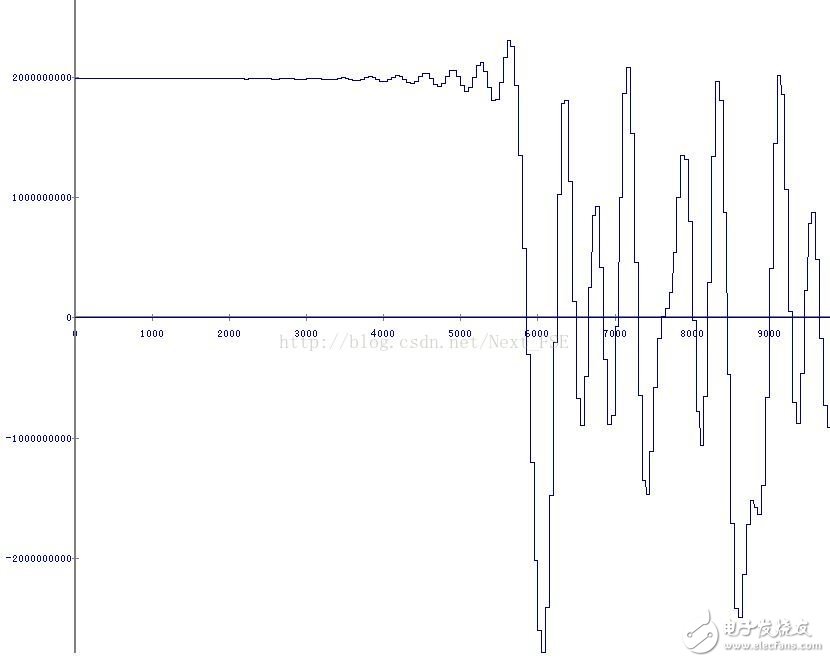

最近進行FPGA學習,使用FIR濾波器過程中出現以下問題:使用FIR濾波器IP核中,輸入數據為1~256,濾波器系數為,coef =-1469,-14299 ,-2185,10587

2018-11-02 17:17:57

有找到關于添加IP的文章A simple BBP for RF Transceivers [Analog Devices Wiki] 我想直接使用Xilinx的IP核,但是vivado建立的IP核

2018-08-13 08:03:00

最近在做一個FIR低通濾波器,利用Matlab 產生濾波系數,導入到Quartus中,再利用其中的FIR IP核進行濾波器設計,在采用分布式全并行結構時,Modelsim 仿真有輸出;如果改為分布式

2018-07-05 08:33:02

各位大佬,xilinx ip核的各個參數的含義從哪里看啊

2021-05-30 10:37:27

各位牛人,xilinx Blockset能做A計權濾波器嗎?

2013-03-12 14:54:22

Programmable Gate Array,現場可編程門陣列)基于查找表的結構和全硬件并行執行的特性,如何用FPGA 來實現高速FIR 數字濾波器成了近年來數字信號處理領域研究的熱點。目前,全球兩大PLD 器件供應商都提供了加速FPGA 開發的IP(IntelligentProperty,知識產權)核。

2019-09-05 07:21:15

基于FPGA的FIR濾波器IP仿真實例 AT7_Xilinx開發板(USB3.0+LVDS)資料共享 騰訊鏈接:https://share.weiyun.com/5GQyKKc 百度網盤鏈接

2019-07-16 17:24:22

和ip-iq檢測方式[1].本文利用軟件建立了基于這兩種方法的并聯有源電力濾波器模型,并進行了諧波分析.在圖1中,有源電力濾波器輸入交流電流ic抵消交流電源中電流is的諧波含量,交流電流is是負載電流iL和全文下載

2010-04-24 09:03:00

我正在嘗試將Xilinx MIG IP Core從1.7版升級到1.9版。 Coregen UI左側有一個方便的“升級IP核”按鈕,但它顯示為灰色。我需要做什么才能進行IP核升級?我在Kintex

2019-11-04 09:26:19

Xilinx 官方提供的技術參數來實現對 IP 核的寫控制。寫命令和寫數據總線介紹DDR3 SDRAM控制器IP

2022-02-08 07:08:01

本文將簡單介紹FIR濾波器的原理,詳細介紹使用Verilog HDL設計并行FIR濾波器的流程和方法。接下來幾篇會介紹串行結構FIR的Verilog設計、使用Quartus和Vivado的IP核

2020-09-25 17:44:38

微波濾波器的分類方法很多,根據通頻帶的不同,微波濾波器可分為低通、帶通、帶阻、高通濾波器;按濾波器的插入衰減地頻響特性可分為最平坦型和等波紋型;根據工作頻帶的寬窄可分為窄帶和寬帶濾波器;按濾波器

2019-11-04 09:10:14

怎么區別交流濾波器與直流濾波器

2015-07-27 00:03:06

相對無限沖擊響應(IIR)濾波器,有限沖擊響應(FIR)能夠在滿足濾波器幅頻響應的同時獲得嚴格的線性相位特性,而數據通信、語音信號處理等領域往往要求信號在傳輸過程中不能有明顯的相位失真,所以FIR

2019-08-23 06:39:46

相對無限沖擊響應(IIR)濾波器,有限沖擊響應(FIR)能夠在滿足濾波器幅頻響應的同時獲得嚴格的線性相位特性,而數據通信、語音信號處理等領域往往要求信號在傳輸過程中不能有明顯的相位失真,所以FIR

2019-08-27 07:16:54

DSP系統中不常用,Quartus和Vivado都沒有提供相關的IP核,因此只能自己進行Verilog設計。本文設計參考自杜勇老師的《數字濾波器的MATLAB與FPGA實現》。本設計將在Vivado環境

2020-09-27 09:22:58

相關濾波器、數字濾波器和虛擬濾波器三者的含義,區別,聯系真的是菜鳥一枚啊,求大神幫助

2015-10-14 20:01:46

你好,有可能設計一個帶50濾波器的帶阻濾波器在PSoC上使用濾波器塊嗎?我試過,但實際上不起作用…謝謝。當做,羅米拉。

2019-09-20 06:41:29

; 數字濾波器由數字乘法器、加法器和延時單元組成的一種算法或裝置。數字濾波器的功能是對輸入離散信號的數字代碼進行運算處理,以達到改變信號頻譜的目的。數字濾波器可用計算機軟件實現,也

2010-05-10 21:04:02

本帖最后由 86xue 于 2011-10-17 11:46 編輯

1.輸入正弦波,用模擬濾波器濾除高頻信號,發現有相位延遲,怎樣才能補償掉?2.輸入不同頻率,延時還不同,所以補償方法還要針對不同頻率都不要有延遲。求解答

2011-10-17 11:46:13

什么是奈奎斯特定理?什么是模擬低通濾波器?什么是數字有限脈沖響應 (FIR) 濾波器?模擬低通濾波器和數字有限脈沖響應濾波器有何不同?

2021-07-29 07:27:13

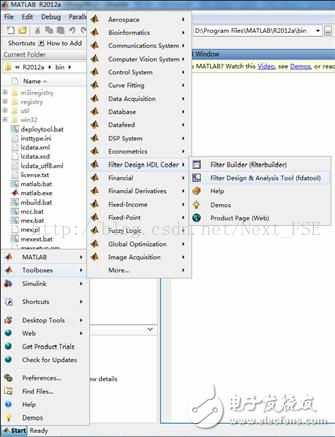

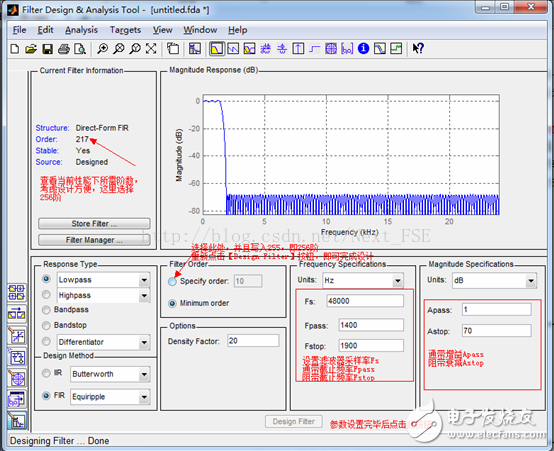

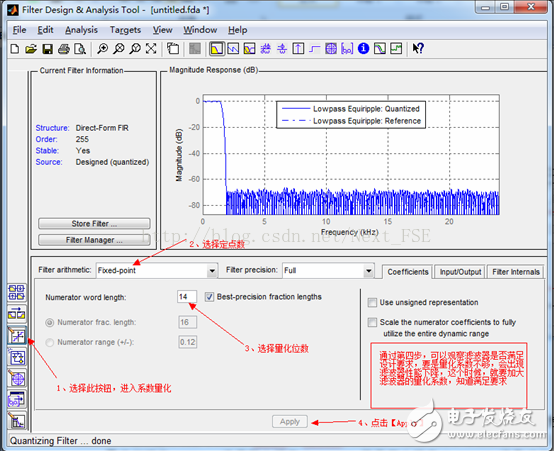

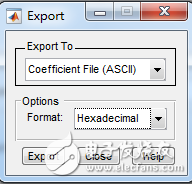

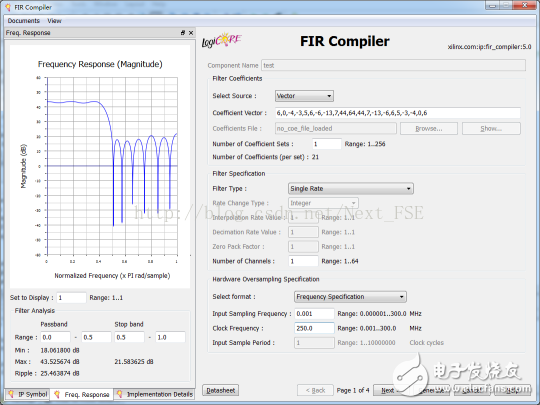

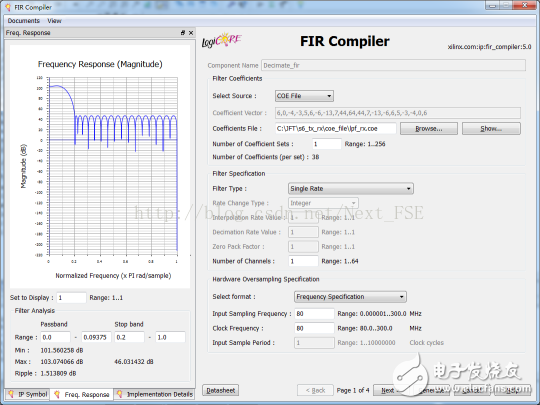

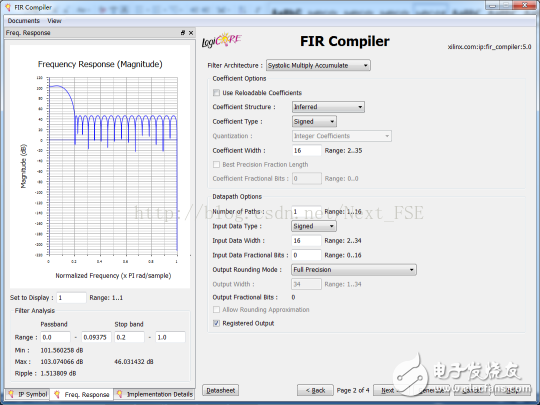

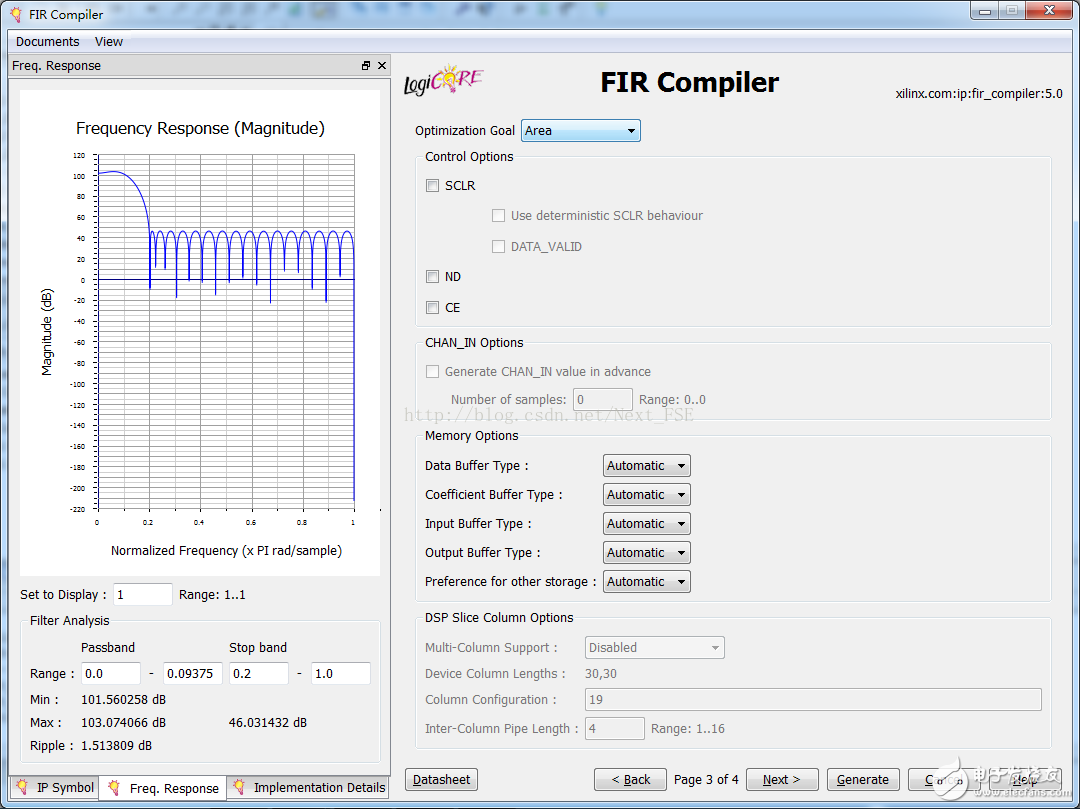

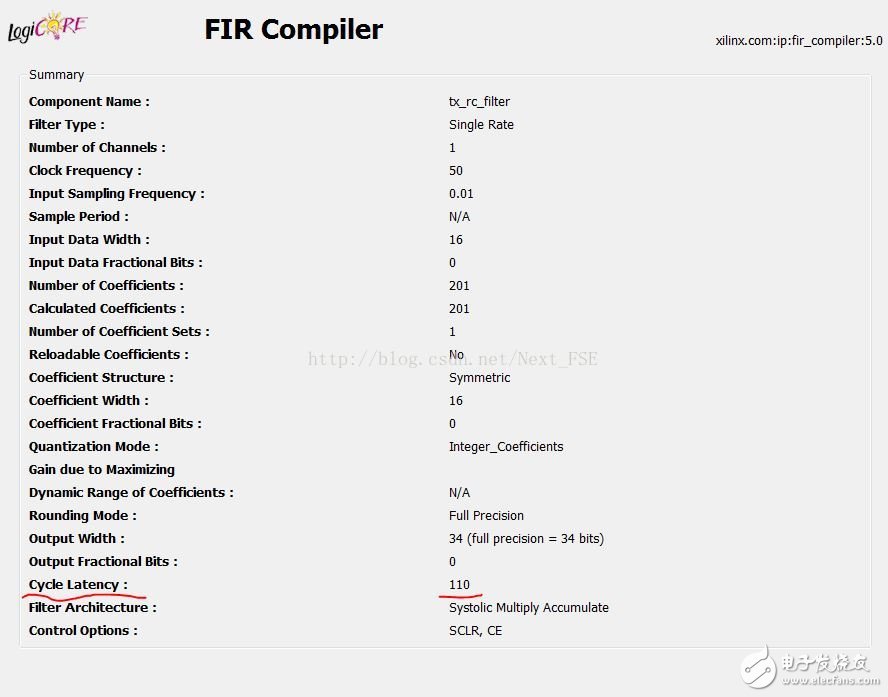

小弟現在需要一個帶通濾波器,大概設計方案是通過MATLAB的fdatool設計濾波器,生成濾波系數,再調用fpga的ip核,但是這樣占用fpga的太多資源,有沒有什么更好的方法來實現,或者是我的參數設置不對,貼出我的fir編譯器

2017-07-10 15:20:09

使用的是Vivado,希望使用其FIRIP核設計一個濾波器,該濾波器不是固定結構,而是可以根據項目中的變量filterselect的值選擇其通帶頻率,例如filterselect=0,1,2,3

2017-08-10 05:49:04

求解答怎么利用IP core設計收音機的FIR濾波器

2013-08-09 17:41:36

依次送入FIR濾波器IP核進行處理,輸出結果寫入fir_result.txt文本中。`timescale 1ns/1psmodule zstar_fir_sim();reg clk; reg [15

2020-01-14 09:39:45

如何去實現程控濾波器的設計?設計程控濾波器又有何作用?

2021-04-13 06:24:42

給響應帶來了損失。現有的視頻信號制式包括RGB、分量視頻、復合視頻和RGB PC圖像等。所有應用與制式都希望視頻濾波器能達到"線性相位",這是群延時(不同頻率的延時)特性所要

2021-05-14 07:55:00

我用MATLAB設計好單位增益的濾波器系數,然后導入 FIR 的IP核里面,系數轉換成定點數了,但是此時顯示的濾波器幅頻特性曲線卻是100dB的放大倍數,求問怎么讓其變成單位增益?

2018-01-27 13:53:00

帶通濾波器(BPF)被廣泛用于通帶非常窄、通帶以外任何其它頻率被衰減的應用。公式(1)是帶通濾波器的二階帶通傳輸函數:其中,K代表恒定的濾波器增益,Q代表濾波器的品質因數。

2019-06-24 07:23:07

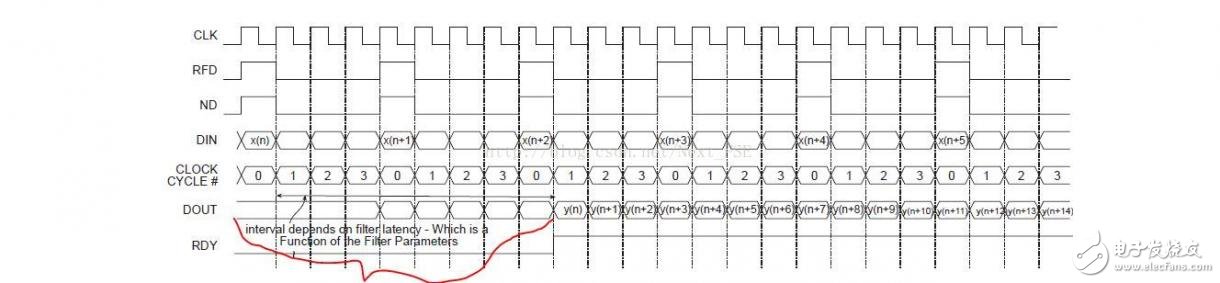

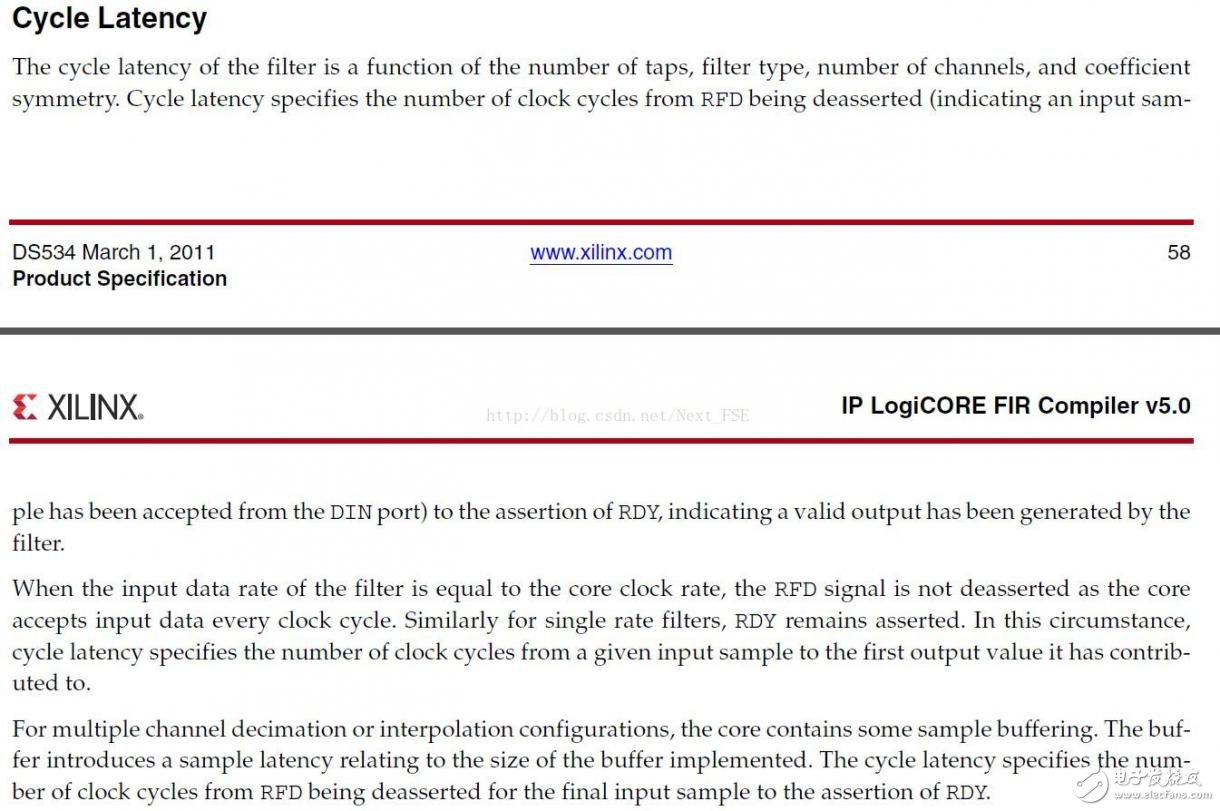

本人FPGA小白一枚,最近使用到FPGA的IP核遇到一個問題。比如說:某個IP,用于計算sin函數,使用了流水線機制,所有從輸入到輸出需要20個時鐘周期的延時。另外,還有一個IP,從輸入到輸出需要1

2021-06-19 11:06:07

請教大家誰用過 Xilinx PCIe IP 核啊?

2014-01-15 14:38:28

AD9361的FIR濾波器是否可以配置成RRC濾波器?只能用作低通濾波器嗎?另外,FIR濾波器的2/4倍插值是對原信號進行補0嗎?

2019-01-07 11:31:53

書籍共七章,首先概括介紹了有源濾波器的種類和結構特點,接著分開詳細介紹了巴特沃斯和切比雪夫低通濾波器,帶通濾波器,帶阻濾波器,全通和恒定延時濾波器的特點和實際的設計方法。本資料來自 世紀電影網 wkubae所發資料

2020-11-18 22:22:25

相同,濾波器階數為10。 圖1 可以發現轉置型結構不對輸入數據寄存,而是對乘累加后的結果寄存,這樣關鍵路徑上只有1個乘法和1個加法操作,相比于直接型結構,延時縮短了不少。 綜合得到結果

2019-06-28 08:22:02

頻率濾波器大概分為帶通、帶阻、高通、低通。特性不同的模擬濾波器中經典濾波器有Butterworth 和 Chebyshev 。其中,Butterworth 濾波器特點是通帶處幅值特性平坦,而 Chebyshev 濾波器則比前者的截至特性要好,但通帶處的幅值有振蕩。

2019-09-19 09:00:57

有源濾波器中數字低通濾波器的設計及其DSP實現摘要:介紹了基于瞬時無功功率理論的ip iq 諧波檢測方法及對低通濾波器的要求,分析討論了數字低通濾波器的類

2010-05-13 17:19:18 90

90 抗混迭濾波器,什么是抗混迭濾波器

背景知識:基本原理:抗混疊濾波器g(n)的輸入和輸出之間的卷積關系如下

2010-03-24 14:02:02 1287

1287 光濾波器,什么是光濾波器

基于干涉原理的濾波器:熔錐光纖濾波器、Fabry-Perot濾波器、多層介質膜濾波器、馬赫-曾德干涉濾波

2010-04-02 16:54:04 2190

2190 數字濾波器用于離散系統;模擬濾波器用于連續時間系統,也可以用在離散時間系統中,比如SC(開關電容)濾波器。 數字濾波器 由數字乘法器、加法器和延時單元組成的一種算法或裝置。

2012-03-30 14:11:39 4878

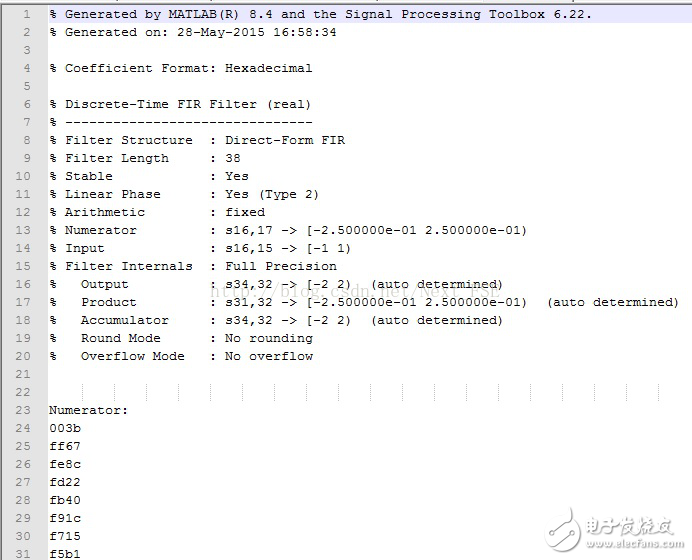

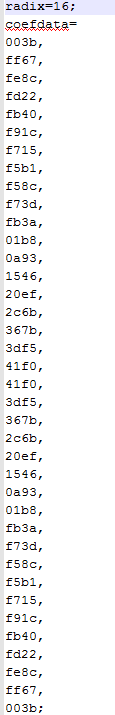

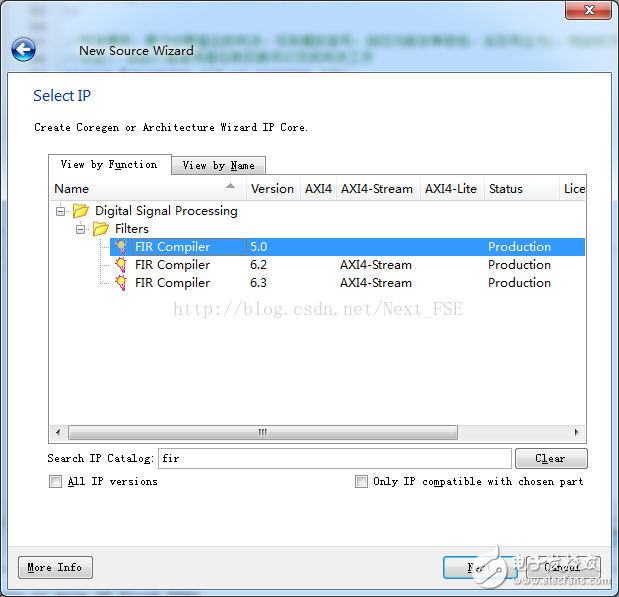

4878 Xilinx FIR IP的介紹與仿真 1 xilinx fir ip 簡介 1)符合 AXI4-Stream 的接口 2)高性能有限脈沖響應(FIR),多相抽取器,多相內插器,半帶,半帶抽取

2020-10-30 12:29:01 511

511

電子發燒友App

電子發燒友App

評論