-V+傳統(tǒng)芯片的案例越來(lái)越多,比如基于RISC-V實(shí)現(xiàn)高可靠性CPU,或者通過(guò)FPGA+RISC-V 實(shí)現(xiàn)一種創(chuàng)新設(shè)計(jì)。 ? 我們都知道,安路科技發(fā)布的FPSoC新品便是上述舉例中的后者。5月27日,國(guó)內(nèi)領(lǐng)先的FPGA芯片供應(yīng)商安路科技在官方微信中表示,精心打造的SF1系列FPSoC器件現(xiàn)已全面推出,

2022-08-02 08:01:00 4168

4168 FPGA 中已經(jīng)燒進(jìn)去了基于RISC-V 處理器(開(kāi)源CPU),怎么才能把編譯好de.elf文件加載到FPGA 中執(zhí)行,請(qǐng)各位大神幫我解答一下,感激不盡!

2017-06-21 19:30:45

與視頻處理培訓(xùn)發(fā)布時(shí)間:2009-1-6,來(lái)自 未名芯銳課程目標(biāo):1、深入了解JPEG標(biāo)準(zhǔn)和H.264標(biāo)準(zhǔn)協(xié)議;2、掌握FPGA在圖像與視頻方向設(shè)計(jì)的設(shè)計(jì)流程、方法及技巧。3、能夠?qū)崿F(xiàn)視頻處理中的重要模塊

2009-07-16 14:05:25

FPGA設(shè)計(jì)開(kāi)發(fā)問(wèn)題:設(shè)計(jì)要求種要求數(shù)據(jù)處理能力≥40M· samples/s 怎么理解?這是什么單位呀?根據(jù)這個(gè)單位怎么推算數(shù)據(jù)速率?有哪些接口能滿足此數(shù)據(jù)處理能力?序號(hào)指標(biāo)描述 1核心壓縮芯片

2017-08-01 15:27:17

顯示出來(lái),差分后的圖像不為零的即為目標(biāo)。在兩幀圖像中,灰度值沒(méi)有變化的部分被剪掉,主要是背景和一些小部分目標(biāo)。由檢出的部分大致可以確定運(yùn)動(dòng)目標(biāo)的位置,但是該方法的確定是當(dāng)物體的位移較小時(shí),難以確定目標(biāo)的運(yùn)動(dòng)

2020-12-26 15:57:01

來(lái)說(shuō),濾除噪聲、擴(kuò)展對(duì)比度、銳化以及色彩增強(qiáng)等處理能顯著提升視覺(jué)效果。這里設(shè)計(jì)一個(gè)基于FPGA的實(shí)時(shí)視頻圖像處理系統(tǒng),包含增強(qiáng)對(duì)比度擴(kuò)展和色飽和度兩種處理方法,相比于DSP和ASIC方案來(lái)說(shuō),FPGA在性能和靈活性方面具有絕對(duì)優(yōu)勢(shì),應(yīng)用FPGA設(shè)計(jì)視頻通信系統(tǒng)更普遍。

2019-08-22 08:22:29

設(shè)計(jì)RISC微處理器需要遵循哪些原則?基于FPGA技術(shù)用VHDL語(yǔ)言實(shí)現(xiàn)的8位RISC微處理器

2021-04-13 06:11:51

的核心知識(shí)在于驅(qū)動(dòng)和接口至CMOS圖像傳感器,動(dòng)態(tài)擴(kuò)展 和進(jìn)行信號(hào)預(yù)處理到TFT的領(lǐng)域。使用Helion系統(tǒng)意味著決定圖像質(zhì)量的很多功能可以直接在攝像機(jī)中實(shí)現(xiàn)。根據(jù)系統(tǒng)要求,這些解決方案基于 DSP,FPGA或兩者兼而有之。

2012-08-11 11:27:45

最近一段時(shí)間一直在研究基于FPGA的圖像處理,乘著這個(gè)機(jī)會(huì)和大家交流一下,自己也順便總結(jié)一下。主要是為了大家對(duì)用FPGA做圖像處理有個(gè)感性的認(rèn)識(shí),如果真要研究的話就得更加深入學(xué)習(xí)了。本人水平有限

2017-04-21 14:25:54

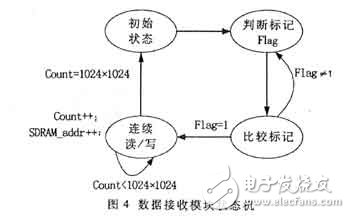

到的一幀圖像數(shù)據(jù)保存到 SRAM 中,此時(shí) DSP 在等待;第一次采樣結(jié)束后,DSP 與 FPGA 進(jìn)行總線切換,分別連接到與上次不同的 SRAM 上,DSP開(kāi)始讀取數(shù)據(jù),FPGA 開(kāi)始采集數(shù)據(jù)。每當(dāng) DSP 和 FPGA 都完成各自的任務(wù)時(shí),就進(jìn)行總線切換,交換連接的 SRAM。

2018-12-10 09:54:23

)。具體代碼查看vga_ctrl。· SDR SDRAM控制器本系統(tǒng)中的圖像模式為640X480,在SDRAM中存儲(chǔ)的方式設(shè)定為SDRAM每一行存儲(chǔ)160個(gè)像素點(diǎn),利用四行的存儲(chǔ)空間存儲(chǔ)一行的圖像信息

2023-03-24 19:29:11

2023 年 RISC-V 中國(guó)峰會(huì)上,倪光南院士表示,“RISC-V 的未來(lái)在中國(guó),而中國(guó)半導(dǎo)體芯片產(chǎn)業(yè)也需要 RISC-V,開(kāi)源的 RISC-V 已成為中國(guó)業(yè)界最受歡迎的芯片架構(gòu)”。大家怎么看呢?

2023-08-26 14:16:43

RISC-V會(huì)成為芯片主流嗎

2021-08-27 15:21:03

公開(kāi)了其在RISC-V方面的研究,指出了在深度神經(jīng)網(wǎng)絡(luò)中應(yīng)用RISC-V指令集的可能性;三星也披露了將推出多款采用RISC-V內(nèi)核架構(gòu)的芯片;另外,Google、三星和高通在內(nèi)的約80家公司將聯(lián)合

2021-06-18 20:57:35

(1)、芯片設(shè)計(jì)者可選擇RISC-V 核 和SoC 平臺(tái) 構(gòu)建自己的芯片。比如,使用 PULPino 平臺(tái)開(kāi)發(fā) SoC 芯片,內(nèi)核使用 RI5CY和Zero-risky,國(guó)內(nèi)企業(yè)和高校研究項(xiàng)目都有在

2023-06-21 20:34:16

RISC-V架構(gòu)秉承簡(jiǎn)單的設(shè)計(jì)哲學(xué)。體現(xiàn)為:在處理器領(lǐng)域,主流的架構(gòu)為x86與ARM架構(gòu)。x86與ARM架構(gòu)的發(fā)展的過(guò)程也伴隨了現(xiàn)代處理器架構(gòu)技術(shù)的不斷發(fā)展成熟,但作為商用的架構(gòu),為了能夠保持架構(gòu)的向后兼容性

2021-06-18 19:41:21

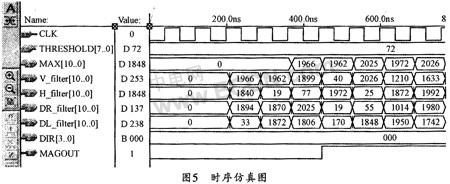

紅外圖像的自適應(yīng)分段線性拉伸,對(duì)FPGA芯片資源占用情況如表1所示。整個(gè)設(shè)計(jì)完全在FPGA中實(shí)現(xiàn),能最大限度地減少分立元件的使用。降低了系統(tǒng)的整體功耗,設(shè)計(jì)周期和開(kāi)發(fā)成本也就能隨之減少。算法完全采用

2012-04-27 14:37:03

在芯片設(shè)計(jì)中FPGA的優(yōu)勢(shì)是什么?基于FPGA的芯片設(shè)計(jì)方法及流程是怎樣的?

2021-05-10 07:06:05

,致力于為消費(fèi)電子、工控和AIoT中高量市場(chǎng)提供智能化的設(shè)計(jì)軟件和芯片系統(tǒng)。AGM創(chuàng)立于2010年,剛開(kāi)始致力于FPGA/CPLD的研發(fā)推廣,在LED 戶外屏驅(qū)動(dòng)市場(chǎng)占有大半壁江山后,于3年前切入

2024-01-02 15:58:32

、網(wǎng)絡(luò)通信和圖像顯示等其他操作。圖1.在FPGA協(xié)處理中,圖像使用CPU進(jìn)行采集后,通過(guò)DMA發(fā)送到FPGA,然后由FPGA對(duì)圖像進(jìn)行處理。在嵌入式FPGA處理架構(gòu)中,您可以將相機(jī)接口直接連接到FPGA

2018-08-03 11:13:19

在FPGA圖像處理中矩陣提取是個(gè)有趣的東東,本文僅限個(gè)人DIY,是否具有工程價(jià)值不做論述,權(quán)當(dāng)一樂(lè)。無(wú)處不在的line buffer現(xiàn)在FPGA圖像處理中,凡事?tīng)可娴骄仃囘\(yùn)算的算法里面基本都有l(wèi)ine

2022-07-15 14:51:07

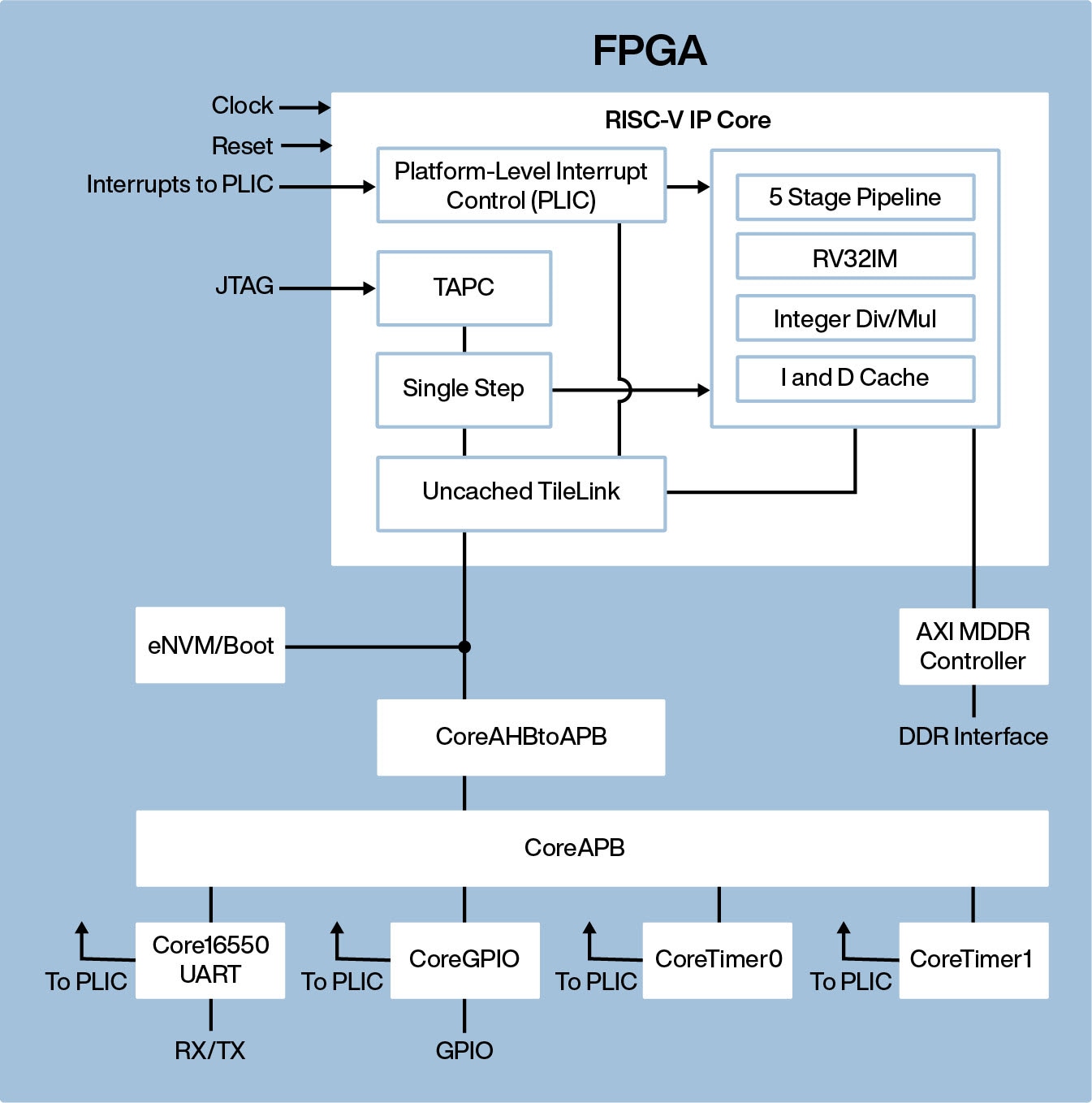

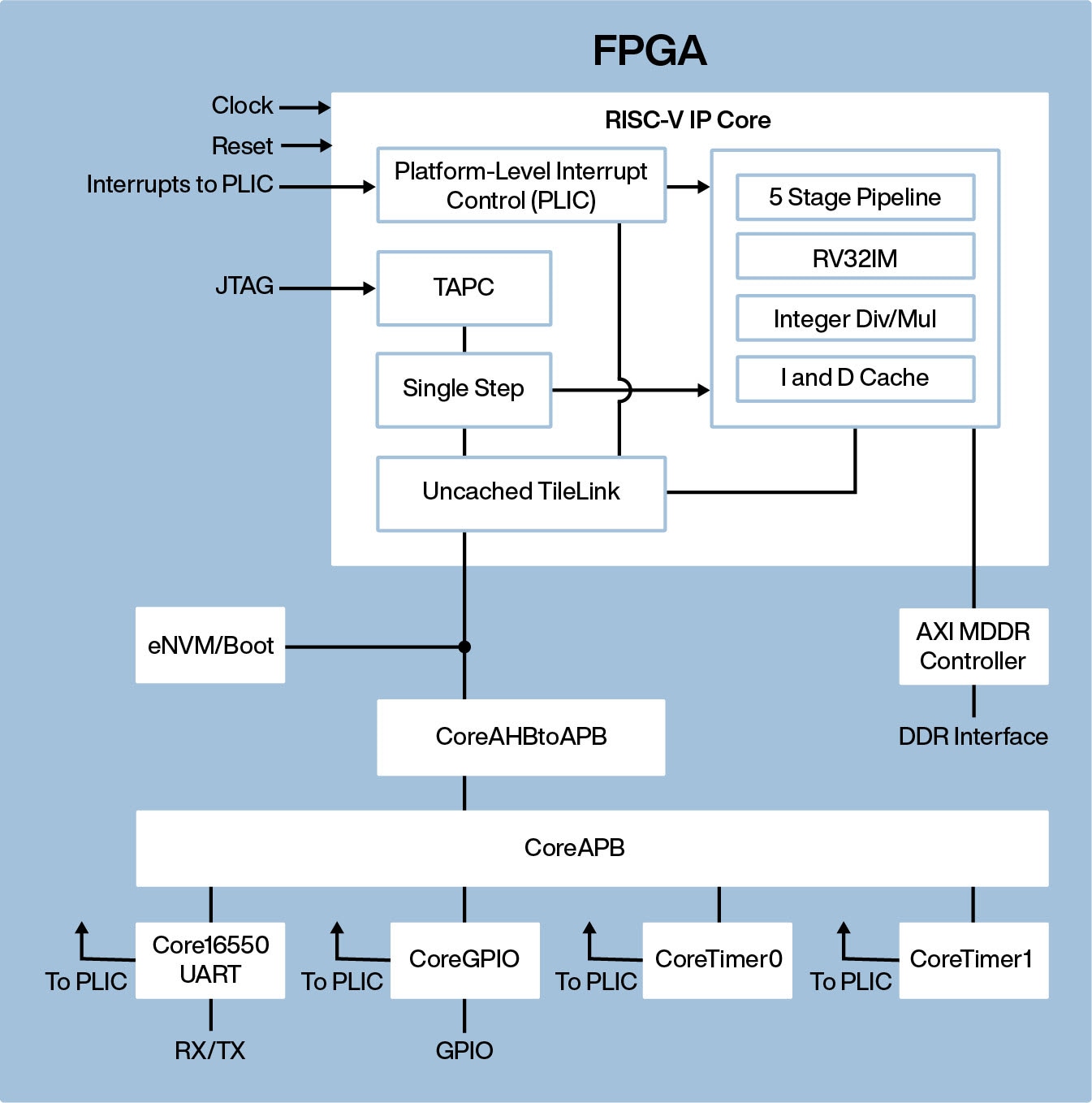

多個(gè) CPU 時(shí),可能是在高可靠性或高性能應(yīng)用中,PolarFire SoC FPGA 提供五個(gè)強(qiáng)化的 RISC-V 內(nèi)核。這種支持 Linux 的 SoC 具有跨內(nèi)核的一致內(nèi)存子系統(tǒng)和可配置的分支

2021-09-07 17:59:56

系統(tǒng)整體方案及硬件設(shè)計(jì) 系統(tǒng)要求在FPGA片內(nèi)利用SoPC技術(shù)實(shí)現(xiàn)便攜式的圖像采集與處理。它通過(guò)對(duì)原始圖像的掃描,經(jīng)數(shù)字圖像處理與識(shí)別后即可將得到的大容量的承載信息(包括文字、頭像、指紋等個(gè)人信息)在

2018-10-31 16:54:52

` 本項(xiàng)目利用MP801開(kāi)發(fā)板,通過(guò)攝像頭采集圖像數(shù)據(jù),然后在屏幕上顯示兩種圖像:屏幕有一個(gè)圓,圓內(nèi)顯示經(jīng)過(guò)了邊緣處理的圖像,而圓外則顯示原始圖像(效果如下圖)通過(guò)該工程的學(xué)習(xí),可以學(xué)到如下知識(shí):1

2019-11-29 09:52:21

項(xiàng)目名稱(chēng):基于FPGA的紅外激光圖像采集及顯示應(yīng)用領(lǐng)域:醫(yī)療,工業(yè)相機(jī),商業(yè)圖像處理參賽計(jì)劃:將FPGA作為主控芯片,控制CMOS傳感器攝取圖像,經(jīng)FIFO高速緩存輸出到激光器中。利用激光器將圖形

2021-05-12 18:02:40

數(shù)據(jù)到FPGA,FPGA會(huì)將接收到的數(shù)據(jù)實(shí)時(shí)存儲(chǔ)到AC6102開(kāi)發(fā)板上的DDR2存儲(chǔ)器中。另一邊,TFT驅(qū)動(dòng)邏輯會(huì)實(shí)時(shí)從DDR2中讀取圖像數(shù)據(jù)并顯示在TFT顯示屏上。整個(gè)系統(tǒng)的框圖如下圖所示(手繪草圖

2020-02-12 17:39:19

背景知識(shí) 在FPGA數(shù)字圖像處理中,行緩存的使用非常頻繁,例如我們需要圖像矩陣操作的時(shí)候就需要進(jìn)行緩存,例如圖像的均值濾波,中值濾波,高斯濾波以及sobel邊緣查找等都需要行緩存設(shè)計(jì)。這里的重要性

2020-02-17 19:32:54

。例如,如果工程師在FPGA中實(shí)現(xiàn)軟RISC-V內(nèi)核,則通常可以使用RTL源代碼。由于RISC-V免版稅,這為將基于RISC-V的設(shè)計(jì)從FPGA移植到ASIC或另一個(gè)FPGA帶來(lái)了極大的靈活性,而無(wú)

2020-07-27 17:38:30

主要負(fù)責(zé)一些接口邏輯 ,比如圖像的采集,圖像的顯示,圖像的存儲(chǔ)。還有FPGA和DSP之間的通信 。那我想問(wèn)一下 處理圖像應(yīng)該用什么系列的fpga 芯片從性能功耗價(jià)格方面綜合考慮,處理速度要快!!

2012-08-06 10:53:09

各位大蝦好,我現(xiàn)在正在做關(guān)于fpga的課題。想問(wèn)問(wèn)大家用fpga處圖像,圖片以怎么的方式輸入fpga再進(jìn)行處理。

2013-04-12 11:00:17

反熔絲FPGA在密碼芯片設(shè)計(jì)中的運(yùn)用

2012-08-17 10:37:41

國(guó)產(chǎn)RISC-V芯片這個(gè)俱樂(lè)部中,已經(jīng)聚集了哪些玩家呢? 平頭哥(中天微) 平頭哥半導(dǎo)體公司是由阿里巴巴全資收購(gòu)的杭州中天微和阿里達(dá)摩院合并而成,主要發(fā)力于32位高性能和低功耗嵌入式CPU的IC

2020-08-02 11:56:07

摘 要

針 對(duì) 圖 像 傳 輸 過(guò) 程 中 的 多 路 徑 、非 通 視 和 高 速 移 動(dòng) 等 特 點(diǎn) ,提 出 了 一 種 FPGA+ W5300 架 構(gòu) 的C0FDM 無(wú) 線 圖像 傳 輸

2023-11-07 11:33:53

基于FPGA和視頻解碼芯片的實(shí)時(shí)圖像采集系統(tǒng)設(shè)計(jì)

2017-12-26 16:51:49

基于FPGA和視頻解碼芯片的實(shí)時(shí)圖像采集系統(tǒng)設(shè)計(jì),介紹了CCD圖像傳感器和ADV7181B解碼芯片的I2C配置原理。給出了乒乓緩存的原理與實(shí)現(xiàn)方法,同時(shí)給出了ADV7181B與FPGA等芯片組成視頻處理電路的設(shè)計(jì)和FPGA的程序?qū)崿F(xiàn)方法。

2017-11-17 13:59:48

數(shù)據(jù)流,FPGA通過(guò)對(duì)其同步信號(hào),如時(shí)鐘、行頻和場(chǎng)頻進(jìn)行檢測(cè),從而從數(shù)據(jù)總線上實(shí)時(shí)的采集圖像數(shù)據(jù)。MT9V034攝像頭默認(rèn)初始化數(shù)據(jù)就能輸出正常的視頻流,因此FPGA中實(shí)際上未作任何IIC初始化配置。在FPGA

2019-07-05 13:51:50

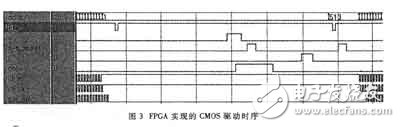

對(duì)CMOS Sensor進(jìn)行寄存器初始化配置。這些初始化的基本參數(shù),即初始化地址對(duì)應(yīng)的初始化數(shù)據(jù)都存儲(chǔ)在一個(gè)預(yù)先配置好的FPGA片內(nèi)ROM中。在初始化配置完成后,CMOS Sensor就能夠持續(xù)輸出標(biāo)準(zhǔn)

2019-07-10 09:12:31

對(duì)CMOS Sensor進(jìn)行寄存器初始化配置。這些初始化的基本參數(shù),即初始化地址對(duì)應(yīng)的初始化數(shù)據(jù)都存儲(chǔ)在一個(gè)預(yù)先配置好的FPGA片內(nèi)ROM中。在初始化配置完成后,CMOS Sensor就能夠持續(xù)輸出標(biāo)準(zhǔn)

2019-07-08 18:15:47

對(duì)CMOSSensor進(jìn)行寄存器初始化配置。這些初始化的基本參數(shù),即初始化地址對(duì)應(yīng)的初始化數(shù)據(jù)都存儲(chǔ)在一個(gè)預(yù)先配置好的FPGA片內(nèi)ROM中。在初始化配置完成后,CMOS Sensor就能夠持續(xù)輸出標(biāo)準(zhǔn)RGB

2019-07-14 17:26:36

顯示在液晶屏的右側(cè)。測(cè)試腳本中,根據(jù)lcd_driver.v模塊的顯示驅(qū)動(dòng)信號(hào),將一幀的顯示圖像寫(xiě)入到monitor_display_image.txt文本中(仿真測(cè)試結(jié)果

2019-07-12 17:33:07

結(jié)構(gòu),即在內(nèi)存中開(kāi)辟一個(gè)整數(shù)數(shù)組來(lái)進(jìn)行計(jì)數(shù),但是在FPGA 中定義數(shù)組是非常消耗資源的,尤其是當(dāng)數(shù)組成員的位寬很大時(shí)。例如用觸發(fā)器來(lái)統(tǒng)計(jì)256 灰度的720p 圖像的直方圖,將消耗4000 個(gè)邏輯單元

2012-05-14 12:37:37

,也就是說(shuō),圖像中的任何像素不是0就是1,再無(wú)其他過(guò)渡的灰度值。二值圖像經(jīng)常出現(xiàn)在數(shù)字圖像處理中作為圖像掩碼或者在圖像分割、二值化和dithering的結(jié)果中出現(xiàn)。一些輸入輸出設(shè)備,如激光打印機(jī)

2018-08-14 09:08:57

、 廣播、汽車(chē)電子、工業(yè)、消費(fèi)類(lèi)市場(chǎng)、測(cè)量測(cè)試等多個(gè)熱門(mén)領(lǐng)域。2008年北京奧運(yùn)會(huì)的主舞臺(tái)中——畫(huà)卷就用到了4000個(gè)FPGA芯片,這是FPGA在圖像領(lǐng)域中的應(yīng)用;FPGA在人臉、車(chē)牌等物體檢測(cè)中得到

2023-06-21 18:47:51

為了實(shí)現(xiàn)—是彈武器瞄準(zhǔn)自動(dòng)化,本文設(shè)計(jì)了基于DSP和FPGA的高速高精確度雙通道CCD圖像采集系統(tǒng),采用QUartuBn在AJtera的FPGA器件CYCLONEII上設(shè)計(jì)了CCD驅(qū)動(dòng)時(shí)序電路,采用

2014-11-07 14:54:07

,7670可以說(shuō)是最基礎(chǔ)的攝像頭,基礎(chǔ)到你都不想學(xué)驅(qū)動(dòng)它,因?yàn)楫?huà)質(zhì)很差,還有一款基礎(chǔ)的攝像頭是OV7725,也是30w像素和7670比起來(lái),差別咋就這么大呢(看價(jià)格就明白了)。 完整文檔下載: 基于Xilinx FPGA的視頻圖像采集系統(tǒng).pdf

2018-07-03 10:56:57

,7670可以說(shuō)是最基礎(chǔ)的攝像頭,基礎(chǔ)到你都不想學(xué)驅(qū)動(dòng)它,因?yàn)楫?huà)質(zhì)很差,還有一款基礎(chǔ)的攝像頭是OV7725,也是30w像素和7670比起來(lái),差別咋就這么大呢(看價(jià)格就明白了)。 完整文檔下載: 基于Xilinx FPGA的視頻圖像采集系統(tǒng).pdf

2018-07-09 09:31:05

基于專(zhuān)用單片機(jī)來(lái)實(shí)現(xiàn)(一般稱(chēng)為可編程DSP單片機(jī))以及在VLSI上實(shí)現(xiàn)某種算法的專(zhuān)用集成電路芯片(ASIC)等。近年來(lái),隨著EDA技術(shù)的迅速發(fā)展,國(guó)內(nèi)外逐漸比較流行的是在FPGA中實(shí)現(xiàn)復(fù)雜算法的運(yùn)算處理。在

2019-07-31 06:38:07

大家好,我有FPGA virtext -5 ML510板,我想將圖像存儲(chǔ)在DD RAM中,我聲明一個(gè)數(shù)組,并希望存儲(chǔ)在DD RAM的基地址中,如果有人可以幫助我,那么使用Xilinx SDK 11從RAM寫(xiě)入和讀取圖像數(shù)據(jù)的過(guò)程是什么。

2020-06-03 12:03:38

主要負(fù)責(zé)一些接口邏輯 ,比如圖像的采集,圖像的顯示,圖像的存儲(chǔ)。還有FPGA和DSP之間的通信 。那我想問(wèn)一下 處理圖像應(yīng)該用什么系列的fpga芯片從性能功耗價(jià)格方面綜合考慮,處理速度要快!!

2012-08-06 10:54:12

數(shù)碼相機(jī)用途的高級(jí)圖像處理大規(guī)模集成電路Milbeaut家族中的新成員,該產(chǎn)品家族中旗艦型號(hào)為MB91680。該款全新芯片可以確保照相機(jī)在功耗極小的條件下實(shí)時(shí)處理高清晰,高質(zhì)量的圖像。 富士通

2018-10-26 16:53:52

設(shè)計(jì)。FPGA-ARM架構(gòu)是經(jīng)常用的一種架構(gòu)。通常ARM用作核心處理芯片,相當(dāng)于人的大腦,而FPGA作為底層實(shí)踐、實(shí)現(xiàn)者,完成大部分電路驅(qū)動(dòng)和數(shù)據(jù)采集處理,做一個(gè)不恰當(dāng)?shù)谋扔鳎?b class="flag-6" style="color: red">FPGA相當(dāng)于人的四肢。在設(shè)計(jì)中,通常要

2019-12-10 17:58:16

今天給大俠帶來(lái)基于FPGA的實(shí)時(shí)圖像邊緣檢測(cè)系統(tǒng)設(shè)計(jì),由于篇幅較長(zhǎng),分三篇。今天帶來(lái)第二篇,中篇,話不多說(shuō),上貨。導(dǎo)讀隨著科學(xué)技術(shù)的高速發(fā)展,FPGA在系統(tǒng)結(jié)構(gòu)上為數(shù)字圖像處理帶來(lái)了新的契機(jī)。圖像中

2021-07-28 06:06:26

RISC-V的出現(xiàn),或許有機(jī)會(huì)出現(xiàn)一些變數(shù)?近日,Sipeed在社交平臺(tái)上發(fā)布了一個(gè)64位RISC-V (RV64)芯片平臺(tái)運(yùn)行Android 10系統(tǒng)的視頻,并表示搭載64位RISC-V芯片的手機(jī)將于明年

2021-12-17 08:00:00

請(qǐng)幫幫我。我無(wú)法在FPGA中創(chuàng)建可用信號(hào)。(引腳FPGA中的網(wǎng)關(guān)輸出)顯示錯(cuò)誤。焊盤(pán)位置的數(shù)量必須與驅(qū)動(dòng)該網(wǎng)關(guān)輸出的信號(hào)的位數(shù)相匹配。格式必須指定為單元格數(shù)組,例如{'MSB',...,'LSB

2019-09-10 12:44:58

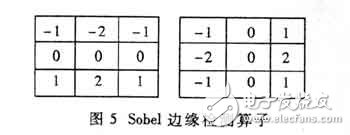

先用一個(gè)3x3的算子進(jìn)行濾波,再用一個(gè)3x3的算子進(jìn)行取邊緣,在FPGA流水線算法中,濾波處理完了數(shù)據(jù)立即就會(huì)進(jìn)行取邊緣處理,是不需要像CPU那樣存回內(nèi)存再讀出來(lái)的。

FPGA進(jìn)行圖像處理的前景

2023-06-08 15:55:34

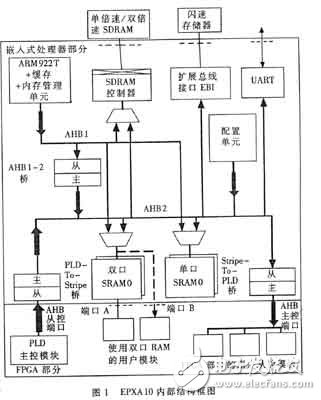

隨著亞微米技術(shù)的發(fā)展,FPGA芯片密度不斷增加,并以強(qiáng)大的并行計(jì)算能力和方便靈活的動(dòng)態(tài)可重構(gòu)性,被廣泛地應(yīng)用于各個(gè)領(lǐng)域。但是在復(fù)雜算法的實(shí)現(xiàn)上,FPGA卻遠(yuǎn)沒(méi)有32位RISC處理器靈活方便,所以在

2019-07-08 07:40:22

在labview中用IMAQ打開(kāi)圖像后,怎么在圖像中畫(huà)圓?而且是用圓心加半徑的方法。我用draw circle by radius函數(shù)時(shí),連不上圖像。比如在這個(gè)圖像中畫(huà)圓

2017-04-19 16:55:03

本帖最后由 upmcu 于 2012-7-28 15:07 編輯

截圖:FPGA控制實(shí)現(xiàn)圖像系統(tǒng)視頻圖像采集.pdfFPGA在多制式視頻轉(zhuǎn)換系統(tǒng)中的應(yīng)用.pdfFPGA在圖象處理中

2012-07-28 14:28:52

提供視頻數(shù)據(jù)的模擬通道,共同匯集到DVI-I輸出接口,傳送到數(shù)字顯示器或模擬顯示器上顯示。 圖2 硬件構(gòu)架框圖輸出圖像的分辨率要求FPGA與TMDS發(fā)送芯片之間傳送數(shù)據(jù)的帶寬在100M(像素/秒)以上

2019-04-22 07:00:11

-V 設(shè)計(jì)而開(kāi)發(fā)的一個(gè)不斷擴(kuò)展、全面的工具套件和設(shè)計(jì)資源。Microchip FPGA業(yè)務(wù)部副總裁 Bruce Weyer表示:“隨著 RISC-V 軟件和硅芯片在市場(chǎng)上的廣泛應(yīng)用,Microchip 正在

2021-03-09 19:48:43

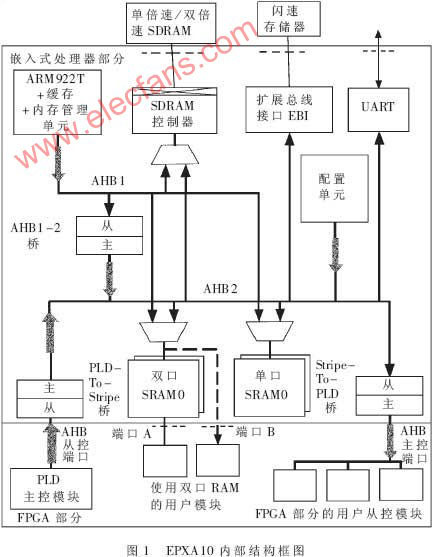

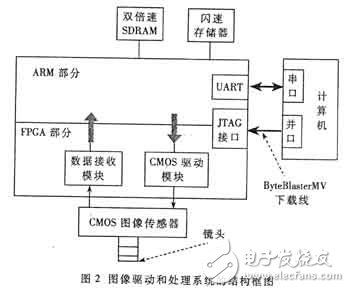

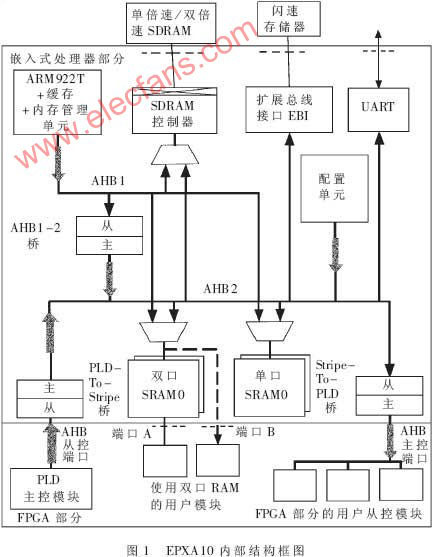

????內(nèi)嵌ARM核的FPGA芯片EPXA10及其在圖像驅(qū)動(dòng)和處理方面的應(yīng)用 ????

2006-04-16 23:33:07 1148

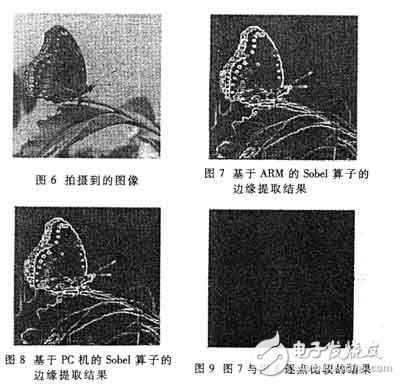

1148 基于FPGA的圖像邊緣檢測(cè)

引言

圖像邊緣檢測(cè)是圖像處理的一項(xiàng)基本技術(shù),在工業(yè)、醫(yī)學(xué)、航天和軍事等領(lǐng)域有著廣泛的應(yīng)用。圖像處理的速度一直是一

2010-01-14 11:07:57 1714

1714

?????????本文所介紹的圖像驅(qū)動(dòng)和處理系統(tǒng)正是應(yīng)用了EPXA10的這些特點(diǎn),充分發(fā)揮了FPGA邏輯控制實(shí)現(xiàn)簡(jiǎn)單、對(duì)大量數(shù)據(jù)做簡(jiǎn)單處理速度快的優(yōu)勢(shì)以

2010-07-10 11:37:49 818

818

捅要:為了實(shí)現(xiàn)是彈武器瞄準(zhǔn)自動(dòng)化,本文設(shè)計(jì)了基于DSP和FPGA的高速高精確度雙通道CCD圖像采集系統(tǒng),采用QUartuBn在AJtera的FPGA器件CYCLONEII上設(shè)計(jì)了CCD驅(qū)動(dòng)時(shí)序電路,采用PsPICE設(shè)計(jì)了可以

2011-02-25 13:48:05 187

187 本文設(shè)計(jì)了基于FPGA的LCoS驅(qū)動(dòng)代碼及圖像的FFT變換系統(tǒng),為計(jì)算全息三維顯示圖像處理和顯示提供了硬件平臺(tái)

2011-06-28 09:36:46 1824

1824

本文將實(shí)現(xiàn)基于FPGA的圖像二維5/3提升小波變換,采用FPGA芯片實(shí)現(xiàn)計(jì)算量十分復(fù)雜的二維提升小波變換,可以大大提高圖像壓縮運(yùn)算速度,保證系統(tǒng)的實(shí)時(shí)性要求。

2011-06-29 11:59:28 3299

3299

ECT圖像重建算法的FPGA實(shí)現(xiàn)

ECT圖像重建算法的FPGA實(shí)現(xiàn)

2015-11-19 14:59:41 1

1 本文在研究紅外焦平面陣列非均勻性的特點(diǎn)和成因后,首先設(shè)計(jì)了紅外圖像實(shí)時(shí)處理的硬件平臺(tái)。本硬件平臺(tái)以FPGA為核心處理器,外圍芯片主要有存儲(chǔ)器和D/A等。該平臺(tái)為紅外探測(cè)器提供驅(qū)動(dòng)信號(hào),實(shí)現(xiàn)圖像算法。

2016-05-17 14:29:59 5

5 基于FPGA的CMOS圖像感器IA_G3驅(qū)動(dòng)電路的研究

2016-08-29 16:05:01 15

15 基于FPGA的多幅圖像融合疊加的設(shè)計(jì)與實(shí)現(xiàn)

2016-08-30 15:10:14 11

11 基于FPGA的圖像數(shù)據(jù)采集卡及其驅(qū)動(dòng)設(shè)計(jì)

2016-08-29 23:22:35 24

24 基于FPGA的圖像字符疊加器設(shè)計(jì),下來(lái)看看

2016-08-29 23:23:30 17

17 FPGA圖像處理

2016-12-14 22:29:34 17

17 Jan Gray是在FPGA中集成32位RISC處理器的專(zhuān)家,他寫(xiě)了一篇博客叫作FPGA CPU 新聞,副標(biāo)題為 “使用FPGA開(kāi)發(fā)并行計(jì)算機(jī)體系架構(gòu)”。

2017-02-10 08:55:03 1898

1898

32位RISC CPU ARM芯片的應(yīng)用與選型

2017-09-25 08:33:48 13

13 本文結(jié)合實(shí)際系統(tǒng)中的前端圖像處理和圖像數(shù)據(jù)傳輸需要.充分利用ARM的靈活 性和FPGA的并行性特點(diǎn),設(shè)計(jì)了一種基于ARM+FPGA的圖像快速采集傳輸系統(tǒng)。所選的ARM體系結(jié)構(gòu)是32位嵌入式RISC

2017-11-24 09:23:21 3937

3937

FPGA仿真篇-使用腳本命令來(lái)加速仿真二 基于FPGA的HDMI高清顯示借口驅(qū)動(dòng) 基于FPGA灰度圖像高斯濾波算法的實(shí)現(xiàn) FPGA為什么比CPU和GPU快 基于Xilinx FPGA的視頻圖像采集

2018-02-20 20:44:00 1256

1256

FPGA仿真篇-使用腳本命令來(lái)加速仿真二 基于FPGA的HDMI高清顯示借口驅(qū)動(dòng) 基于FPGA灰度圖像高斯濾波算法的實(shí)現(xiàn) FPGA為什么比CPU和GPU快 基于Xilinx FPGA的視頻圖像采集

2018-02-20 20:49:00 7272

7272

FPGA圖像處理之路,從此開(kāi)始,接下來(lái),讓我們把時(shí)間交給“圖像處理”。一休哥在動(dòng)筆之前,一直在猶豫,反復(fù)思考著一個(gè)問(wèn)題,這個(gè)問(wèn)題一直困擾著我,“FPGA在圖像處理領(lǐng)域中的地位?”

2018-05-09 17:05:00 3953

3953 關(guān)鍵詞:RISC-V , 晶心 , 高云 晶心科技宣布其RISC-V CPU處理器核心獲高云半導(dǎo)體用于Arora GW-2A FPGA系列產(chǎn)品。晶心的RISC-V CPU除了標(biāo)準(zhǔn)的RISC

2018-10-08 14:34:01 441

441 高云半導(dǎo)體FPGA應(yīng)用研發(fā)總監(jiān)高彤軍作了題為“基于RISC-V微處理器的FPGA解決方案”的專(zhuān)題演講,高云半導(dǎo)體北美銷(xiāo)售總監(jiān)Scott Casper參加了主旨為“準(zhǔn)備好用RISC-V做設(shè)計(jì)了嗎?”的主題論壇,會(huì)議現(xiàn)場(chǎng),高云半導(dǎo)體與會(huì)人員演示了內(nèi)嵌RISC-V核的視頻顯示系統(tǒng)。

2018-11-17 09:30:43 8224

8224 RISC-V的發(fā)展速度比我預(yù)期的要快得多。我認(rèn)為這將給FPGA帶來(lái)一個(gè)巨大的機(jī)會(huì),使其可以更多地蠶食ASIC和ASSP。大多數(shù)SoC在通往ASIC的路上都要使用到FPGA,首先使用基于FPGA的仿真

2020-06-09 15:34:54 3709

3709 介紹一種用于印制電路板孔徑孔數(shù)檢測(cè)機(jī)的新的基于FPGA 的超長(zhǎng)CIS 圖像采集系統(tǒng),該系統(tǒng)由三個(gè)CIS(接觸式圖像傳感),兩個(gè)A/D(數(shù)/模)轉(zhuǎn)換芯片,一片XC866 單片機(jī)以及一片

2021-01-26 15:57:00 10

10 可編程門(mén)陣列(FPGA)作為載體,使用VHDL語(yǔ)言對(duì)驅(qū)動(dòng)時(shí)序發(fā)生器進(jìn)行了硬件描述。采用Quartus II 7.1軟件對(duì)所做的設(shè)計(jì)進(jìn)行功能仿真后.將程序燒寫(xiě)入FPGA(ALTERA公司的EP2C20F484C8)內(nèi),對(duì)IA._G3圖像傳感器進(jìn)行配置,實(shí)驗(yàn)結(jié)果表明,上述電路滿足CMOS相機(jī)的驅(qū)動(dòng)要求。

2021-01-29 16:51:40 14

14 基于小波變換的濾波方法應(yīng)用于紅外圖像處理中可以在降低噪聲的同時(shí)提升圖像細(xì)節(jié),有效改善圖像畫(huà)質(zhì)。介紹了一種采用FPGA的小波圖像處理方法及其硬件處理架構(gòu)。通過(guò)合理有效地進(jìn)行算法硬件設(shè)計(jì),在單片FPGA芯片上實(shí)現(xiàn)了圖像的實(shí)時(shí)處理,有利于紅外機(jī)芯的小型化。

2021-02-01 14:54:00 5

5 為了解決圖像掃描設(shè)備與主機(jī)之間海量數(shù)據(jù)高速傳輸問(wèn)題,提出了一種基于FPGA的圖像數(shù)據(jù)采集卡的設(shè)計(jì)方法。該設(shè)計(jì)方法對(duì)采集卡的原理設(shè)計(jì)、FPGA的開(kāi)發(fā)以及驅(qū)動(dòng)程序的實(shí)現(xiàn)進(jìn)行了研究;板卡采用

2021-02-03 16:26:11 18

18 在FPGA圖像采集系統(tǒng)的基礎(chǔ)上,設(shè)計(jì)了一種遙控式且?guī)Т鎯?chǔ)功能的圖像采集系統(tǒng)。設(shè)計(jì)采用MT9T001作為圖像傳感器,以FPGA芯片EP2C8Q208和AVR單片機(jī) Atmega8L的組合

2021-03-19 16:30:06 0

0 討論研究了一個(gè)滿足200Hz幀頻的128*128點(diǎn)陣圖像電阻陣驅(qū)動(dòng)控制器的設(shè)計(jì)方案。采用嵌入式計(jì)算機(jī)和FPGA相結(jié)合的構(gòu)架,充分利用100M以太網(wǎng)技術(shù)、乒乓緩沖技術(shù)、硬件查表技術(shù),解決了圖像數(shù)據(jù)的高速穩(wěn)定傳輸?shù)膯?wèn)題,采用高速串行DA技術(shù)解決了200Hz幀頻的128路行驅(qū)動(dòng)信號(hào)生成問(wèn)題。

2021-04-01 14:14:48 12

12 電子發(fā)燒友網(wǎng)站提供《使用FPGA創(chuàng)建RISC V系統(tǒng).zip》資料免費(fèi)下載

2022-11-08 10:26:45 1

1 Microchip FPGA 和基于 SoC 的 RISC-V 生態(tài)系統(tǒng)簡(jiǎn)介

2022-12-28 09:51:19 1475

1475

的靈活性和FPGA的并行性的特點(diǎn),設(shè)計(jì)了一種基于ARM+FPGA的高速圖像數(shù)據(jù)采集傳輸系統(tǒng)。所選用的ARM體系結(jié)構(gòu)是32位嵌入式RISC微處理器結(jié)構(gòu),該微處理器擁有豐富的指令集且編程靈活;而FPGA則在速度和并行運(yùn)算方面有很大優(yōu)勢(shì),適合圖像處理的實(shí)時(shí)性要求

2023-09-27 10:45:02 784

784 RISC-V IP供貨商Andes晶心科技(TWSE:6533)與邊緣運(yùn)算芯片供貨商元視芯智能科技共同宣布,元視芯 MAT系列作為全球首次采用RISC-V IP SoC的車(chē)規(guī)級(jí)CMOS圖像傳感器系列芯片產(chǎn)品

2024-02-22 10:55:53 288

288

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論