通用異步收發(fā)器(UART, Universa lA synchronousRece iver Transm itter)是一種應(yīng)用廣泛的短距離串行傳輸接口, 具有傳輸線少、成本低、可靠性高等優(yōu)點。 8250、8251等都是常見的UART 接口芯片, 但專用芯片一般引腳較多, 內(nèi)含許多輔助模塊和一些輔助功能, 在實際使用時往往用不到這些功能, 基本的UART 通信只需要接收和發(fā)送兩條信號線, 接收與發(fā)送是全雙工形式, 因此若采用UART 專用芯片, 將會使電路變得復(fù)雜, PCB面積增大, 從而導(dǎo)致成本增加, 系統(tǒng)的穩(wěn)定性和可靠性降低。 由于FPGA 的功能日益強大, 開發(fā)周期短、可重復(fù)編程等優(yōu)點也越來越明顯, 可以在FPGA 芯片上集成UART 功能模塊, 從而簡化電路, 縮小PCB 面積, 提高系統(tǒng)可靠性。 此外, 基于FPGA 的設(shè)計具有很高的靈活性, 可以方便地進行升級和移植。

1、 UART 控制器的FPGA實現(xiàn)

異步收發(fā)器的頂層模塊由波特率發(fā)生器、UART 接收器和UART發(fā)送器構(gòu)成。 UART 發(fā)送器的用途是將準備輸出的并行數(shù)據(jù)按照基本UART 幀格式轉(zhuǎn)為TXD 信號串行輸出; UART 接收器接收RXD 串行信號, 并將其轉(zhuǎn)化為并行數(shù)據(jù), 但串并轉(zhuǎn)換的時鐘同發(fā)送器一樣處理, 收發(fā)設(shè)備間的時鐘是會累計的, 會導(dǎo)致接收數(shù)據(jù)不正確, 波特率發(fā)生器就是專門產(chǎn)生一個遠遠高于波特率的本地時鐘信號對輸入RXD 不斷采樣, 以不斷地讓接收器與發(fā)送器保持同步。

本設(shè)計主要分為波特率發(fā)生器模塊、發(fā)送模塊和接收模塊, 采用的芯片為康欣公司的KX _7C5系列芯片, 其具體型號為EP2C5T144, 具備4608個邏輯宏單元、兩個鎖相環(huán), 約20萬門、約12萬RAM bi.t 具體實現(xiàn)方法如下:

1. 1、波特率控制器

波特率控制可有多種方法實現(xiàn), 常用計數(shù)器分頻, 或利用片內(nèi)鎖相環(huán)控制, 分頻較為簡單, 但對輸入頻率有要求, 分頻后的頻率必須在該波特率下頻率偏差允許范圍內(nèi), 設(shè)定較好的輸入頻率值, 可解決此問題,這樣可較少消耗片內(nèi)資源, 鎖相環(huán)技術(shù)雖然對輸入頻率沒有過高要求, 但定制內(nèi)部鎖相環(huán), 必然耗費較多的片內(nèi)資源, 本設(shè)計出于對片內(nèi)資源的考慮, 采用了分頻方法實現(xiàn)波特率控制器。 波特率發(fā)生器實際是一個頻率變換器。 可以根據(jù)給定的系統(tǒng)時鐘和要求的波特率, 通過內(nèi)部的分頻或倍頻, 最終得到適宜雙方通信的一個時鐘頻率。 發(fā)送器和接收器以該頻率為基準, 進行發(fā)送和采樣接收。

1. 2、接收器

由于串行數(shù)據(jù)幀和接收時鐘是異步的, 由邏輯1轉(zhuǎn)為邏輯0可以被視為一個數(shù)據(jù)幀的起始位。 然而為了避免毛刺影響, 能夠得到正確的起始為信號, 必須要求接收到的起始位在波特率采樣過程中至少有一半是屬于邏輯0才可以認定接收到的是起始位。 由于內(nèi)部采樣時鐘是發(fā)送和接收時鐘頻率的16倍, 所以起始位至少有8個連續(xù)采樣時鐘周期的邏輯0被收到, 才認為起始位接收到, 接著數(shù)據(jù)位和奇偶校驗位將每隔16個采樣時鐘周期被采樣一次(即每一個波特率時鐘采樣一次)。 如果起始位的確是16個采樣時鐘周期, 那么接下來數(shù)據(jù)在每位中點處被采樣, 采得的數(shù)據(jù)進行移位寄存, 當一幀接收完, 把移位接收寄存器中的內(nèi)容放入接收緩沖寄存器, 同時產(chǎn)生接收完一幀的標志信號。

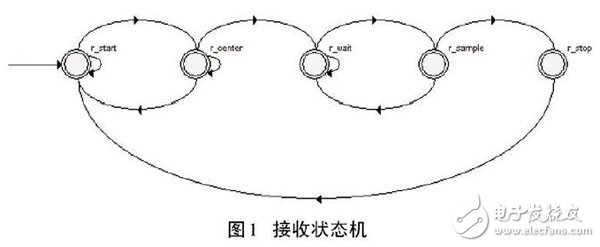

基于UART 的實現(xiàn)原理和通信協(xié)議, 本設(shè)計采用圖1的狀態(tài)機完成此模塊。

接收器共設(shè)有5個工作狀態(tài): R_START (等待起始位)、R_CENTER (求中點)、R_WA IT (等待采樣)、R_SAMPLE (采樣)、R_STOP(停止位接收) 。

( 1) R_START狀態(tài): 當UART接收器復(fù)位后, 接收狀態(tài)機將處于這一個狀態(tài)。 在此狀態(tài), 狀態(tài)機一直在等待RXD的電平跳轉(zhuǎn), 從邏輯1變?yōu)檫壿?, 即起始位, 這意味著新的一幀UART數(shù)據(jù)幀的開始, 一旦起始位被確定, 狀態(tài)機將被轉(zhuǎn)入R_CENTER狀態(tài)。

( 2) R_CENTER 狀態(tài): 在本狀態(tài), 判定起始位是否真實, 通過對采樣時鐘的個數(shù)進行計數(shù)( RCNT16為采樣時鐘個數(shù)計數(shù)器) , 可以認為保持邏輯0超過1 /2個位時間的信號一定是起始位。

( 3) R_WA IT狀態(tài): 當狀態(tài)機處于這一狀態(tài), 等待計滿15個采樣時鐘周期, 在第16個采樣時鐘周期是進入R_SAMPLE狀態(tài)進行數(shù)據(jù)位的采樣檢測, 同時也判斷是否采集的數(shù)據(jù)位長度已達到數(shù)據(jù)幀的長度( FRAMELEN ) , 如果到來, 就說明停止位來臨了。

( 4) R_SAMPLE 狀態(tài): 即數(shù)據(jù)位采樣檢測, 完成后無條件狀態(tài)機轉(zhuǎn)入R_WA IT狀態(tài), 等待下次數(shù)據(jù)位的到來。

( 5) R_STOP狀態(tài): 無論停止位是1還是1. 5位, 或是2位, 狀態(tài)機在R_STOP不具體檢測RXD, 只是輸出幀接收完畢信號(REC_DONE《 = ‘1’), 停止位后狀態(tài)機轉(zhuǎn)回到R START狀態(tài), 等待下一個幀的起始位。

1. 3、發(fā)送器

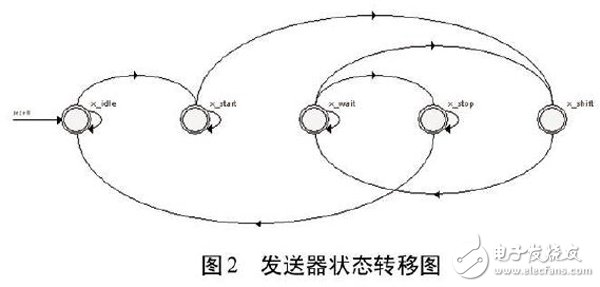

發(fā)送器在收到發(fā)送命令后, 先發(fā)送一個寬度為16個采樣周期的起始位, 并且將發(fā)送緩沖區(qū)數(shù)據(jù)放入發(fā)送移位寄存器, 然后每隔16個采樣周期移位寄存器移位輸出1個數(shù)據(jù), 當數(shù)據(jù)發(fā)送完, 根據(jù)需要選擇發(fā)送停止位的長度(常用長度有0、1、2) , 停止位的寬度同樣是16個采樣。 發(fā)送器只要每隔16個波特率周期輸出1個數(shù)據(jù)即可, 次序遵循1位起始位, 8位數(shù)據(jù)位和1位停止位。 在本設(shè)計中沒有校驗位。 該模塊也用狀態(tài)機實現(xiàn), 狀態(tài)圖如圖2:

發(fā)送器也設(shè)以下5個工作狀態(tài): X_IDLE (空閑)、X_START (起始位)、X_WA IT (移位等待)、X_SH IFT(移位)、X_STOP(停止) 。

( 1) X_IDLE狀態(tài): 當UART 被復(fù)位信號RESETL復(fù)位后, 狀態(tài)機將立刻進入這一狀態(tài)。 在這個狀態(tài)下, UART的發(fā)送器一直在等待一個數(shù)據(jù)幀發(fā)送命令, 當數(shù)據(jù)幀發(fā)送命令到來, 狀態(tài)轉(zhuǎn)入X_START, 準備發(fā)送起始位。

( 2) X_START狀態(tài): 在這個狀態(tài)下, UART的發(fā)送器一個位時間寬度的邏輯0 信號至TXD, 即起始位。 緊接著狀態(tài)機轉(zhuǎn)入X_WA IT 狀態(tài)。

( 3) X_WA IT狀態(tài): 同UART接收狀態(tài)機中的R_WA IT狀態(tài)類似。

( 4) X_SH IFT狀態(tài): 當狀態(tài)機處于這一狀態(tài)時, 實現(xiàn)待發(fā)數(shù)據(jù)的并串轉(zhuǎn)換。 轉(zhuǎn)換完成立即回到X_WA IT狀態(tài)。

( 5) X_STOP: 停止位發(fā)送狀態(tài), 當數(shù)據(jù)幀發(fā)送完畢, 狀態(tài)機轉(zhuǎn)入該狀態(tài), 并發(fā)送16個采樣時鐘周期的邏輯1信號, 即1位停止位。 狀態(tài)機送完停止位后回到X_IDLE狀態(tài), 并等待另一個數(shù)據(jù)幀的發(fā)送命令。

2、仿真測試

2. 1、 Testbench

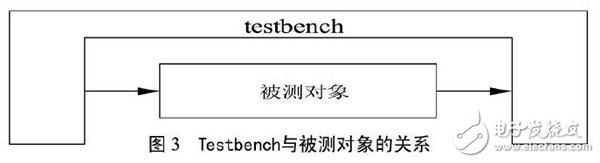

通常是這樣的代碼: 它對輸入產(chǎn)生預(yù)定的激勵, 然后有選擇地觀察響應(yīng), 并檢查該響應(yīng)是否為我們所期望。 功能驗證的核心不僅是這個平臺, 更在于對被測對象施加了什么樣的激勵以及在此激勵下被測對象的輸出是什么。 Testbench與被測對象的關(guān)系如圖3:

2. 1. 1、為何要寫Testbench

( 1)畫波形圖只能提供極低的功能覆蓋率。

( 2)畫波形圖無法實現(xiàn)驗證自動化。

( 3)畫波形圖難以定位錯誤。

( 4)畫波形圖的可重用性和平臺移植性極差。

( 5)通過畫波形圖的驗證速度極慢(特別是基于數(shù)據(jù)幀長度大的通信類設(shè)計, 畫波形幾乎是不可能的)。

2. 1. 2、Testbench的結(jié)構(gòu)

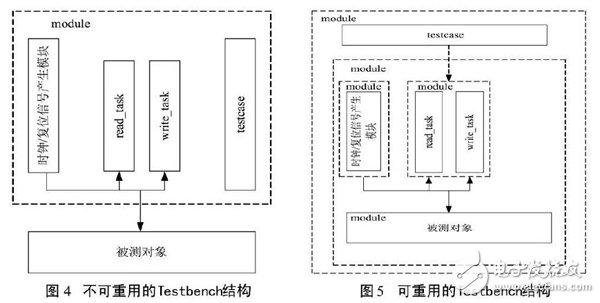

一個好的Testbench結(jié)構(gòu)應(yīng)該包含兩點要求: 層次清晰和具備較好的重用性。 這兩點要求之間也有很重要聯(lián)系: 只有層次清晰的Testbench才是可重用的, 重用性也將使Testbench層次更加清晰。

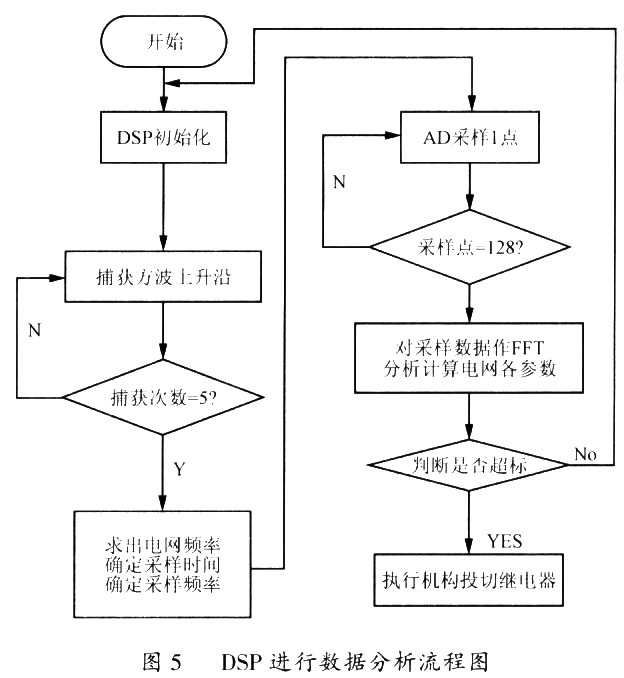

圖4是一個不可重用的Testbench結(jié)構(gòu), 它將所有的處理放在一個模塊中, 當進行新的設(shè)計時必然不可重用。

圖5是一個可重用的Testbench結(jié)構(gòu), 它將不同處理放在不同的模塊, 然后再層次化封裝, 當下一次進行類似的設(shè)計時, 必然有一部分模塊是可以直接調(diào)用, 或者只需修改相應(yīng)參數(shù)。

2. 1. 3、本設(shè)計的Testbench結(jié)構(gòu)

本設(shè)計采用上述可重用的Testbench結(jié)構(gòu)進行了Testbench的設(shè)計, 其中Testcase中主要進行了自發(fā)自收的測試, 定義了如下的測試序列, 發(fā)送數(shù)據(jù)FF- 00- A5。

2. 2、模塊仿真測試

2. 2. 1、波特率控制模塊

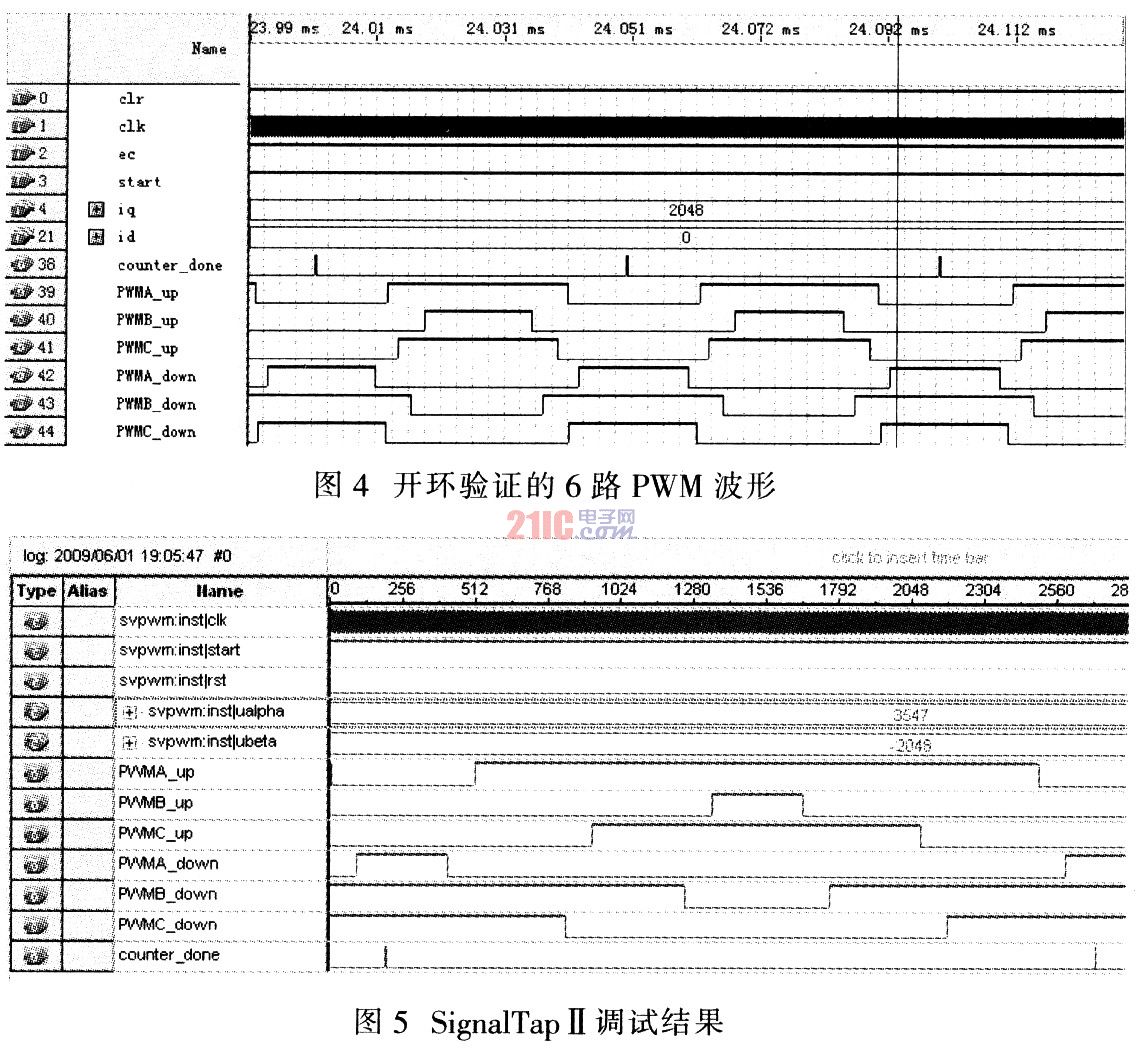

波特率模塊主要是一個計數(shù)分頻器, 輸入為高速時鐘和波特率因子(即分頻系數(shù)) , 即可實現(xiàn)任意整數(shù)分頻, 圖6是分頻系數(shù)為3時的波形仿真圖。

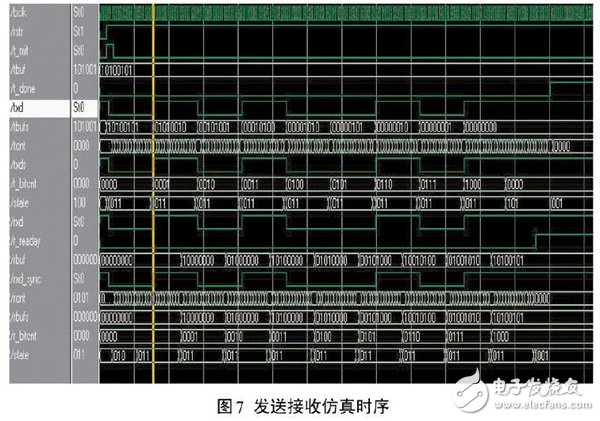

2. 2. 2、發(fā)送器模塊和接收模塊

由于可使用自發(fā)自收進行測試, 所以發(fā)送和接收模塊的測試可以同時進行, 設(shè)計中的測試數(shù)據(jù)為A5循環(huán)發(fā)送。 圖7是測試數(shù)據(jù)的仿真波形圖。

分析上圖得出結(jié)論: 標尺黃線開始, RXD 開始重新接收一幀數(shù)據(jù), 同時通過TXD 把tbuf中的數(shù)據(jù)由低位到高位移位發(fā)送。 state為各過程的狀態(tài)標志, 發(fā)送接收狀態(tài)顯示都為011. t b itcnt和r b itcnt分別是發(fā)送數(shù)據(jù)和接收數(shù)據(jù)計數(shù)位, 且發(fā)送跟接收數(shù)據(jù)都準確無誤。

2. 3、和PC機通訊的測試

仿真驗證功能之后, 將綜合后的電路寫入FPGA 芯片中, 通過一片RS232轉(zhuǎn)接與PC 機進行串行通信, 上位機使用的是串口調(diào)試助手軟件, 下位機的結(jié)果采用LED顯示。 設(shè)置好波特率9 600后, PC 機發(fā)送的數(shù)據(jù)可下位機接收, 并由LED顯示(字符串除外) , 并可以通過轉(zhuǎn)發(fā)回PC 機在串口小助手上顯示, 所測數(shù)據(jù)正確無誤。

3、結(jié)束語

本文完成了UART控制器的設(shè)計, 實現(xiàn)了異步串行通訊的基本功能, 并通過簡單的串口通訊進行了功能調(diào)試。 實際運用中可根據(jù)外設(shè)和處理器的不同需求, 在其基本功能基礎(chǔ)上進行波特率調(diào)整、不同幀格式的設(shè)置等升級改進, 運用于不同的數(shù)字系統(tǒng)。

電子發(fā)燒友App

電子發(fā)燒友App

評論