在高速系統中FPGA時序約束不止包括內部時鐘約束,還應包括完整的IO時序約束和時序例外約束才能實現PCB板級的時序收斂。因此,FPGA時序約束中IO口時序約束也是一個重點。只有約束正確才能在高速情況下保證FPGA和外部器件通信正確。

2022-09-27 09:56:09 1382

1382 會有比較詳細的結構圖,因為是新人對于找資料解決問題,還是比較弱,往往無從下手)2. 想對FPGA的IO,設計成可配置的形式,可以當普通IO口使用,有輸入輸出,也可以配置成復用模式,可配置成復用功能,復用輸入功能好像會遇到扇入的問題,大家有沒有比較好的思路。

2015-10-31 20:13:49

FPGA+DA怎么實現調相呢,不是數字調制。就是用一個正弦波的峰值來控制載波的相位,這個要怎么在FPGA中實現呢?希望大神能給個思路,我開始是想調制波直接用DDS IP核生成,然后用起幅值作為地址去查找表,表中存的是載波幅值,然后輸出,但是結果一直不對。

2017-06-29 16:00:24

一般涉及到數字處理和邏輯控制都用DSP加FPGA實現,最近想用FPGA實現數字處理和邏輯控制,聽搞通信的說多加幾個門就可以了,數字處理時鐘要求25MHZ,請高手指點一下。

2013-04-05 10:01:31

可以兼容多種不同的電壓標準,也有豐富的IO。

其次,FPGA的功能命名規則。功能命名規則每個廠家都會自己的一套規則,但都大同小異,我們重點來講述一下xilinx的命名(xilinx的文檔是行業標桿

2023-11-03 11:08:33

多種不同的電壓標準,也有豐富的IO。首先,FPGA的IO物理命名規則,也就是我們做管腳約束時候的命名,芯片通常是長方體或者正方體,所以命名通常采用字母+數字組合的方式,從上到下是字母(A,B,C,D

2019-07-18 14:26:01

請問,DAC的dma請求具體怎么實現?手冊說的挺簡單,dma的 源 目的是什么??正如例程中的梯形波,dma實現了一數據到dac寄存器的傳送,又有Dac_dma的使能是什么??

2019-04-28 06:15:55

請問一下AD7760的并行IO接口和控制IO接口能不能與MCU的IO直接連接呢?MCU的IO電平是3.3V。AD7760看了是差分信號輸入,有沒有大神做過單端輸入呢?誤差這方面怎樣呢?能不能達到0.001%呢?

2018-07-31 12:42:55

問題如標題,使用Xilinx 6系列FPGA控制DAC芯片AD9745,FPGA引腳電平為2.5V,但是DAC芯片的數字IO供電電壓為3.3V,兩者直連會不會有問題,FPGA內的數據能否正確的被

2018-09-17 15:20:43

片DAC,有些DAC芯片兩路信號相位,幅度均一致;有些芯片兩路輸出相位差異很大;請問,AD9783芯片是否有兩路相位同步的功能?如何實現兩路相同信號相位同步?r如何實現多片DAC之間的同步?感謝解答!

2019-02-28 14:49:44

請問CPLD/FPGA上電初始時IO口的狀態是怎么樣的呢?

2023-04-23 14:26:44

. 數字電平可能容易,但是如果想實現模擬電平,可以嗎?

下次使用的時候,希望能夠通過編程修改這種對應關系,同時想問問,如果FPGA可以實現,那么還有別的元器件可以實現嗎?

請問CPLD或者FPGA能夠實現任意的IO口對聯嗎?數字方式的可以話,那么模擬方式的也可以嗎?

2023-04-23 14:19:12

求助FM調制器的FPGA實現,對FPGA這些完全不了解,在網上看可以用DDS技術實現FM的數字調制,就在書上按照步驟先做了產生正弦波分頻模塊尋址模塊數據存儲模塊,但編譯不能通過,也不知道該怎樣進行頻率調制,請問該怎樣實現頻率的調制,請問有人寫過頻率調制的verilog代碼嗎,急求,謝謝

2019-03-16 11:43:26

請問,adau1452如何實現echo(回聲)功能呢?謝謝

2018-08-03 06:14:31

請問,adau1452如何實現echo(回聲)功能呢?謝謝

2023-11-29 07:20:01

請問一下FPGA如何實現別的芯片的管腳連接的呢?

2023-04-23 11:39:44

請問一下FPGA如何實現別的芯片的管腳連接的呢?

2023-04-23 11:40:17

DAC是如何去定義的?DAC地功能有哪些?怎樣去使用DAC的功能呢?

2021-11-15 06:28:40

請問有人用FPGA讀過數字mens麥克風的pdm信號嘛?最近在用fpga做音頻的采集,之前沒接觸過音頻編碼,不知道是不是用io口模擬spi協議就能讀麥克風陣列的pdm信號,請大神指導。

2016-10-24 22:16:20

Virtex-5 給它提供DAC 的DACCLK。v5 FPGA 可以輸出是 供電電壓為2.5V的LVPECL,請問能否按FPGA上給的連接方式與DAC3164的DACCLK管腳相連?

2019-06-13 06:41:07

如題,新唐M451的DAC功能,通過運放控制LED,當使能DAC時,一切正常,不過因為即使把DAC_OUT設為0,LED也會微弱亮光,所以想禁止DAC來完全關閉輸出,沒想到禁止后,DAC的IO腳卻有1.5V電壓,而不是0V,請問哪位大俠知道這是什么情況?

2023-06-28 07:59:43

想試試新唐的MCU,但發現只有少量MCU帶了DAC。

新唐是出于什么考慮不帶DAC模塊呢?

大家用新唐MCU的時候,又是怎么實現快速DAC的呢?

2023-06-27 06:50:07

DAC是什么?STM32 DAC功能是如何實現輸出音頻波形的?

2021-11-15 07:18:19

使用stm32 USB功能 控制自身IO口實現通信(發送與接收)功能,即USB連接電腦,兩個IO口分別連接下位機的發送與接收端,實現上位機控制與下位機數據上傳的功能,上行速率(I口接收)1Mbps

2019-01-04 09:19:09

的實現方法我們用一個臺PC去解碼MP3,然后把信號發送到用1位數模轉換(DAC)設置成的FPGA傷。音頻輸出 我們需要一個DAC(數字-模擬轉換器)FPGA(數字)連接到揚聲器(模擬)。傳統的做法

2012-03-15 09:55:03

一個單音信號分2路由FPGA輸入到DAC,然后在頻譜儀上面看為何頻譜不對呢?請問為何

2015-07-11 20:07:34

串口IO口映射功能是指什么?串口IO口映射功能該如何去實現呢?

2021-12-13 07:07:24

通過編程來改變內部結構的芯片。FPGA 功能實現:需要通過編程即設計硬件描述語言,經過 EDA 工具編譯、

2022-01-25 06:45:52

什么是數字中頻?FPGA怎么實現數字中頻?

2021-05-08 08:05:40

如圖,我想做一個音樂播放電路。用上位機解碼經串口發給FPGA,再由fpga控制12位dac芯片輸出模擬信號經濾波放大后輸出到揚聲器。請問這么做可行嗎?各位有沒有相關資料或經驗呢?

2015-08-05 11:55:00

請問STM32F103VET6有沒有DAC的功能啊?如果有,為什么會沒有DAC輸出啊? 這事搞了我兩天了,自已實在找不出下面哪里錯了,怎么會沒有DA輸出呢?DAC輸出引腳為PA4(DAC

2018-08-27 17:23:40

DSP技術廣泛應用于各個領域,但傳統的數字信號處理器由于以順序方式工作使得數據處理速度較低,且在功能重構及應用目標的修改方面缺乏靈活性。而使用具有并行處理特性的FPGA實現數字信號處理系統,具有很強的實時性和靈活性,因此利用FPGA實現數字信號處理成為數字信號處理領域的一種新的趨勢。

2019-10-17 08:12:27

首先我們要知道哪些io口可以實現中斷。一、基本那么什么是中斷呢。我們可以認為是放下目前要做的事A,去做另外的事B,做完B后再回來繼續做A。比如說我們要寫一個程序,中途渴了要去喝水,我們喝完水后再繼續

2021-11-29 07:03:46

FPGA數字信號處理——基于FPGA和高速DAC的DDS設計與頻率調制(一)——X現如今,隨著高速模數-數模轉換技術和FPGA的發展。FPGA的高速性、并行性、高數據吞吐量與高速數模-模數轉換技術

2021-07-23 08:06:59

內容:1.掌握Verilog語法及使用方法,初步了解FPGA的基本工作原理及其他簡單數字系統的系統級設計方法,學會如何利用FPGA實現實際的各種功能。 2.采用Labview實現上位機程序編寫,實現

2016-04-19 20:33:42

本帖最后由 kandy286 于 2013-11-8 00:33 編輯

剛學FPGA,用FPGA+DAC設計的DDS,已實現調頻,調相功能。可是調幅該怎么控制呢?有種方案是改變DAC的參考電壓

2013-11-08 00:32:04

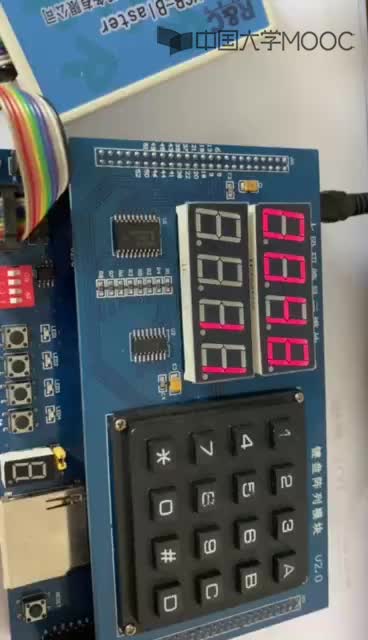

1、基于FPGA設計實現一個多功能數字鐘在FPGA中設計實現一個多功能數字鐘,具備以下功能:準確計時。能顯示時、分、秒,小時的計時為24進制,分和秒的計時為60進制。校時功能。時、分可調。準點報時

2022-07-08 17:26:04

音頻二進制文件是怎樣生成的?音頻功率放大器TDA2030的原理是什么?如何去實現基于STM32的DAC音頻輸出呢?

2021-10-27 06:44:21

,其它FPGA廠家的資料多多少少會參考xilinx)。通常xilinx 的功能命名格式為:IO_LXXY#/IO_XX。其中: (1) IO代表用戶IO; (2) L代表差分,XX代表在當

2020-12-23 17:44:23

在FPGA中,動態相位調整(DPA)主要是實現LVDS接口接收時對時鐘和數據通道的相位補償,以達到正確接收的目的。那么該如何在低端FPGA中實現DPA的功能呢?

2021-04-08 06:47:08

將具有信號處理功能的FPGA與現實世界相連接,需要使用模數轉換器(ADC)或數模轉換器(DAC)一旦執行特定任務,FPGA系統必須與現實世界相連接,而所有工程師都知道現實世界是以模擬信號而非數字

2019-09-19 07:51:05

如何控制FPGA燒寫時io口的電平呢?

2023-04-23 14:47:00

現場可編程門陣列(Field Programmable Gate Arrays,FPGA)是一種可編程使用的信號處理器件。通過改變配置信息,用戶可對其功能進行定義,以滿足設計需求。通過開發,FPGA能夠實現任何數字器件的功能。與傳統數字電路相比,FPGA具有可編程、高集成度、高可靠性和高速等優點。

2019-11-11 08:31:12

我正在嘗試將Kintex 7 FPGA與CMOS輸入DAC連接。我相信這意味著我需要使用標準IO引腳而不是GTX收發器。標準IO引腳上的最大頻率和數據速率是多少?謝謝。

2020-05-14 09:31:31

怎么實現基于FPGA的dac控制?

2021-11-02 07:32:32

怎么實現基于STM32的PWM和DAC的功能?

2021-11-19 07:53:09

數字系統的設計人員擅長在其印制電路板上用FPGA和CPLD將各種處理器、存儲器和標準的功能元件粘合在一起來實現數字設計。除了這些數字功能之外,FPGA和CPLD還可以使用LVDS輸入、簡單的電阻電容(RC)電路和一些FPGA或CPLD的數字邏輯單元實現共模功能,從而構建模數轉換器(ADC)。

2019-08-19 06:15:33

DAC數字/模擬轉換模塊是什么?有何作用?怎樣去使用STM32中的DAC接口呢?

2021-11-25 09:03:38

怎樣通過編寫程序去實現數字時鐘顯示功能呢?

2022-03-01 06:53:39

內容:1.掌握Verilog語法及使用方法,初步了解FPGA的基本工作原理及其他簡單數字系統的系統級設計方法,學會如何利用FPGA實現實際的各種功能。 2.采用Labview實現上位機程序編寫,實現

2016-04-19 20:44:29

結合DAC和µP監控電路,提高模擬IO的可靠性

2009-04-16 23:34:53 18

18 DAC與數字電位器摘要:本應用筆記對數/模轉換器(DAC)和數字電位進行了對比,傳統的數字電位器用于替代機械電位器。隨著分辨率的提高和功能的增多,數字電位器

2009-11-16 11:45:21 62

62 用matlab來實現fpga功能的設計

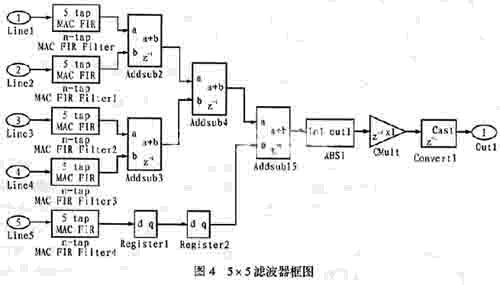

摘要:System Generator for DSP是Xilinx公司開發的基于Matlab的DSP開發工具?熗?時也是一個基于FPGA的信號處理建模和設計工具。

2008-01-16 18:10:54 11207

11207

基于FPGA和CPLD數字邏輯實現ADC技術

數字系統的設計人員擅長在其印制電路板上用FPGA和CPLD將各種處理器、存儲器和標準的功能元件粘合在一起來實現

2010-05-25 09:39:10 1309

1309

本文介紹基于FPGA實現二次群數字信號的分接部分的功能,包括幀頭捕獲、幀丟失告警、基群信號提取,去除插入碼、負碼速調整等二次群分接的關鍵技術。

2011-08-21 17:55:17 850

850

本書共分8章,主要內容包括典型fpga器件的介紹、vhdl硬件描述語言、fpga設計中常用軟件簡介、用fpga實現數字信號處理的數據規劃、多種結構類型的fir數字濾波器的fpga實現、不同結構

2011-11-04 15:50:12 0

0 在Quartus Ⅱ開發環境下,用Verilog HDL硬件描述語言設計了一個可以在FPGA芯片上實現的數字時鐘. 通過將設計代碼下載到FPGA的開發平臺Altera DE2開發板上進行了功能驗證. 由于數字時鐘的通用

2011-11-29 16:51:43 178

178 本文以FPGA平臺為基礎,在QuartusⅡ開發環境下設計開發多功能數字鐘。數字鐘實現計時\校時\整點報時\世界時鐘功能.

2012-12-18 11:51:03 33158

33158 基于FPGA的數字鎖相環設計與實現技術論文

2015-10-30 10:38:35 9

9 本書比較全面地闡述了fpga在數字信號處理中的應用問題。本書共分8章,主要內容包括典型fpga器件的介紹、vhdl硬件描述語言、fpga設計中常用軟件簡介、用fpga實現數字信號處理的數據規劃、多種

2015-12-23 11:07:46 44

44 dac0832ad08098259a,825382508255等芯片的fpga實現及仿真

2016-01-20 15:12:47 13

13 Xilinx FPGA工程例子源碼:用FPGA實現數字鎖相環

2016-06-07 15:07:45 37

37 基于FPGA的數字時鐘設計,可實現鬧鐘的功能,可校時。

2016-06-23 17:15:59 64

64 基于8051的Proteus仿真-DAC0808實現數字調壓

2016-09-01 23:28:14 27

27 數字信號處理的FPGA實現

2016-12-14 22:08:25 32

32 基于FPGA技術的數字相關器的設計與實現

2016-12-16 22:23:00 14

14 基于FPGA的全數字FQPSK調制器實現_楊峰

2017-03-19 11:38:26 2

2 能夠實現任何 數字器件的功能。與傳統數字電路相比,FPGA 具有可編程、高集成度、高可靠性和高速等優點。 世界時鐘模塊的工作原理及設計實現 本設計中加入了世界時鐘模塊,能夠將北京時間快速轉換為格林威治標準時。北京位于東八區,格林威治 位于本初子午線附近,北京時間比格

2017-11-30 14:57:30 73

73 本系統由FPGA、單片機控制模塊、鍵盤、LCD 液晶顯示屏、DAC輸出電路和末級放大電路構成。僅用單片FPGA 就實現了直接數字頻率合成技術(DDS),產生穩幅正弦波,并在數字域實現了AM、FM

2019-10-18 17:31:25 13

13 近年來,數字AM調制技術應用越來越廣泛,具體應用中多采用專用的調制芯片完成。文中介紹一種在FPGA中實現數字AM調制的方法,采用該方法設計的系統具有使用靈活、擴展性強、便于集成等優點。文中先討

2020-07-31 17:50:22 19

19 在高速系統中FPGA時序約束不止包括內部時鐘約束,還應包括完整的IO時序約束利序例外約束才能實現PCB板級的時序收斂。因此,FPGA時序約束中IO口時序約束也是重點。只有約東正確才能在高速情況下保證FPGA和外部器件通信正確

2021-01-13 17:13:00 11

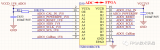

11 介紹IO口與FPGA管腳對應關系表。

2021-03-18 10:02:26 12

12 FPGA設計中DAC控制的Verilog實現圖文稿(ltspice 放置電源)-該文檔為FPGA設計中DAC控制的Verilog實現圖文稿資料,講解的還不錯,感興趣的可以下載看看…………………………

2021-07-26 12:17:02 10

10 FPGA設計中DAC控制的Verilog實現(單片機電源維修)-該文檔為FPGA設計中DAC控制的Verilog實現資料,講解的還不錯,感興趣的可以下載看看…………………………

2021-07-26 12:18:48 18

18 FPGA設計中DAC控制的Verilog實現修訂稿(空調電源芯片)-該文檔為FPGA設計中DAC控制的Verilog實現修訂稿資料,講解的還不錯,感興趣的可以下載看看…………………………

2021-07-26 13:13:56 10

10 數字信號處理的FPGA實現.第3版英文

2021-10-18 10:55:32 0

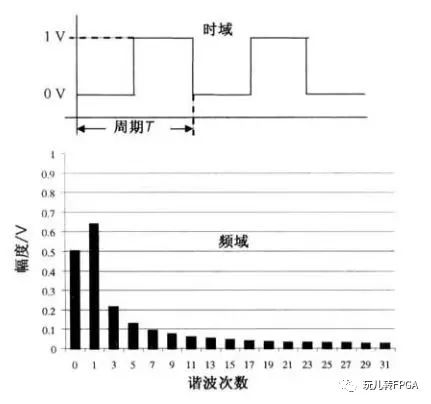

0 假設方波頻率為f0。橫軸諧波次數為0的柱狀圖代表直流分量的幅值,也就是方波的平均電壓(與占空比有關),諧波次數為1代表頻率為f0的正弦波分量的幅值,3代表,3*f0的正弦波分量幅值,以此類推。

2022-12-07 10:31:01 1049

1049 工作方式; IO串并轉換資源:分析IO資源如何實現串并轉換。 其中第二、三系列是對第一系列中的部分內容進行更進一步的詳細描述。本篇是對于第一個系列——IO資源進行部分描述,共分為幾個章節進行具體闡述。 FPGA IO資源的基本單元架構為一個個 IO tile ,下圖為 IO tile 的結構

2022-12-13 13:20:06 1099

1099 引言:上一篇文章我們介紹了通過添加電阻器、場效應晶體管(FET)開關、電平轉換器甚至其他Xilinx FPGA等選項實現HP Bank IO與2.5V/3.3V外設對接的方法。本文介紹利用TI公司TXS0108實現FPGA IO Bank接不同外設IO接口電壓轉換。

2023-05-16 09:02:50 2100

2100

FPGA(可編程邏輯門陣列)是一種集成電路芯片,具有可編程的數字邏輯功能。多功能數字鐘系統利用FPGA技術實現了時鐘的顯示、計時、報時等功能。本文將詳細介紹FPGA多功能數字鐘系統

2024-01-02 16:50:57 252

252

電子發燒友App

電子發燒友App

評論