Zynq中AXI4-Lite功能 AXI4-Lite接口是AXI4的子集,專用于和元器件內(nèi)的控制寄存器進行通信。AXI-Lite允許構(gòu)建簡單的元件接口。這個接口規(guī)模較小,對設(shè)計和驗證方面的要求更少

2020-09-27 11:33:02 8051

8051

AXI (Advanced eXtensible Interface) 本是由ARM公司提出的一種總線協(xié)議, Xilinx從 6 系列的 FPGA 開始對 AXI 總線提供支持,目前使用 AXI4

2020-12-04 12:22:44 6179

6179

構(gòu)成的傳輸數(shù)據(jù)的通道, 一般由數(shù)據(jù)線、地址線、 控制線構(gòu)成。?Xilinx從6系列的 FPGA 開始對 AXI 總線提供支持, 此時 AXI 已經(jīng)發(fā)展到

2020-12-25 14:07:02 2957

2957

賽靈思 AXI Verification IP (AXI VIP) 是支持用戶對 AXI4 和 AXI4-Lite 進行仿真的 IP。它還可作為 AXI Protocol Checker 來使用。

2022-07-08 09:24:17 1281

1281 在 AXI 基礎(chǔ)第 2 講 一文中,曾提到賽靈思 Verification IP (AXI VIP) 可用作為 AXI 協(xié)議檢查工具。在本次第4講中,我們將來了解下如何使用它在 AXI4 (Full) 主接口中執(zhí)行驗證(和查找錯誤)。

2022-07-08 09:31:38 1945

1945 AXI Traffic Generator IP 用于在AXI4和AXI4-Stream互連以及其他AXI4系統(tǒng)外設(shè)上生成特定序列(流量)。它根據(jù)IP的編程和選擇的操作模式生成各種類型的AXI事務(wù)。是一個比較好用的AXI4協(xié)議測試源或者AXI外設(shè)的初始化配置接口。

2023-11-23 16:03:45 580

580

和Stream 接口支持64bit,128bit和256bit的數(shù)據(jù)AXI4 Master和Slave接口可配置成AXI3接口配置:通過PCIE和(或)AXI4-Lite Slave接口可操作橋配置空間

2016-03-11 10:57:58

此信號。 從機(slave)控制的信號 11.TREADY 握手信號 一個AXI-stream傳輸?shù)臅r序圖: 圖4?59 AXI-stream example AXI4-stream主從

2021-01-08 16:52:32

我必須通過AXI4-lite接口配置Jesd204b核心,或者我可以簡單地將AXI4-lite端口保持未連接狀態(tài)(強制接地)?Jesd204核心示例top沒有提供有關(guān)AXI4-Lite端口配置的指導(dǎo)。

2020-05-15 09:30:54

最近在搞AXI4總線協(xié)議,有一個問題困擾了兩天,真的,最后知道真相的我,差點吐血。 問題是這樣的,我設(shè)置了突發(fā)長度為8,結(jié)果,讀了兩個輪回不到,斷了,沒有AWREDATY信號了,各種找,最后發(fā)現(xiàn)設(shè)置

2016-06-23 16:36:27

如果在仿真的時候出現(xiàn)可以寫,可以讀,但是讀出來的數(shù)據(jù)一直是那么幾個的問題,很有可能,你和我一樣,是個馬大哈了,去看DQ,是不是地址也來來去去就那么幾個?是的話,可以考慮考慮你的地址的問題,AXI4

2016-06-24 16:25:38

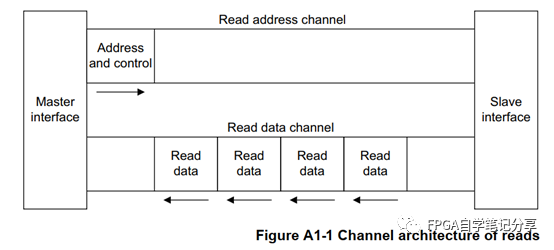

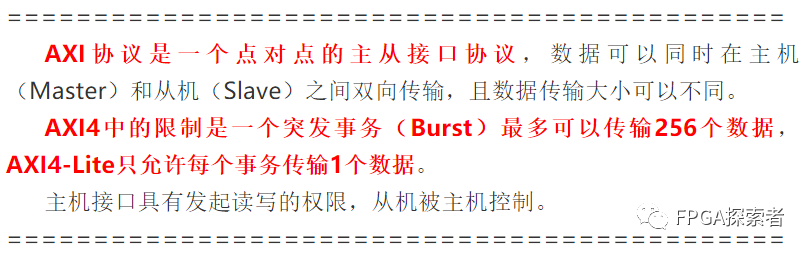

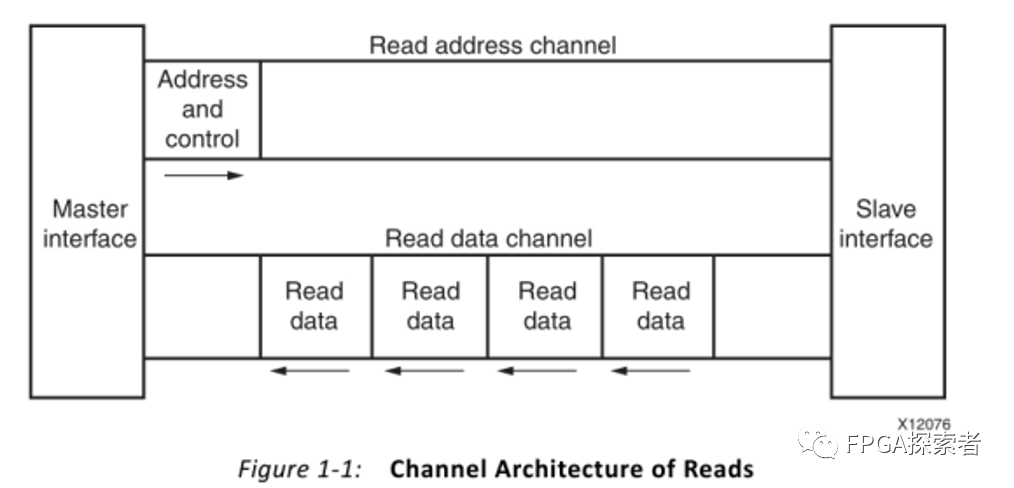

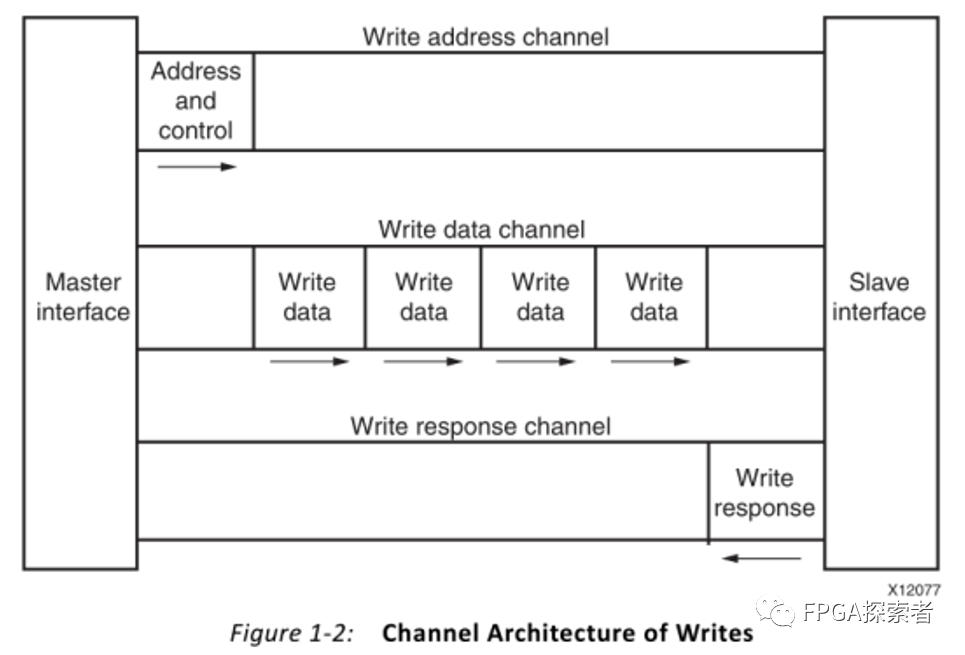

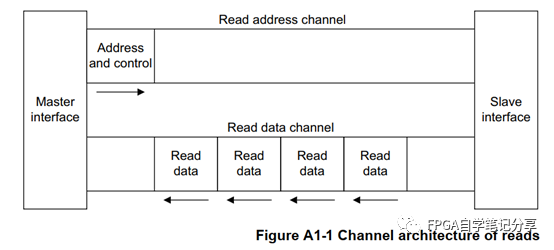

AXI4協(xié)議基于猝發(fā)式傳輸機制。在地址通道上,每個交易有地址和控制信息,這些信息描述了需要傳輸?shù)臄?shù)據(jù)性質(zhì)。主從設(shè)備間的數(shù)據(jù)傳輸有兩種情況,一種是主設(shè)備經(jīng)過寫通道向從設(shè)備寫數(shù)據(jù)(簡稱寫交易

2021-01-08 16:58:24

我想知道AXI4流互連IP 2中True Round-Robin和Round-Robin仲裁方案之間的區(qū)別,特別是當所有從接口都不活動時。我已經(jīng)參考了文檔PG085,并提到“如果所有從接口都不活動

2020-05-20 14:51:06

Controller 的輸出(讀取通道)連接到 AXI Stream FIFO ,最后處理器通過 AXI4-Lite 接口讀取數(shù)據(jù)。下面顯示了設(shè)計中的輸入路徑,其中包含由 XADC 生成的信號和一個

2022-11-04 11:03:18

AXI有哪些性能?AXI的特點是什么?AXI4有哪些工作模式?

2021-06-23 08:13:52

是主機,而第一個字母 “S” 表示 PS 是從機。在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三種總線,但PS與PL之間的接口卻只支持前兩種,AXI-Stream只能在PL中實現(xiàn)

2022-04-08 10:45:31

突發(fā)傳輸; AXI4-Lite:(For simple, low-throughput memory-mapped communication)是一個輕量級的地址映射單次傳輸接口,占用很少的邏輯單元

2022-10-14 15:31:40

到新的通道。錯誤的處理例化了一個Axi4ReadOnlySlaveError:可以看到,只有所有slave端口的地址段大小總和小于Axi4總線能覆蓋的地址范圍時方例化

2022-08-04 14:28:56

AXI4-Streamslave接口上TDATA信號的寬度(以字節(jié)為單位)。 AXI4-Stream主接口TDATA寬度是此值乘以從屬接口數(shù)參數(shù)。此參數(shù)是一個整數(shù),可以在0到(512 /從站接口數(shù))之間變化。設(shè)置為0以省略

2020-08-20 14:36:50

你好,大家好。我正在使用EMI14.4和xc6v315t。我正在嘗試模擬IP CORE.It的axi4-stream interconnect.I配置ip為6siand 4mi。但是當我用ismI模擬它時發(fā)現(xiàn)s_tready很低,有什么問題?

2020-06-18 15:08:59

。 AXI握手時序圖 在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三種總線,通過表5-1,我們可以看到這三種AXI接口的特性。 AXI4-Lite: 具有輕量級,結(jié)構(gòu)

2021-01-07 17:11:26

您可以將協(xié)議斷言與任何旨在實現(xiàn)AMBA?4 AXI4的接口一起使用?, AXI4 Lite?, 或AXI4流? 協(xié)議通過一系列斷言根據(jù)協(xié)議檢查測試接口的行為。

本指南介紹SystemVerilog

2023-08-10 06:39:57

XHB將AXI4協(xié)議轉(zhuǎn)換為AHB-Lite協(xié)議,并具有AXI4從接口和AHB-Lite主接口。有關(guān)AXI4事務(wù)如何通過XHB橋接到AHB-Lite的信息,請參閱第2-2頁的表2-1

2023-08-02 06:51:45

ARM處理器中有些總線APB AHB AXI 3 AXI 4,他們的有什么不同,各自作用?

2023-10-24 07:16:36

in the reference design consist of AXI4, AXI4-Lite, andAXI4-Stream interfaces as described in the AMBA AXI4

2012-01-26 18:57:03

的fifo接口),用戶只要操作fifo接口,無需關(guān)心PCIE的內(nèi)部驅(qū)動。為了便于讀者更加明白,可以深入了解PCIE,我們將會制作一個PCIE的連載系列。今天,首先說一下自定義AXI4的IP核,至于AXI4

2019-12-13 17:10:42

這是SoC Designer AXI4協(xié)議包的用戶指南。該協(xié)議包包含SoC Designer組件、探針和ARM AXI4協(xié)議的事務(wù)端口接口(包括對AMBA4 AXI的支持)。

2023-08-10 06:30:18

或起點嗎?此外,我的VHDL模塊具有AXI4流接口,而其他模塊具有自定義接口。如何使它們兼容?將等待有用的回復(fù)。問候

2020-05-22 09:24:26

你好,我有一個關(guān)于XADC及其AXI4Lite接口輸入的問題。我想在Microzed 7020主板上測試XADC,在通過AXI4Lite接口將Zynq PL連接到XADC向?qū)В▍⒁姷?b class="flag-6" style="color: red">一個附件)之后

2018-11-01 16:07:36

data.)面向高速流數(shù)據(jù)傳輸;去掉了地址項,允許無限制的數(shù)據(jù)突發(fā)傳輸規(guī)模。AXI4總線和AXI4-Lite總線具有相同的組成部分:(1)讀地址通道,包含ARVALID, ARADDR, ARREADY

2018-01-08 15:44:39

。

●AXI4: 主要面向高性能地址映射通信的需求,允許最大256輪的數(shù)據(jù)突發(fā)傳輸。

●AXI4-Lite: 是一個輕量級的,適用于吞吐量較小的地址映射通信總線,占用較少的邏輯資源

2023-11-03 10:51:39

) AXI協(xié)議(又稱AXI4.0),包括3種接口標準:AXI4、AXI-Stream、AXI-lite。AXI4:適用于要求數(shù)據(jù)高速傳輸?shù)膱龊稀?b class="flag-6" style="color: red">AXI-Stream:如FIFO,數(shù)據(jù)傳輸不需要地址,而是

2016-12-16 11:00:37

AXI4總線協(xié)議,接下來我們將對該協(xié)議作一個更具體的介紹。AXI的英文全稱是Advanced eXtensible Interface,即高級可擴展接口,它是ARM公司所提出的AMBA(Advanced

2020-10-22 15:16:34

按鍵控制LED實驗》中的AXI4-Lite接口等。其中AXI4-Lite接口屬于AXI4總線協(xié)議,接下來我們將對該協(xié)議作一個更具體的介紹。AXI的英文全稱是Advanced eXtensible

2020-09-04 11:10:32

[]合成了內(nèi)存),輸出端口合成為ap_fifo,這意味著,由于AXi4Lite不支持fifo結(jié)構(gòu),因此只能使用AXI4Stream接口/總線從輸出端口result []讀取數(shù)據(jù)。我也是這個嵌入式總線和接口

2019-02-28 13:47:30

接口進行仿真驗證),提前規(guī)避和發(fā)現(xiàn)一些不滿足AXI總線規(guī)范的設(shè)計問題。本文就跟大家分享如何使用Xilinx AXI VIP對自己的設(shè)計搭建仿真驗證環(huán)境的方法。本文參考的Xilinx官方文檔為

2022-10-09 16:08:45

多選一的抉擇相較于Axi4寫通路,多通路的多選一就容易多了。對于Axi4ReadOnlyArbiter,其僅需處理兩個問題:Ar通路多端口仲裁,其處理和寫通路aw通路基本相同,采用多端口RR調(diào)度即可

2022-08-08 14:32:20

大家好,我正在兩個時鐘域之間穿過AXI4-Stream,并嘗試使用AXI4-Stream時鐘轉(zhuǎn)換器核心,使用tkeep端口但是在合成時它被Vivado 2015.2在實例化時刪除了!這是綜合警告

2020-05-08 08:56:14

元素(如混合端序結(jié)構(gòu))的支持。

本文檔重點介紹AXI4中定義的AXI的關(guān)鍵概念,并強調(diào)了差異

適用時,適用于AXI3。AXI5擴展了AXI4,并引入了一些性能和Arm

架構(gòu)特征。此處描述的關(guān)鍵概念仍然適用,但

AXI5在此未涵蓋

2023-08-09 07:37:45

AXI3端口。互連如何工作?3.數(shù)據(jù)增大是否是AXI互連的一部分?以上來自于谷歌翻譯以下為原文I have doubts on AXI Interconnect, 1. I have AXI4

2019-04-01 10:10:35

使用AXI4流快速讀取?如果這不是一個不錯的方法,還有其他方法可以使用Virtex-7來解決這個問題嗎?以上來自于谷歌翻譯以下為原文Hey all. I'm currently working

2019-05-05 13:14:10

你好是否可以使用帶有AXI4接口的邏輯核心ip reed solomon編碼器版本9。問候Rose Varghese

2020-05-20 15:44:58

現(xiàn)在我正在使用Xilinx的AXI視頻處理內(nèi)核進行小型設(shè)計。現(xiàn)在我面對一個奇怪的問題。我的設(shè)計很簡單。我使用Xilinx的三個內(nèi)核:1.測試模式發(fā)生器(TPG)2。視頻定時控制(VTC

2019-03-08 10:00:05

的FPGA開始引入的一個接口協(xié)議(AXI3)。在ZYNQ中繼續(xù)使用,版本是AXI4,ZYNQ內(nèi)部設(shè)備都有AXI接口。AXI4-Lite則是AXI4的一個簡化版本,實現(xiàn)AXI4運行起來的最少接口

2019-05-06 16:55:32

讀寫分離的設(shè)計在Axi4總線中,讀和寫通道是完全相互獨立,互不干擾。故而無論是在設(shè)計Decoder還是Arbiter時,均可以采用讀寫分離的方式。如前文所述,SpinalHDL在基于Axi4總線

2022-08-03 14:27:09

,ar)共用一組信號的接口(arw,w,b,r)。關(guān)于總線互聯(lián)的設(shè)計凡是設(shè)計中用到Axi4總線的設(shè)計總離不開總線互聯(lián)。在Xilinx FPGA使用中,VIvado針對Axi4總線提供了豐富的IP,對于

2022-08-02 14:28:46

大家好。我遇到了xilinx視頻內(nèi)核的問題,并試圖解決這個問題好幾周但都失敗了。有人能給我一些關(guān)于AXI4-Stream到Video核心的技巧嗎?我試圖在我的項目中實現(xiàn)Video Scaler核心

2019-11-08 09:53:46

microblaze通過串口讀寫FPGA內(nèi)部axi4總線上的寄存器

2020-12-23 06:16:11

我們可以使用AXI-Stream Broadcaster作為AXI開關(guān)嗎?如果可能,我們需要控制切換哪個信號?我想開發(fā)小型應(yīng)用程序,它涉及廣播AXI流數(shù)據(jù)并將AXI流數(shù)據(jù)切換到特定的從站。在這個應(yīng)用程序中,我們只有一個主站和8個從站。我們想在從站之間切換流數(shù)據(jù)。提前致謝。

2020-05-07 09:42:16

),以更深入地了解AXI的第一個版本。隨著新版本的AXI(例如AXI4,AXI4-Lite和AXI4-Stream),AXI在AMBA版本4中看到了一些重大變化。將來的AMBA文章將討論用于組件之間系統(tǒng)

2020-09-28 10:14:14

目的是利用嵌入在Xilinx FPGA中的MicroBlaze核實現(xiàn)基于AXI總線的雙核嵌入式系統(tǒng)設(shè)計以及共享實現(xiàn)LED燈的時控.

2012-03-09 14:17:01 91

91 AMBA AXI 總線學習筆記,非常詳細的AXI總線操作說明

2015-11-11 16:49:33 11

11 : AXI4-Stream—使用DMA時,從Zynq SoC的XDAC流式接口到內(nèi)存映射,提供高性能輸出 AXI4-Lite —配置和控制XADC以及DMA控制器 AXI4 —配置

2017-02-08 08:10:39 286

286 Xilinx的視頻的IP CORE 一般都是 以 AXI4-Stream 接口。 先介紹一下, 這個IP的作用。 下面看一下這個IP 的接口: 所以要把標準的VESA信號 轉(zhuǎn)為

2017-02-08 08:36:19 531

531

基于AXI4Stream總線協(xié)議,在Xilinx公司提供的FPGA上實現(xiàn)了一個具有缺陷像素校正、色彩濾波陣列插值、圖像降噪實時圖像采集與顯示功能的視頻系統(tǒng)。AXI4Stream總線協(xié)議由ARM公司

2017-11-17 08:58:01 4189

4189 1、AXI 總線通道,總線和引腳的介紹 AXI接口具有五個獨立的通道: (1)寫地址通道(AW):write address channel (2)寫數(shù)據(jù)通道( W): write data

2018-01-05 08:13:47 9601

9601

這將創(chuàng)建一個附帶 BD 的 Vivado 工程,此 BD 包含 AXI VIP (設(shè)置為 AXI4-Lite 主接口) 和 AXI GPIO IP。這與我們在 AXI 基礎(chǔ)第 3 講一文 中完成的最終設(shè)計十分相似。

2020-04-30 16:24:50 2068

2068

在本教程中,我們將來聊一聊有關(guān)如何在 Vitis HLS 中使用 AXI4-Lite 接口創(chuàng)建定制 IP 的基礎(chǔ)知識。

2020-09-13 10:04:19 5961

5961

AXI-4 Memory Mapped也被稱之為AXI-4 Full,它是AXI4接口協(xié)議的基礎(chǔ),其他AXI4接口是該接口的變形。總體而言,AXI-4 Memory Mapped由五個通道構(gòu)成,如下圖所示:寫地址通道、寫數(shù)據(jù)通道、寫響應(yīng)通道、讀地址通道和讀數(shù)據(jù)通道。

2020-09-23 11:20:23 5453

5453

在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三種總線,但PS與PL之間的接口卻只支持前兩種,AXI-Stream只能在PL中實現(xiàn),不能直接和PS相連,必須通過AXI-Lite

2020-09-24 09:50:30 4289

4289

在FPGA程序設(shè)計的很多情形都會使用到AXI接口總線,以PCIe的XDMA應(yīng)用為例,XDMA有兩個AXI接口,分別是AXI4 Master類型接口和AXI-Lite Master類型接口,可通過

2020-10-30 12:32:37 3953

3953

新的賽靈思器件設(shè)計中不可或缺的一部分。充分了解其基礎(chǔ)知識對于賽靈思器件的設(shè)計和調(diào)試都很有幫助。 本篇博文將介紹賽靈思器件上的 AXI3/AXI4 的相關(guān)基礎(chǔ)知識。首先,我們將從一些通俗易懂的知識、理論

2020-09-27 11:06:45 5857

5857

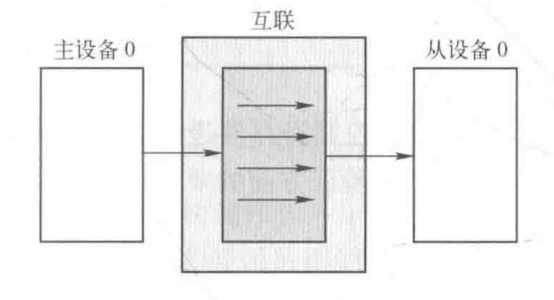

的線連接。在這種模式下,沒有延遲,同時不消耗邏輯資源。 2. 只轉(zhuǎn)換模式 當連接一個主設(shè)備和一個從設(shè)備時,AXI互聯(lián)執(zhí)行不同的轉(zhuǎn)換和流水線功能:數(shù)據(jù)位寬轉(zhuǎn)換、時鐘速率轉(zhuǎn)換、AXI-Lite從適應(yīng)、AXI-3從適應(yīng)、流水線。在只轉(zhuǎn)換模式下,AXI互聯(lián)不包含仲裁、解碼或布

2020-11-16 17:39:24 3093

3093

DMA的總結(jié) ZYNQ中不同應(yīng)用的DMA 幾個常用的 AXI 接口 IP 的功能(上面已經(jīng)提到): AXI-DMA:實現(xiàn)從 PS 內(nèi)存到 PL 高速傳輸高速通道 AXI-HP----AXI-Stream

2020-10-09 18:05:57 6391

6391

在《AXI-Lite 自定義IP》章節(jié)基礎(chǔ)上,添加ilavio等調(diào)試ip,完成后的BD如下圖: 圖4?53 添加測試信號 加載到SDK,并且在Vivado中連接到開發(fā)板。 Trigger Setup

2020-10-30 17:10:22 2041

2041

和接口的構(gòu)架 在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三種總線,但PS與PL之間的接口卻只支持前兩種,AXI-Stream只能在PL中實現(xiàn),不能直接和PS相連,必須通過

2020-11-02 11:27:51 3880

3880

AXI-Stream代碼詳解 AXI4-Stream跟AXI4的區(qū)別在于AXI4-Stream沒有ADDR接口,這樣就不涉及讀寫數(shù)據(jù)的概念了,只有簡單的發(fā)送與接收說法,減少了延時,允許無限制的數(shù)據(jù)

2020-11-05 17:40:36 2826

2826

在 AMBA 系列之 AXI 總線協(xié)議初探 中,了解到 AXI 總線交互分為 Master / Slave 兩端,而且標準的 AXI 總線支持不同的位寬,既然是總線,那么必須要支持總線互聯(lián),多 Master,多 Slave的場景

2021-02-23 06:57:00 45

45 本系列我想深入探尋 AXI4 總線。不過事情總是這樣,不能我說想深入就深入。當前我對 AXI總線的理解尚談不上深入。但我希望通過一系列文章,讓讀者能和我一起深入探尋 AXI4。

2021-03-17 21:40:29 25

25 AXI是個什么東西呢,它其實不屬于Zynq,不屬于Xilinx,而是屬于ARM。它是ARM最新的總線接口,以前叫做AMBA,從3.0以后就稱為AXI了。

2021-04-09 17:10:10 4970

4970

學習內(nèi)容 近期設(shè)計需要用到AXI總線的IP,所以就對應(yīng)常用的IP進行簡要的說明,本文主要對AXI互聯(lián)IP進行介紹。 基礎(chǔ)架構(gòu)IP 基礎(chǔ)的IP是用于幫助組裝系統(tǒng)的構(gòu)建塊。基礎(chǔ)架構(gòu)IP往往是一個通用IP

2021-05-11 14:52:55 5612

5612

本系列我想深入探尋 AXI4 總線。不過事情總是這樣,不能我說想深入就深入。當前我對 AXI總線的理解尚談不上深入。但我希望通過一系列文...

2022-02-07 11:36:33 4

4 XI4-Stream跟AXI4的區(qū)別就是AXI4-Stream去除了地址線,這樣就不涉及讀寫數(shù)據(jù)的概念了,只有簡單的發(fā)送與接收說法,減少了延時。由于AXI4-Stream協(xié)議(amba4_axi4_stream_v1_0_protocol_spec.pdf)沒有時序圖,

2022-06-23 10:08:47 1781

1781 AXI4 是一種高性能memory-mapped總線,AXI4-Lite是一只簡單的、低通量的memory-mapped 總線,而 AXI4-Stream 可以傳輸高速數(shù)據(jù)流。從字面意思去理解

2022-07-04 09:40:14 5818

5818 您是否想創(chuàng)建自己帶有 AXI4-Lite 接口的 IP 卻感覺無從著手?本文將為您講解有關(guān)如何在 Vitis HLS 中使用 C 語言代碼創(chuàng)建 AXI4-Lite 接口的基礎(chǔ)知識。

2022-07-08 09:40:43 1232

1232 前面簡單學習了關(guān)于GPIO的操作,本次將使用PL 端調(diào)用 AXI GPIO IP 核, 并通過 AXI4-Lite 接口實現(xiàn) PS 與 PL 中 AXI GPIO 模塊的通信。

2022-07-19 17:36:52 3230

3230 在 AXI 基礎(chǔ)第 6 講 - Vitis HLS 中的 AXI4-Lite 簡介中,使用 C 語言在 HLS 中創(chuàng)建包含 AXI4-Lite 接口的 IP。在本篇博文中,我們將學習如何導(dǎo)出 IP

2022-08-02 09:43:05 579

579

本系列我想深入探尋 AXI4 總線。不過事情總是這樣,不能我說想深入就深入。當前我對 AXI總線的理解尚談不上深入。但我希望通過一系列文章,讓讀者能和我一起深入探尋 AXI4。

2022-08-29 14:58:44 1272

1272 Xilinx vivado下通常的視頻流設(shè)計,都采用Vid In to axi4 stream --> VDMA write --> MM --> VDMA read -->

2022-10-11 14:26:03 4556

4556 上面兩圖的區(qū)別是相比AXI3,AXI4協(xié)議需要確認AWVALID、AWREADY握手完成才能回復(fù)BVALID。為什么呢?

2023-03-30 09:59:49 668

668 AXI4 協(xié)議定義了五個不同的通道,如 AXI 通道中所述。所有這些通道共享基于 VALID 和 READY 信號的相同握手機制

2023-05-08 11:37:50 700

700

AMBA AXI協(xié)議支持高性能、高頻系統(tǒng)設(shè)計。

2023-05-24 15:05:12 689

689

上文FPGA IP之AXI4協(xié)議1_協(xié)議構(gòu)架對協(xié)議框架進行了說明,本文對AXI4接口的信號進行說明。

2023-05-24 15:05:46 842

842

上文FPGA IP之AXI4協(xié)議1_信號說明把AXI協(xié)議5個通道的接口信息做了說明,本文對上文說的信號進行詳細說明。

2023-05-24 15:06:41 669

669

AXI4協(xié)議是ARM的AMBA總線協(xié)議重要部分,ARM介紹AXI4總線協(xié)議是一種性能高,帶寬高,延遲低的總線協(xié)議。

2023-06-19 11:17:42 2097

2097

AXI4協(xié)議是一個點對點的主從接口協(xié)議,數(shù)據(jù)可以同時在主機(Master)和從機(Slave)之間**雙向** **傳輸** ,且數(shù)據(jù)傳輸大小可以不同。

2023-06-21 15:26:43 1388

1388

在 Vivado 中自定義 AXI4-Lite 接口的 IP,實現(xiàn)一個簡單的 LED 控制功能,并將其掛載到 AXI Interconnect 總線互聯(lián)結(jié)構(gòu)上,通過 ZYNQ 主機控制,后面對 Xilinx 提供的整個 AXI4-Lite 源碼進行分析。

2023-06-25 16:31:25 1914

1914

可以看到,在AXI到UART中,是通過寄存器和FIFO進行中介的。因為從AXI總線往里看,其控制的是就是地址上所映射的寄存器。

2023-06-27 10:12:53 2229

2229

Xilinx 從 Spartan-6 和 Virtex-6 器件開始采用高級可擴展接口 (AXI) 協(xié)議作為知識產(chǎn)權(quán) (IP) 內(nèi)核。Xilinx 繼續(xù)將 AXI 協(xié)議用于針對 7 系列和 Zynq-7000 All Programmable SoC 器件的 IP。

2023-09-27 09:50:27 594

594

中的一個參數(shù)來選擇。 集成設(shè)計環(huán)境(IDE)。AXI數(shù)據(jù)總線的寬度可定制。該IP可通過AXI4互連驅(qū)動AXI4-Lite或AXI4內(nèi)存映射從站。運行時間與該內(nèi)核的交互需要使用Vivado邏輯分析器功能。

2023-10-16 10:12:42 410

410

以AXI4為例,有AXI full/lite/stream之分。 在Xilinx系列FPGA及其有關(guān)IP核中,經(jīng)常見到AXI總線接口,AXI總線又分為三種: ?AXI-Lite,AXI-Full以及

2023-10-31 15:37:08 386

386

本文主要集中在AMBA協(xié)議中的AXI4協(xié)議。之所以選擇AXI4作為講解,是因為這個協(xié)議在SoC、IC設(shè)計中應(yīng)用比較廣泛。

2024-01-17 12:21:22 224

224

電子發(fā)燒友App

電子發(fā)燒友App

評論