一、FPGA設計流程

?

FPGA設計流程是利用EDA開發軟件和編程工具對FPGA芯片進行開發的過程。FPGA的設計流程如上圖所示:包括設計定義、代碼實現、功能仿真、邏輯綜合、前仿真、布局布線、后仿真和板級調試等步驟!

1.設計定義

設計定義階段主要進行方案驗證、系統設計和FPGA芯片選擇等準備工作。根據任務要求,評估系統的指標和復雜度,對工作速度和芯片本身的資源、成本等方面進行權衡,選擇合理的設計方案和合適的器件類型。

這個階段往往會花費大量的時間,這個階段之后一般已經完成了系統建模,功能劃分,模塊劃分以及設計文檔的撰寫等工作。

2.代碼實現

代碼實現階段是將劃分好的各功能模塊用硬件描述語言表達出來,常用的硬件描述語言有Verilog HDL和VHDL。以后的教程中我們主要講解如何使用Verilog HDL進行FPGA設計。

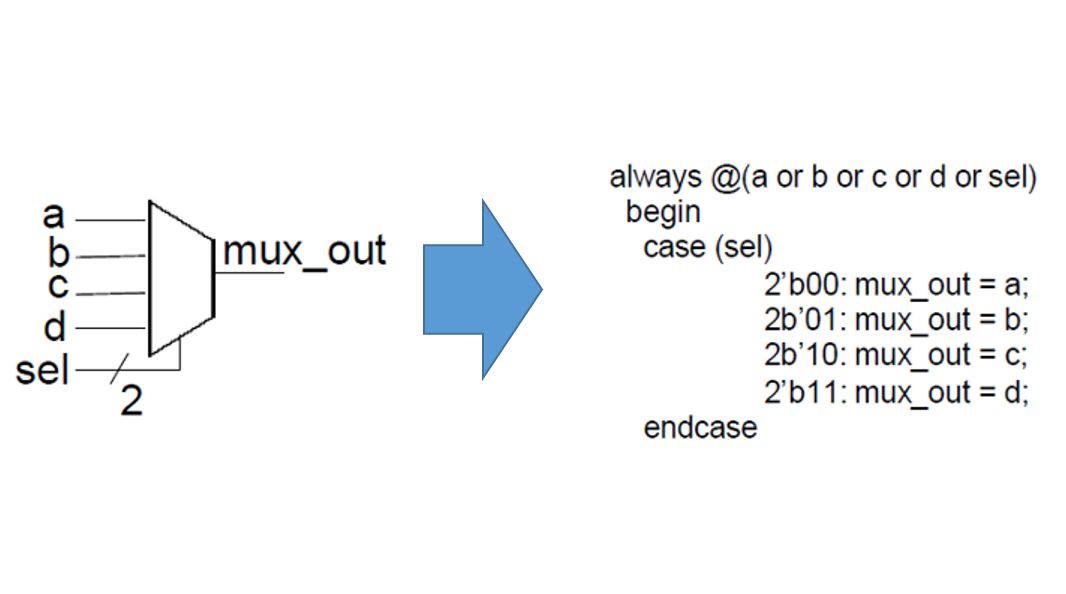

下面是一個四選一電路的代碼實現過程:

常用的代碼編輯器軟件由notepad++和UltralEdit等,它們支持幾乎所有主流編程語言的高亮顯示、代碼補全、自定義快捷鍵等功能,外觀漂亮、功能強大,擴展性強,具有豐富的插件包,極大的提高工作效率。

3.功能仿真

功能仿真是在編譯之前對用戶所設計的電路進行邏輯功能驗證,此時的仿真沒有延遲信息,僅對初步的功能進行檢測。這里我們補充一個延遲類型的知識點

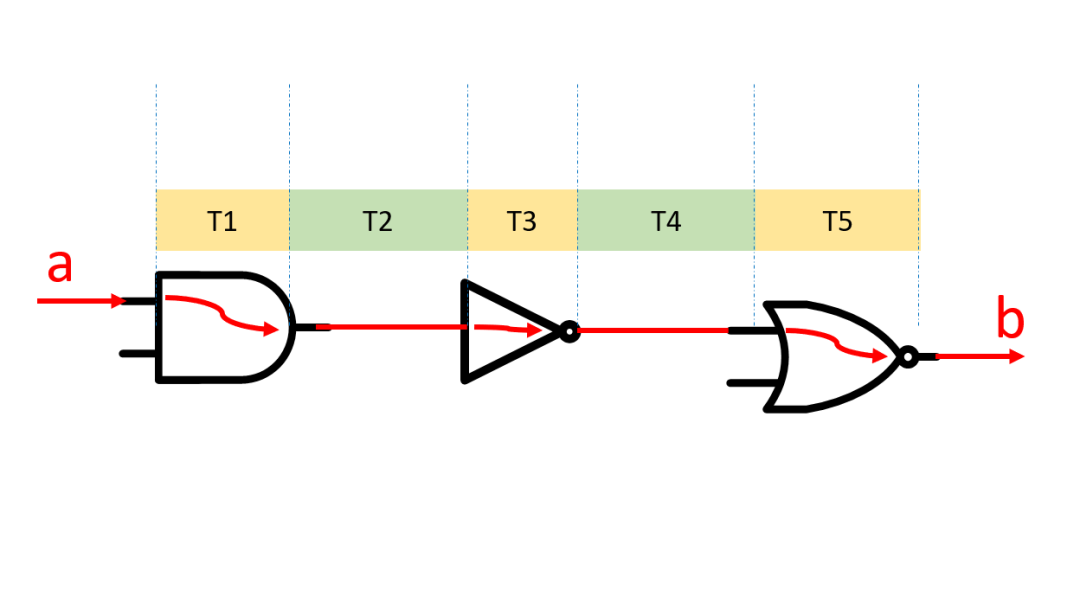

我們知道信號在電路中傳輸時會有兩種延遲:器件延遲和路徑延遲。顧名思義,器件延遲是信號在經過器件傳輸時的延遲時間,路徑延遲是信號經過連接線時的延遲時間。上圖中信號從a到b的延遲時間為T1+T2+T3+T4+T5,其中器件延遲是T1、T3、T5,路徑延遲是T2、T4。在功能仿真中,這些延遲信息都為零。

4.邏輯綜合

邏輯綜合的概念是:將高級抽象層次的描述轉化成較低層次的描述。

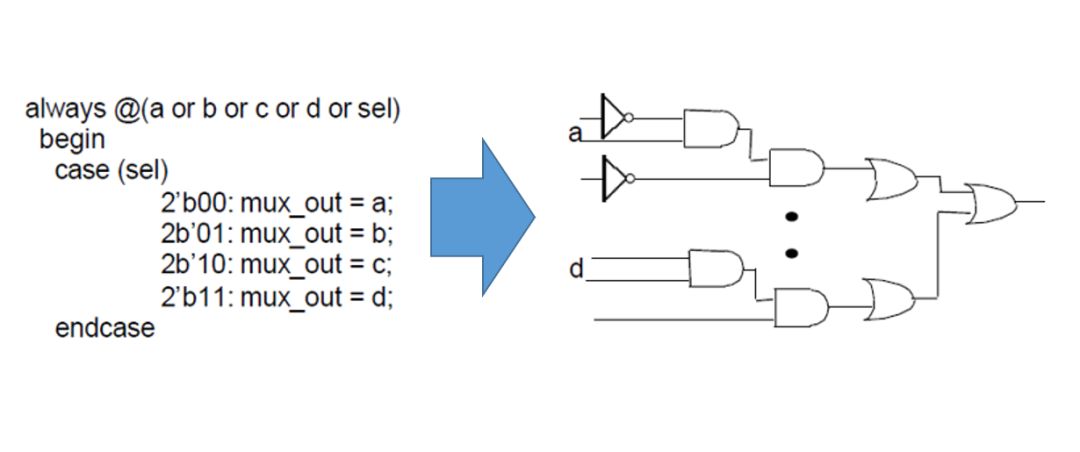

也就是說將語言描述的電路邏輯轉化成與門、或門、非門、觸發器等基本邏輯單元的互連關系。

還是以四選一電路為例,綜合過程將Verilog代碼翻譯成了門級互連網表。

綜合的概念很重要,利用Verilog 做電路設計時我們總是強調可綜合的概念,可綜合就是我們的這段代碼可以被翻譯成門級網表,不可綜合就是代碼不能被翻譯成門級網表。

5.前仿真

前仿真也叫做綜合后仿真,仿真時,把綜合生成的標準延時文件反標注到綜合仿真模型中去。

因為綜合后只能體現基本的邏輯門之間的互連關系,并沒有連線長度信息,所以前仿真只能評估門延時帶來的影響,不能估計路徑延時,前仿真結果和布線后實際情況還有一定的差距,并不十分準確。

目前的綜合工具較為成熟,一般的設計可以省略這一步。但如果布局布線后發現電路功能與設計意圖不符,就需要回溯到前仿真來確定問題所在。

6.布局布線

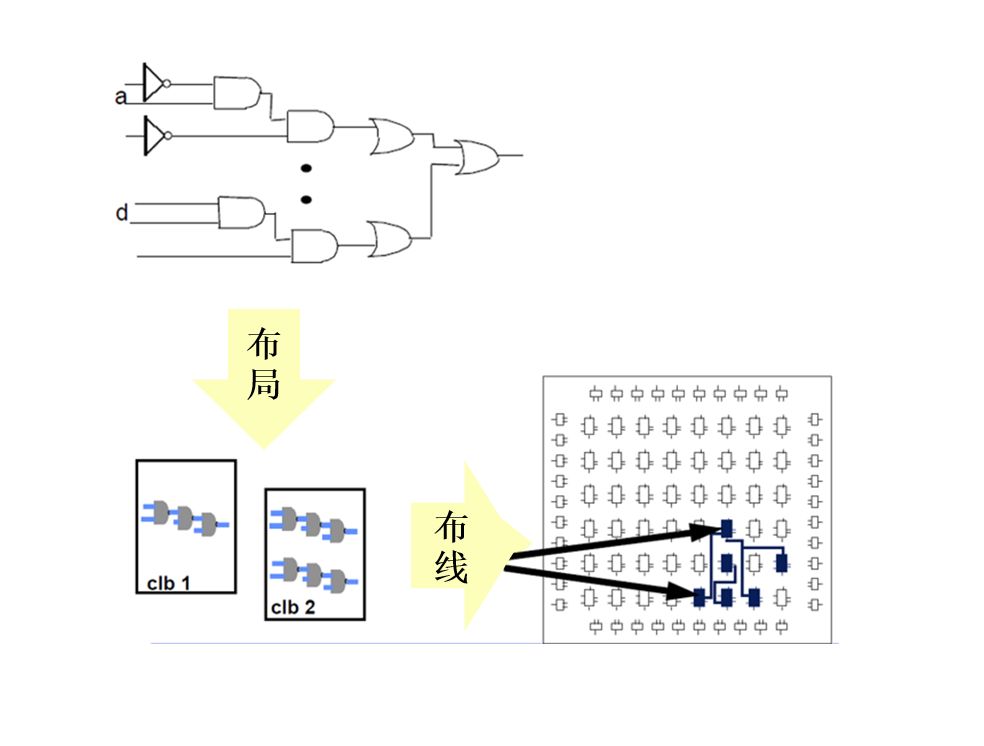

布局布線有時也叫作實現與布局布線,布局布線是將邏輯網表中的門級連接關系配置到FPGA芯片內部的固有硬件結構上。

布局布線的過程是先將綜合后的基本邏輯門映射到FPGA的可編程邏輯塊(CLB)中(上一講中我們知道FPGA中許許多多的CLB組成了巨大的邏輯資源陣列,CLB是FPGA可配置的基礎),相關的邏輯配置在臨近的CLB中,這就是一個布局的過程;

布線是利用FPGA中豐富的布線資源將CLB根據邏輯關系連接在一起。

布局布線策略有兩種:速度優先和面積優先,布局布線時往往需要在速度最優和面積最優之間做出選擇。

7.后仿真

后仿真也稱為時序仿真,是將布局布線的延時信息反標注到設計網表中來檢測有無時序違規。

經過布局布線后,門與門之間的連線長度也確定了,所以后仿真包含的延遲信息最全,也最精確,能更好的反映芯片的額實際工作情況。

現在我們可以總結一下功能仿真、前仿真和后仿真的區別了:

功能仿真:無延遲信息;

前仿真:只有門級的延遲;

后仿真:門級延遲和連線延遲;

8.板級調試

我們的FPGA設計不能只在電腦上跑仿真,最終還是要在電路板上應用起來的,設計的最后一步就是板級測試了,將EDA軟件產生的數據文件(位數據流文件)下載到FPGA芯片中,進行實際的測試。

FPGA工程師還需要有一定的硬件知識,能夠看懂電路板原理圖設計和PCB是最低要求了,能夠獨立設計原理圖是最好的了。

打個比方。。。

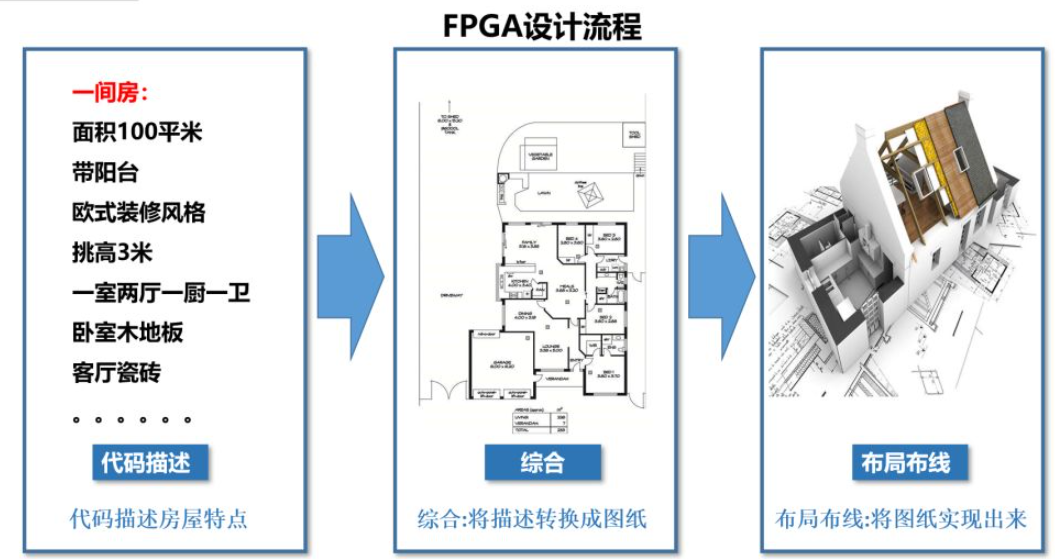

為了方便初學者門能更快的了解FPGA的設計流程,我舉了一個栗子,請看下圖:

代碼實現,綜合和布局布線時FPGA設計流程中的幾個關鍵步驟,下面我們打個比方加深理解一下這幾個步驟是干什么的:

代碼實現:比如我要蓋一座房子,我把房子的特點描述出來:比如面積100平米、帶陽臺、歐式裝修風格、挑高3米、一室兩廳一廚一衛、臥室木地板客廳瓷磚。。。等等要求,這個描述房屋特點的過程就好比我們用Verilog描述電路功能的過程。

邏輯綜合:建筑師根據我們的要求畫出施工圖紙,施工圖紙將我的需求數字化、具體化,比如這個墻有多高,門有多寬,窗戶面積等等,這個過程就好比綜合的過程,將需求翻譯成具體的數字圖紙,只不過綜合是將電路功能翻譯成門級網表,建筑師干的活就是綜合工具軟件干的活。

布局布線:工人拿會根據圖紙進行施工,用磚、水泥、鋼筋、木材等建造符合圖紙標準的房子。圖紙規定了一面墻,但是沒有規定具體用哪一塊磚來砌墻,工人可以自主決定用哪些磚。布局布線是根據綜合后的網表文件(施工圖紙),利用FPGA芯片內部的可編程邏輯塊(CLB),布線資源,時鐘資源,存儲資源等搭建電路的過程。

綜合和布局布線的過程中會涉及到約束策略的問題,比如管腳約束、時鐘約束、面積和速度優先級等。這些概念在蓋房子的過程中也有對應,比如你可以跟建筑師要求陽臺大小、臥室朝向、門窗高度等,采購建筑材料時,你也會控制成本和質量之間的平衡。這些都是類似于綜合和布局布線過程中的約束條件。

二、FPGA廠家、產品系列及設計軟件介紹

1.FPGA廠家

近幾年,全球半導體行業的關鍵詞就是:收購、兼并、重組,FPGA領域也發生了不小的變化。

目前,全球FPGA市場高度集中,被美國四家企業壟斷,呈現出“兩大兩小”的市場格局。“兩大”是指Xilinx(賽靈思)和Intel(因特爾),“兩小”是指Microsemi(美高森美)和Lattice(萊迪思),前兩大企業占據近90%的市場份額。

其中Intel的FPGA業務是收購自Altera公司的,現在的Microsemi是在2010年收購Actel后合并而來的。

2015年Lattice以6億美元收購Silicon Image公司;基于保護國家戰略資產的考慮,16年底美國總統特朗普下達行政指令,宣布停止具有中資背景的私募股權基金(Canyon Bridge)收購美國FPGA芯片制造商Lattice(萊迪思)的交易,要求買賣雙方完全、永久性地放棄收購。

“兩小”廠家主攻的是特殊市場,比如軍工、航天市場所用的反熔絲FPGA。反熔絲FPGA價格十分昂貴,只能燒錄一次,抗輻照能力比較強。

初學者學習Xilinx(賽靈思)和Intel(因特爾)家的FPGA就可以,官網資料比較多,開發板相對便宜。

2.FPGA產品系列

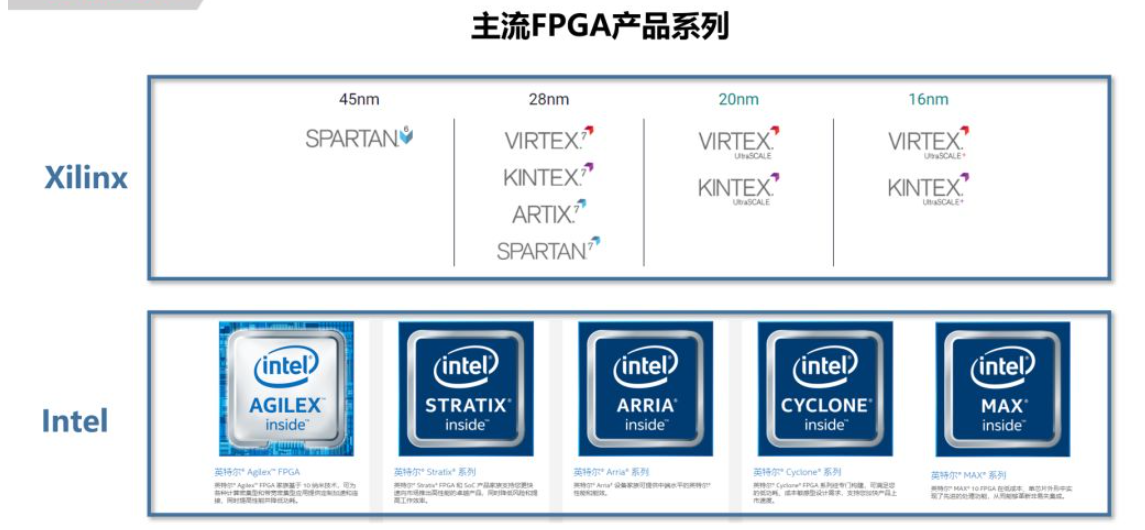

我們只介紹Xilinx(賽靈思)和Intel(因特爾)的FPGA產品系列,另外兩家小眾的FPGA就不介紹了。

上面圖片中的產品系列是從兩家FPGA廠家官網上找到的當前在售的產品系列。

Xilinx:工具工藝制程,可以分為6系(45nm)、7系(28nm)、UltraSCALE(20nm)、UltraSCALE+(16nm),按照型號系列還可以分為Spartan、Artix、Kintex、Virtex等系列,另外還有嵌入式系統開發的Zynq系列。

Intel:Intel目前在售的FPGA產品系列主要有MAX系列、Cyclone系列、Arria系列、Stratix系列、Agilex系列以及SoC FPGA系列產品。

3.設計軟件

學習FPGA一定要學習FPGA的設計思想以及設計原理,不要糾結于單一的實驗平臺或者操作軟件,因為你想在這個行業越走越高的話,廣度和深度都是要有所了解的,初期學習的時候尤其注重動手,選擇一款操作平臺以及操作軟件是為了讓你更好的去動手做,而不是讓你在這款軟件或者實驗平臺去做文章,因為不懂原理的話,換個環境你同樣是什么都不明白。

FPGA設計軟件的使用和FPGA的設計流程是一致的,所以學會了使用其中的一種軟件,再去使用另外的一款軟件也能很快上手。

Xilinx設計軟件

Xilinx目前開發工具包括ISE和Vivado,

ISE design suite 支持 Spartan-6、 Virtex-6、和 CoolRunner 器件,及其上一代器件系列。

Xilinx 推薦 Vivado Design Suite ,針對 Virtex-7、Kintex-7、Artix-7、和 Zynq-7000 起的全新設計。

FPGA廠家的開發工具都有第三方仿真平臺的接口,調用最多的第三方仿真軟件就是Modelsim,ISim是ISE自身集成的仿真工具,兩者功能差不多。用modelsim的人比較多,然后教程也多,容易學。跑大型的工程,Modelsim快很多。所以我們在以后的教程中使用Modelsim演示。

Intel設計軟件

Intel的FPGA軟件是Quartus,目前最新的版本已經到了19版本。

分為3個版本:

英特爾 Quartus Prime 精簡版

英特爾 Quartus Prime 標準版

英特爾 Quartus Prime 專業版

其中精簡版是免費的,無需付費許可,而且內置了modelsim仿真軟件。

編輯:黃飛

電子發燒友App

電子發燒友App

評論