基于VIVADO的PCIE IP的使用

項(xiàng)目簡(jiǎn)述

上一篇內(nèi)容我們已經(jīng)對(duì)PCIE協(xié)議進(jìn)行了粗略的講解。那么不明白具體的PCIE協(xié)議,我們就不能在FPGA中使用PCIE來(lái)進(jìn)行高速數(shù)據(jù)傳輸了嗎?答案是否定的。因?yàn)閄ilinx官方給我們提供了完善的PCIE IP,基于這些IP我們?cè)O(shè)置不需要知道TLP包的組包原理我們便可以把PCIE使用起來(lái)。這篇博客我們主要把FPGA作為endpoint來(lái)進(jìn)行講解,當(dāng)然也對(duì)作為root port進(jìn)行簡(jiǎn)單的描述。我們使用的主要IP是XDMA,主要參考資料是米聯(lián)客。如果對(duì)IP的使用感覺(jué)到疑惑可以參考米聯(lián)客的資料。

因?yàn)槭诸^上硬件條件不夠,沒(méi)辦法進(jìn)行下板測(cè)試,我們主要進(jìn)行介紹IP的定制和Block Design的搭建。

XDMA IP的定制

為什么使用XDMA IP而不使用我們前面介紹的PCIE IP,因?yàn)榍懊娼榻B的IP需要我們自己構(gòu)建TLP包,還有分散收集策略,基于該IP使用起來(lái)PCIE還是有點(diǎn)困難。但是XDMA就特別簡(jiǎn)單了,他不需要FPGA設(shè)計(jì)者熟悉PCIE協(xié)議,直接將PCIE協(xié)議轉(zhuǎn)換成AXI4與AXI_Lite協(xié)議,可以直接對(duì)DDR進(jìn)行操作。XDMA內(nèi)部的分散收集操作、TLP組包、DMA操作等等進(jìn)行了完整的封裝。我們可以把XDMA IP看成我們經(jīng)常使用的ZYNQ IP,他的BAR空間被AXI_Lite總線進(jìn)行讀寫(xiě)操作用于寄存器的配置,AXI總線用于大數(shù)據(jù)的傳輸直接與DDR對(duì)接。

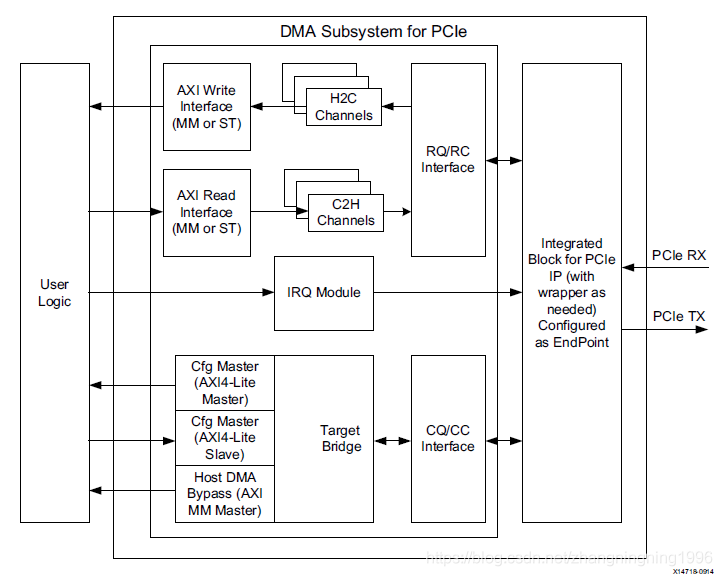

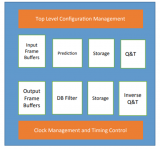

XDMA的內(nèi)部額框圖如下:

對(duì)XDMA的內(nèi)部描述如下:

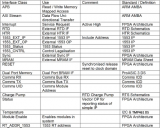

1、AXI4、 AXI4-Stream,必須選擇其中一個(gè),用來(lái)數(shù)據(jù)傳輸

2、 AXI4-Lite Master,可選,用來(lái)實(shí)現(xiàn)PCIE BAR 地址到 AXI4-Lite 寄存器地址的映射,可用來(lái)讀寫(xiě)用戶邏輯寄存器

3、 AXI4-Lite Slave,可選,用來(lái)將XDMA 內(nèi)部寄存器開(kāi)放給用戶邏輯,用戶邏輯可以通過(guò)此接口訪問(wèn) XDMA內(nèi)部寄存器,不會(huì)映射到BAR

4、AXI4 Bypass 接口,可選,用來(lái)實(shí)現(xiàn)PCIE 直通用戶邏輯訪問(wèn),可用于低延遲數(shù)據(jù)傳輸

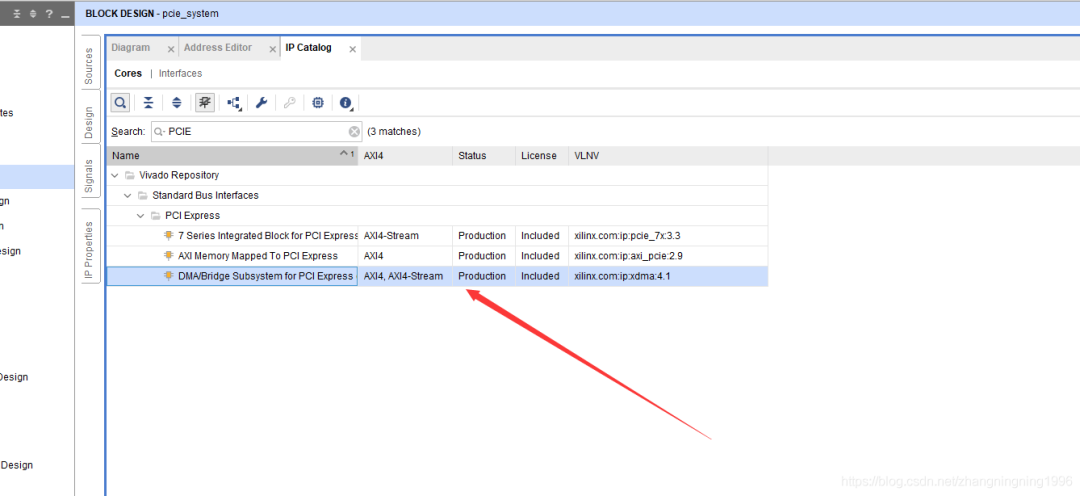

首先選擇XDMA IP如下:

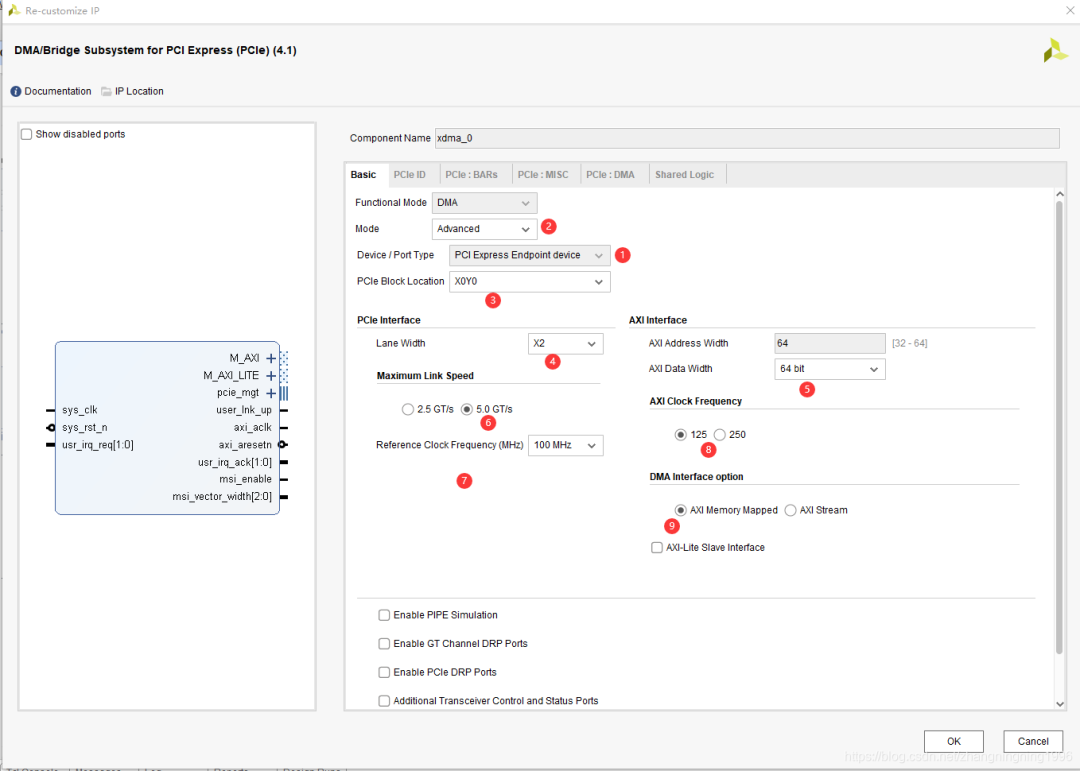

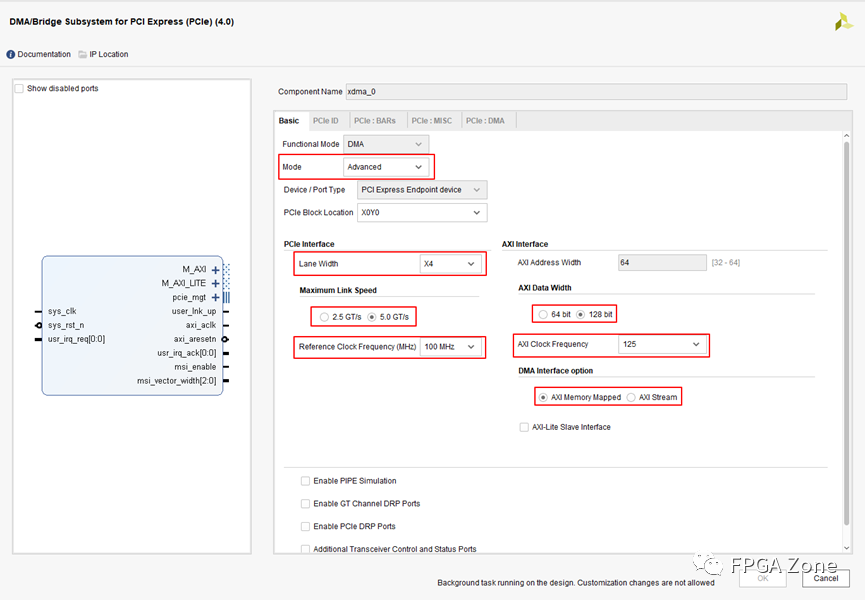

雙擊點(diǎn)開(kāi)該IP的配置:

1、該IP是作為Endpoint來(lái)進(jìn)行PCIE操作的

2、IP定制的模式是高級(jí),這樣一來(lái)可供選擇的IP定制選項(xiàng)就會(huì)增多

3、PCIE硬核的位置,這里我們的芯片只有一個(gè)硬核,所以這里默認(rèn)即可

4、lane的個(gè)數(shù),與開(kāi)發(fā)板相對(duì)應(yīng),這里選擇2個(gè)

5、XDMA將PCIE轉(zhuǎn)換成AXI協(xié)議,這個(gè)就是AXI協(xié)議的位寬

6、該片子的高速串行接口是GTP口,支持PCIE Gen1 Gen2協(xié)議,速度分別是2.5GT/s 5GT/s,這里選擇最大速度5 GT/s

7、PCIE參考時(shí)鐘的頻率,與板子的時(shí)鐘情況有關(guān),這里是100MHz

8、AXI總線的時(shí)鐘頻率,這里我們選擇125MHz

9、這里我們直接將PCIE協(xié)議轉(zhuǎn)換成AXI協(xié)議,而不選擇AXI Stream協(xié)議,簡(jiǎn)化我們的操作

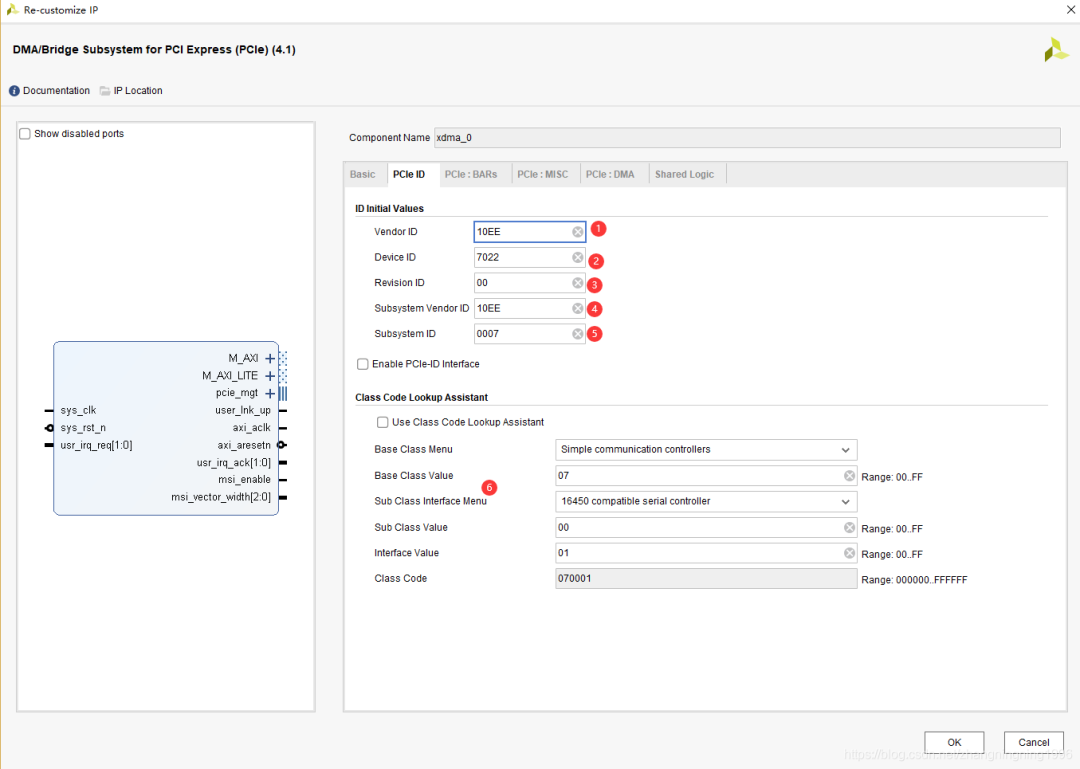

1、廠商ID,專屬于Xilinx的PCIE的ID,是固定的。

2、設(shè)備ID,與廠商ID一起指明數(shù)據(jù)的類型,被使用選擇PCIE上位機(jī)的軟件驅(qū)動(dòng)。

3、版本ID,指明使用該P(yáng)CIE IP進(jìn)行設(shè)置的版本

4、子廠商ID,用來(lái)更近一步的區(qū)分Xilinx旗下的廠商

5、子系統(tǒng)ID,用來(lái)識(shí)別板卡的的ID

6、PCIE在實(shí)驗(yàn)中承擔(dān)的角色,這里我們選擇默認(rèn)即可

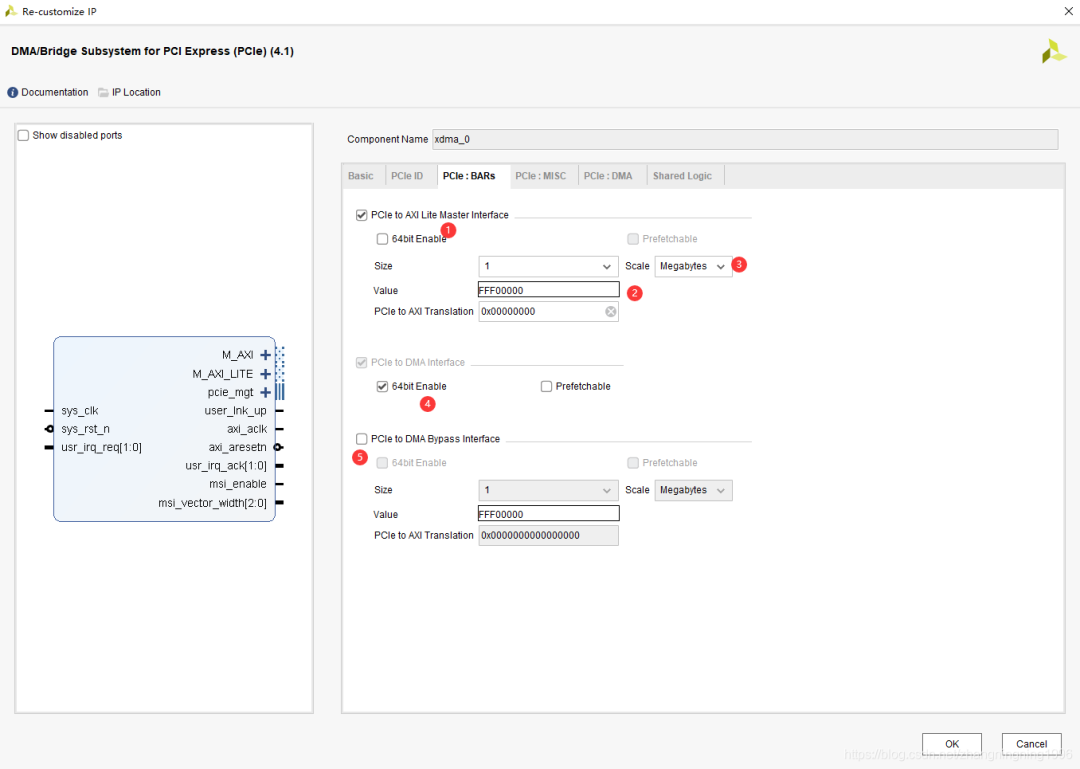

1、首先使能 PCIE to AXI Lite Master Interface ,這樣可以在主機(jī)一側(cè)通過(guò)PCIE 來(lái)訪問(wèn)用戶邏輯側(cè)寄存器或者其他AXI4-Lite 總線設(shè)備

2、主機(jī)側(cè)PCIE BAR 地址與用戶邏輯側(cè)地址是不一樣的,這個(gè)設(shè)置就是進(jìn)行BAR 地址到AXI 地址的轉(zhuǎn)換,比如主機(jī)一側(cè) BAR 地址為0, IP 里面轉(zhuǎn)換設(shè)置為 0x80000000,則主機(jī)訪問(wèn) BAR 地址 0 轉(zhuǎn)換到AXI LIte 總線地址就是0x80000000,這點(diǎn)的理解特別重要

3、選擇64bit 使能

4、用來(lái)實(shí)現(xiàn)PCIE 直通用戶邏輯訪問(wèn),可用于低延遲數(shù)據(jù)傳輸,這里不選擇。

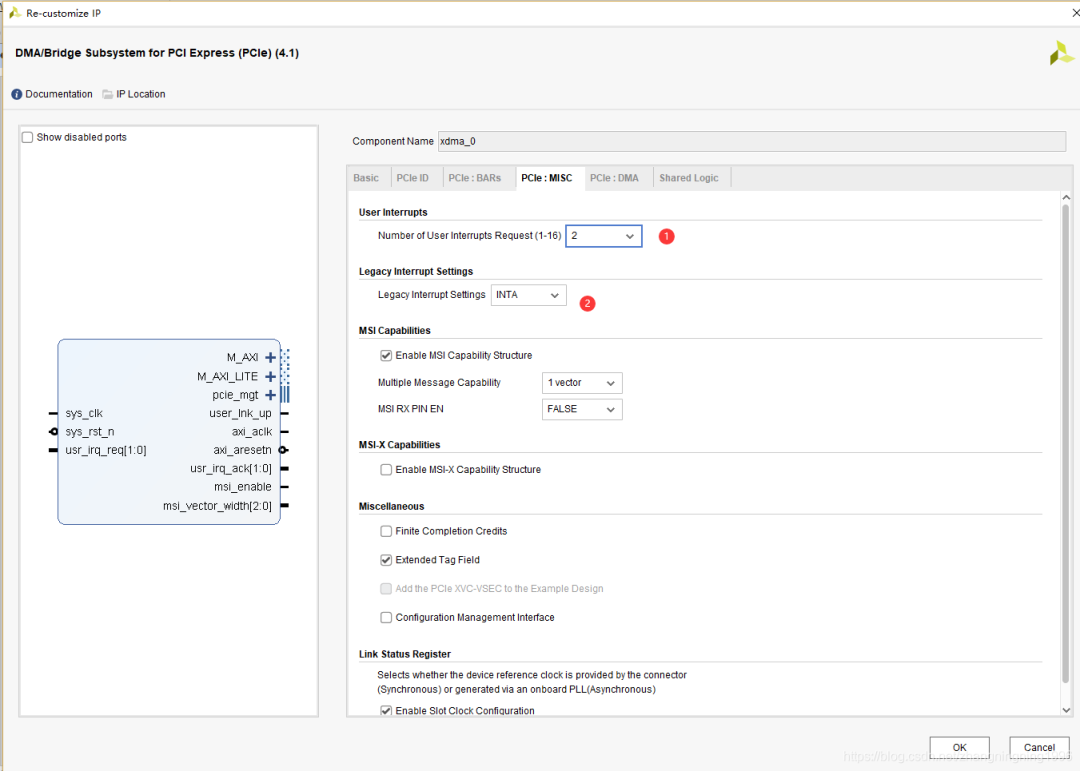

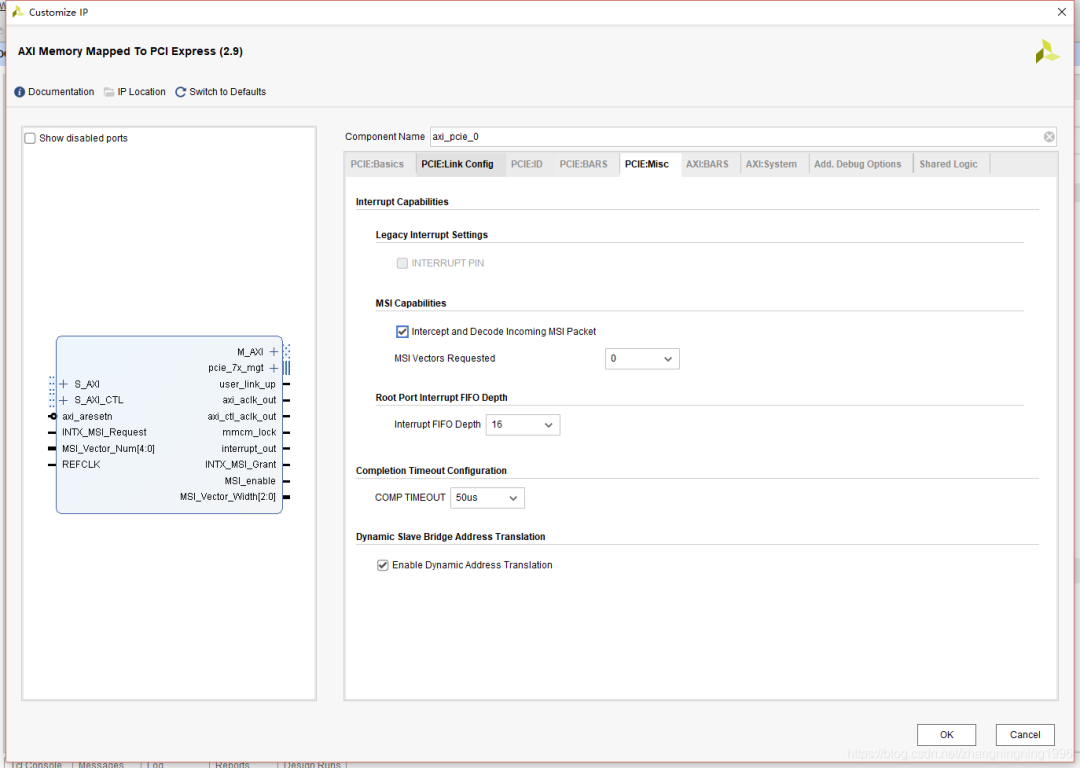

1、選擇消息中斷,因?yàn)橄旅娴墓こ讨惺褂昧?個(gè)中斷,所以這里我們選擇2

2、引腳中斷,這里選不選擇意義不大

其余的默認(rèn)設(shè)置即可。

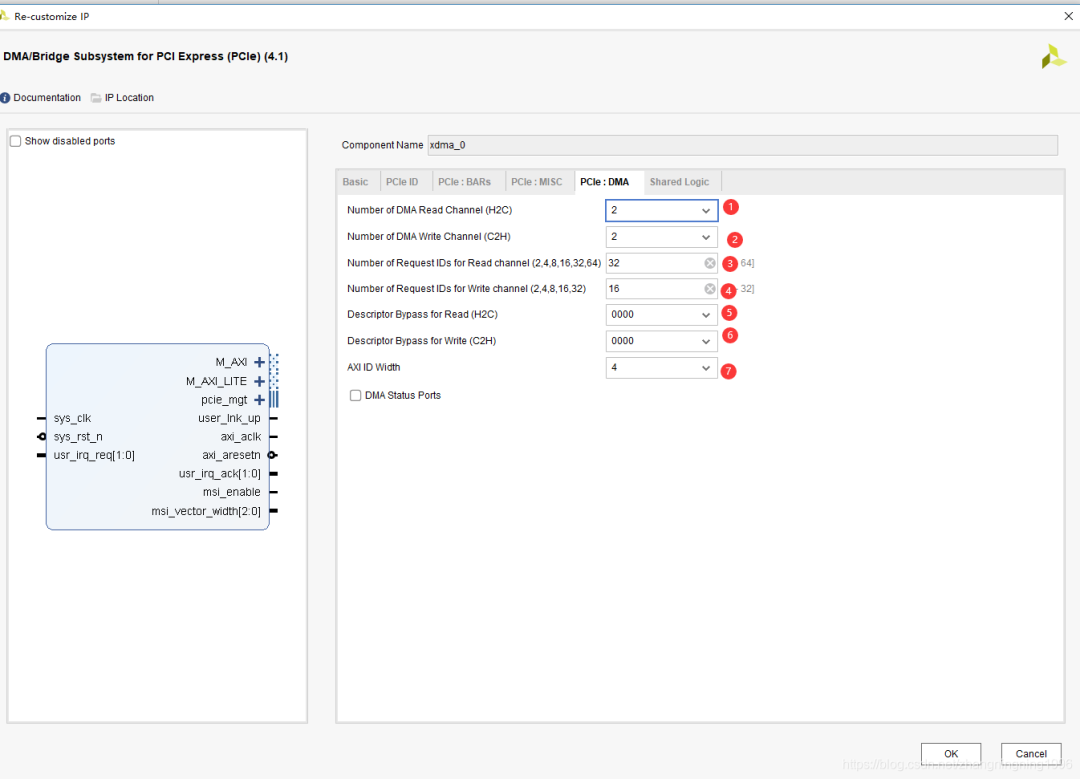

1、2、Number of DMA Read Channel(H2C)和Number of DMA Write Channel(C2H)通道數(shù),對(duì)于PCIE2.0 來(lái)說(shuō)最大 只能選擇 2,也就是 XDMA 可以提供最多兩個(gè)獨(dú)立的寫(xiě)通道和兩個(gè)獨(dú)立的讀通道,獨(dú)立的通道對(duì)于實(shí)際應(yīng)用中 有很大的作用,在帶寬允許的前提前,一個(gè)PCIE 可以實(shí)現(xiàn)多種不同的傳輸功能,并且互不影響。這里我們選擇1。

其余的默認(rèn)即可。

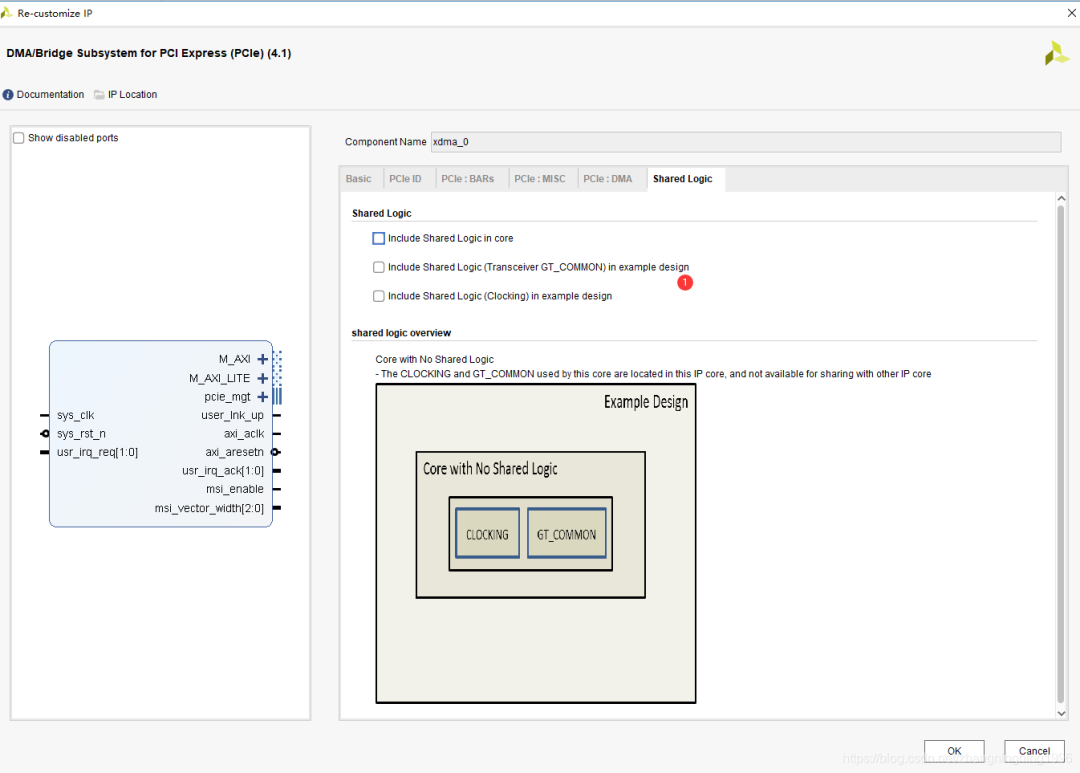

這里我們不共享任何邏輯。

經(jīng)過(guò)上面的設(shè)置,我們已經(jīng)定制了常規(guī)的XDMA IP,接下來(lái)講解常用的Block Design設(shè)計(jì)。

PCIE Endpoint的工程框圖

這里我們使用米聯(lián)客中的一個(gè)例子,個(gè)人認(rèn)為這是上面最難的例子了,涉及到了XDMA中斷的使用。(這里只做粗略介紹,想詳細(xì)學(xué)習(xí)的還是得看米聯(lián)客官方的資料)

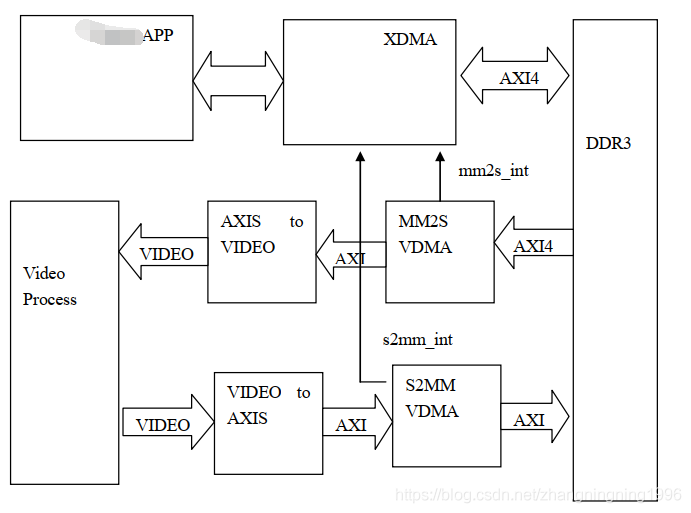

本例子主要講述基于 PCIE XDMA IP 實(shí)現(xiàn)的一個(gè)圖像傳輸應(yīng)用,圖像的數(shù)據(jù)流控制主要用到了 VDMA IP。整個(gè)項(xiàng)目的框圖如下:

由上圖可以看出,圖像數(shù)據(jù)是由 PC 端產(chǎn)生,然后用過(guò) XDMA 傳輸?shù)?ZYNQ 的 DDR3(通過(guò) HP 接口),數(shù)據(jù)再經(jīng)過(guò)一個(gè) MM2S 的 VDMA 從 ZYNQ 的 DDR(通過(guò) HP 接口)讀出到 AXIS 接口,經(jīng)過(guò) AXIS to VIDEO 轉(zhuǎn)換到視頻時(shí)序,可以做視頻處理,之后再經(jīng)過(guò) VIDEO to AXIS 轉(zhuǎn)換到 AXIS 接口,經(jīng)過(guò) MM2S 的 VDMA 存入 DDR, XDMA再?gòu)?DDR 將圖像數(shù)據(jù)讀出到底 PC。這里面實(shí)際上包含了兩條傳輸路徑,一條是 PCIE 到視頻,一條是視頻到 PCIE,一個(gè)工程,兩個(gè)操作例子,很有參考意義。

從上面的工程我們可以學(xué)到,F(xiàn)PGA 端主要實(shí)現(xiàn)如下功能

1、 XDMA 與 DDR 數(shù)據(jù)通信

2、 VDMA 實(shí)現(xiàn)視頻數(shù)據(jù)搬運(yùn)

3、 可編程 VTC(Video Timing Control)模塊,提供視頻時(shí)序功能

4、 AXIS to Video 模塊,實(shí)現(xiàn) axis 到視頻時(shí)序的轉(zhuǎn)換

5、 圖像處理模塊,用戶可自定義圖像處理功能,例程中實(shí)現(xiàn)彩色圖像的飽和度調(diào)整算法

6、 Video to AXIS 模塊,實(shí)現(xiàn)視頻時(shí)序到 AXIS 的轉(zhuǎn)換

7、 用戶邏輯寄存器模塊,可橋接到 XDMA,實(shí)現(xiàn)上位機(jī)通過(guò) XDMA 對(duì) FPGA 的寄存器控制

8、 讀取本地圖像生成圖像傳輸鏈表

9、 通過(guò) VDMA 的 MM2S 中斷來(lái)從 WIN64 傳輸圖像到 FPGA DDR

10、通過(guò) VDMA 的 S2MM 中斷來(lái)從 FPGA DDR 獲取圖像數(shù)據(jù),這些中斷是經(jīng)過(guò)XDMA傳輸?shù)缴衔粰C(jī)

關(guān)于可以學(xué)到的XDMA部分我們已經(jīng)加粗。

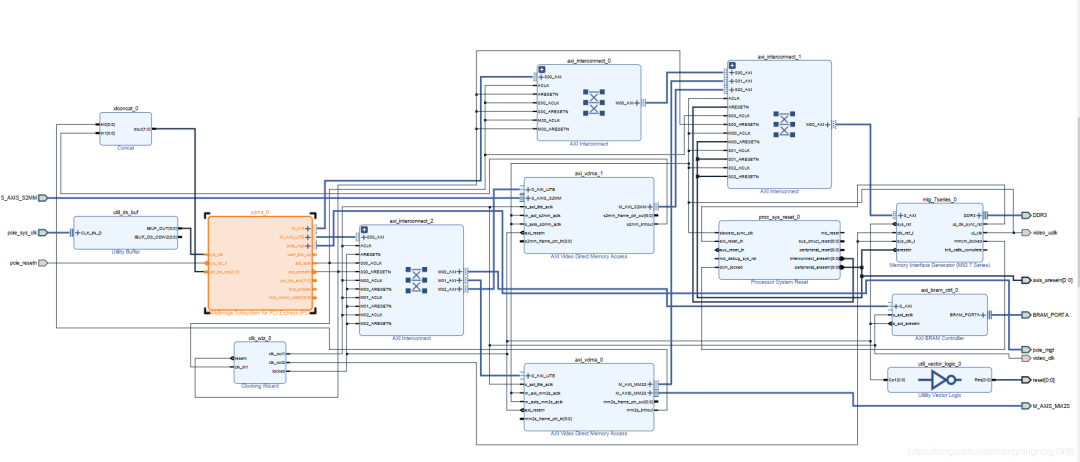

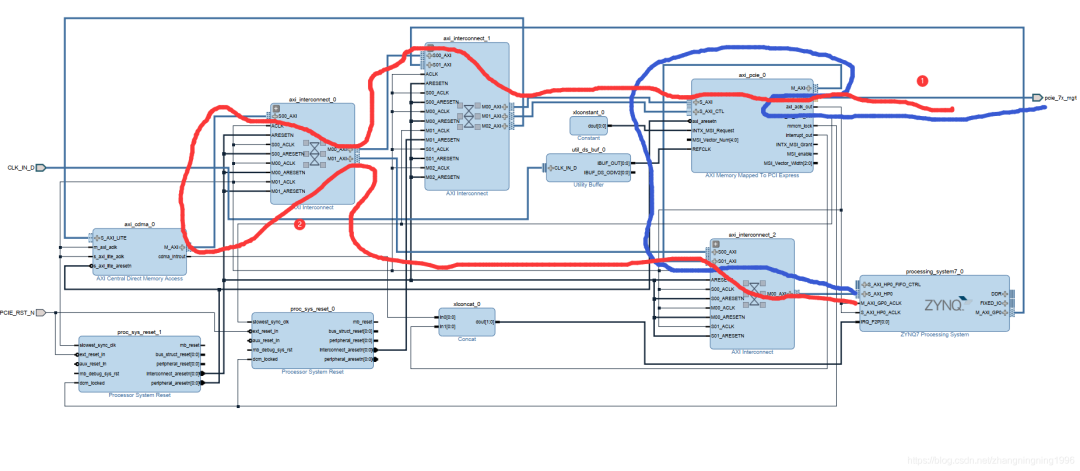

項(xiàng)目的Block Design設(shè)計(jì)圖如下:

這里主要介紹一下XDMA在上面的Block Design設(shè)計(jì)中起到的作用。

1、使用PCIE轉(zhuǎn)AXI的總線將圖像數(shù)據(jù)存儲(chǔ)到DDR、將DDR中的數(shù)據(jù)搬移到DDR中

2、通過(guò)AXI_Lite接口來(lái)配置兩個(gè)VDMA的IP,使其能夠正常工作起來(lái),配置數(shù)據(jù)是PC機(jī)發(fā)送來(lái)的數(shù)據(jù)

3、通過(guò)AXI_Lite接口來(lái)配置Bram,通過(guò)這個(gè)ram來(lái)與PC機(jī)進(jìn)行一定的數(shù)據(jù)交互,解決圖像斷幀的現(xiàn)象

4、通過(guò)兩個(gè)VDMA的中斷信號(hào)使得XDMA產(chǎn)生中斷信號(hào),告訴PC機(jī)進(jìn)行一定的處理

上面的Block Design的設(shè)計(jì),我們只講解了XDMA的作用,至于VDMA的作用,這里不再講解,因?yàn)閭€(gè)人認(rèn)為VDMA IP還是有點(diǎn)雞肋,因?yàn)樾枰M(jìn)行配置、數(shù)據(jù)也需要上游模塊主動(dòng)進(jìn)行讀取寫(xiě)入。這個(gè)完全可以用自定義的AXI IP來(lái)代替。

如果真把上面的流程搞明白了,那么可以熟練的實(shí)現(xiàn)FPGA開(kāi)發(fā)板通過(guò)XDMA與PC機(jī)之間的通信。可以熟練掌握PCIE的使用。但是,上面的使用需要經(jīng)過(guò)上位機(jī)的配合,至于上位機(jī)的書(shū)寫(xiě),我沒(méi)有掌握的太好,就不多加解釋,這個(gè)例子在米聯(lián)客的PCIE教程中有,同學(xué)們可以去學(xué)習(xí)。

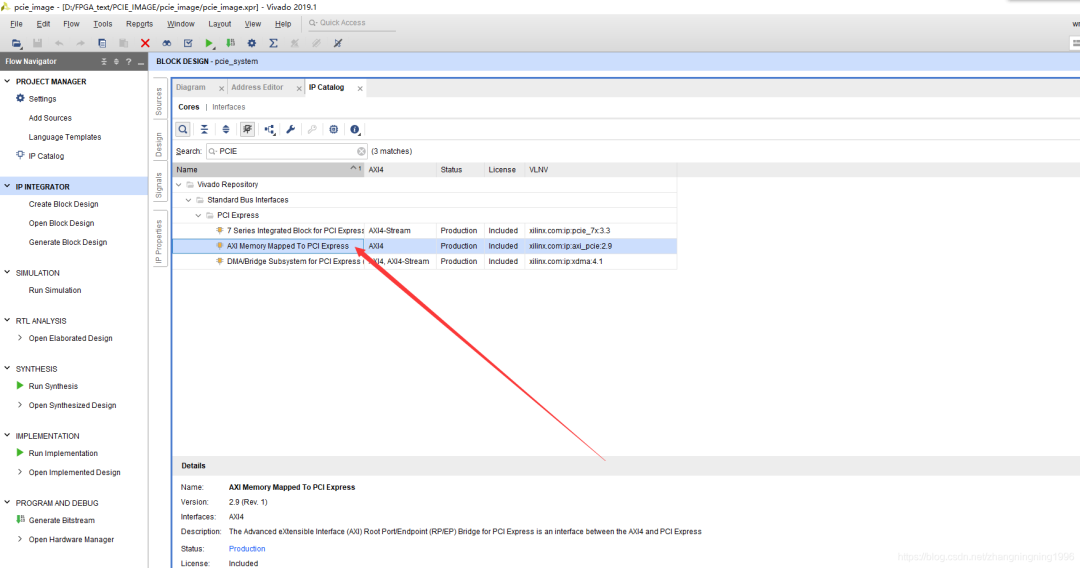

PCIE IP的定制

上面我們已經(jīng)講解了PCIE作為endpoint如何進(jìn)行配置與Block Design的搭建。接下來(lái),我們講解PCIE作為rootpoint如何來(lái)進(jìn)行PCIE的配置與Block Design的設(shè)置。

首先點(diǎn)擊PCIE IP核:

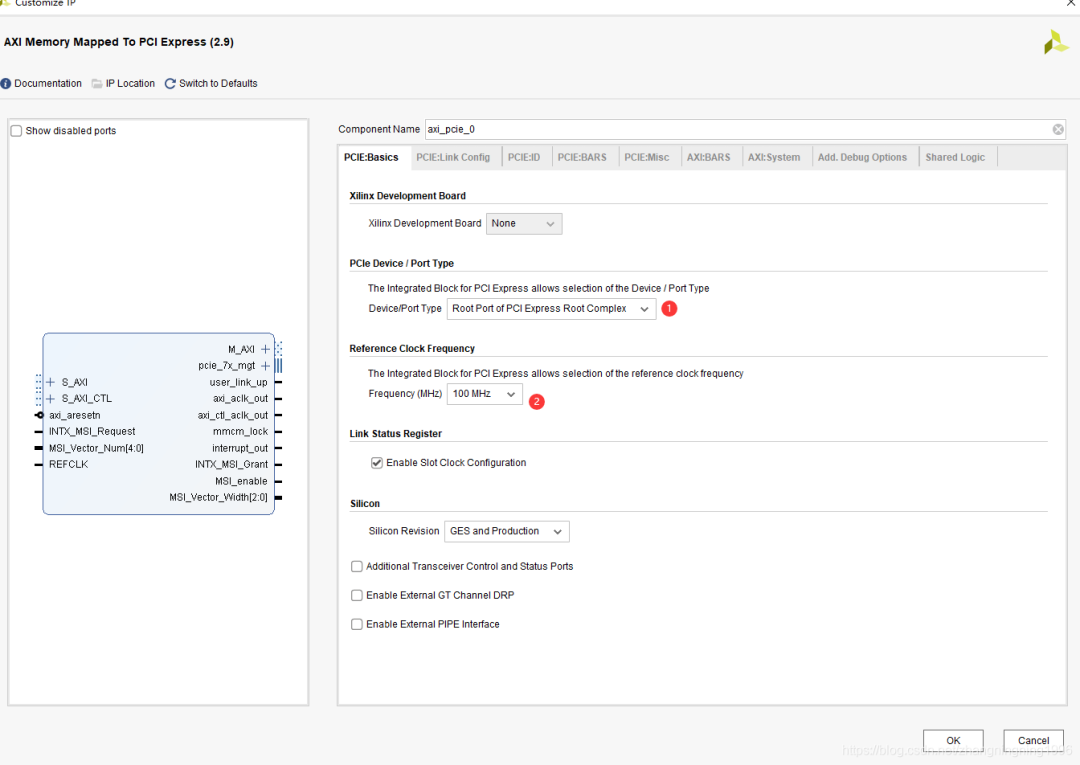

1、這里選擇root port

2、選擇開(kāi)發(fā)板上的時(shí)鐘100MHz

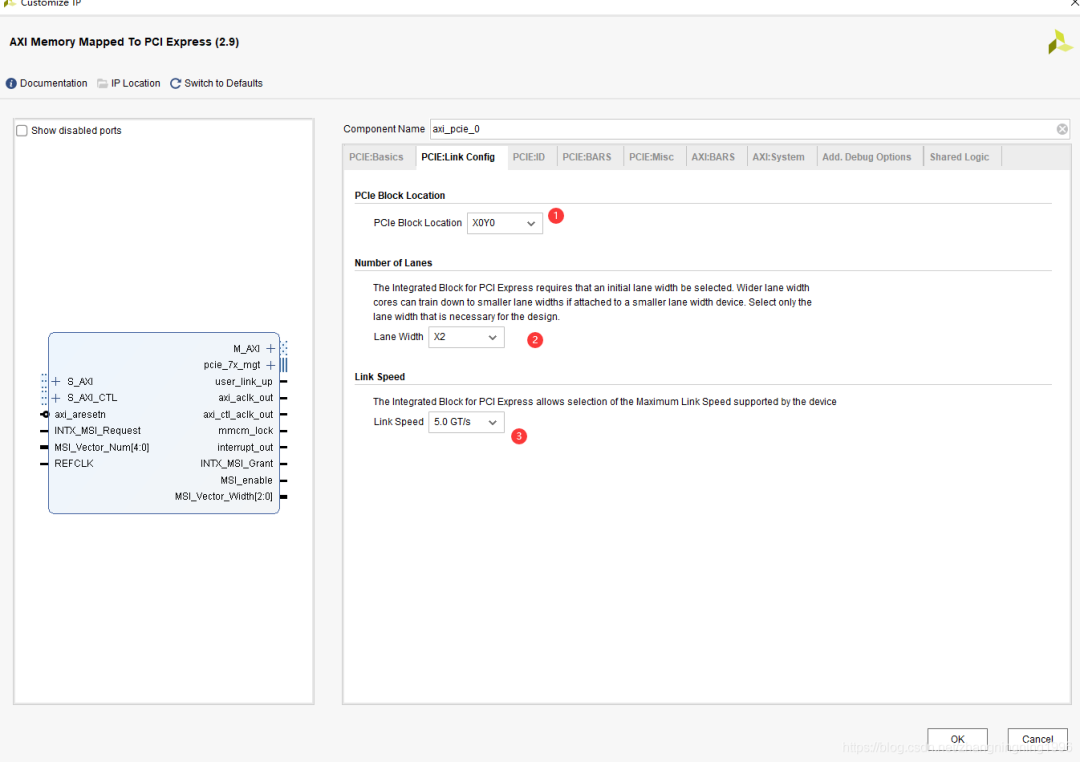

1、這里選擇硬核PCIE所在的位置

2、選擇PCIE的lane的個(gè)數(shù)為2個(gè)

3、選擇PCIE的通信速度為5GT/s

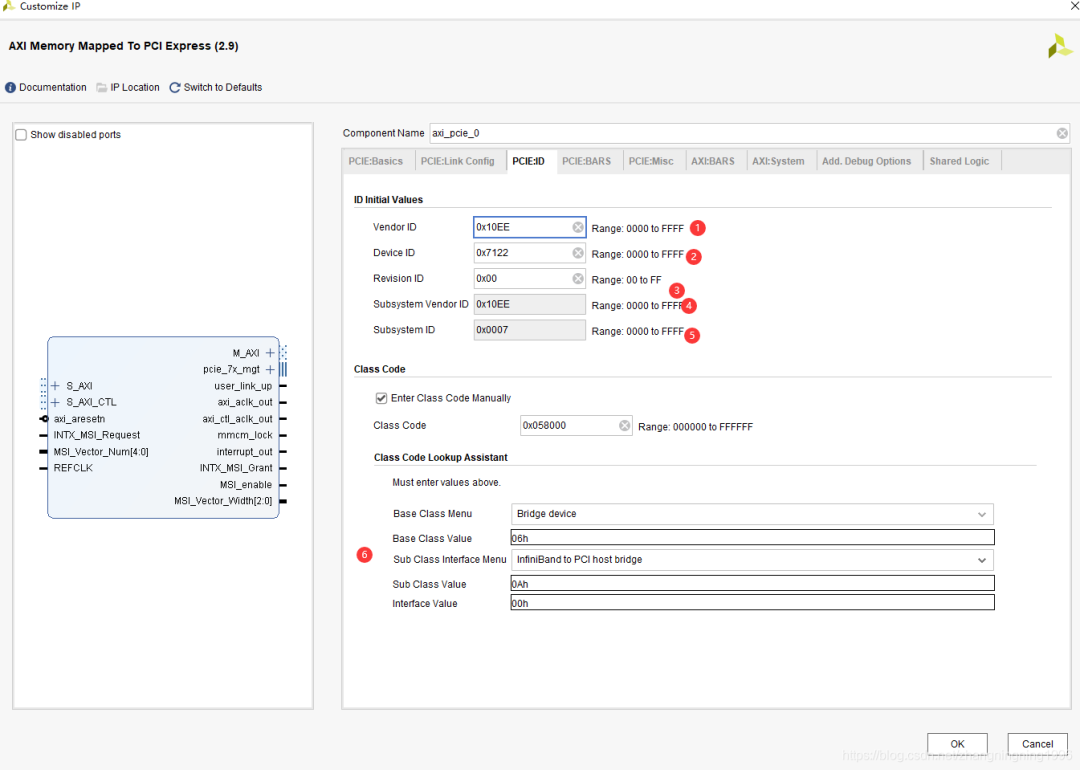

1、廠商ID,專屬于Xilinx的PCIE的ID,是固定的。

2、設(shè)備ID,與廠商ID一起指明數(shù)據(jù)的類型,被使用選擇PCIE上位機(jī)的軟件驅(qū)動(dòng)。

3、版本ID,指明使用該P(yáng)CIE IP進(jìn)行設(shè)置的版本

4、子廠商ID,用來(lái)更近一步的區(qū)分Xilinx旗下的廠商

5、子系統(tǒng)ID,用來(lái)識(shí)別板卡的的ID

6、PCIE在實(shí)驗(yàn)中承擔(dān)的角色,這里我們選擇默認(rèn)即可

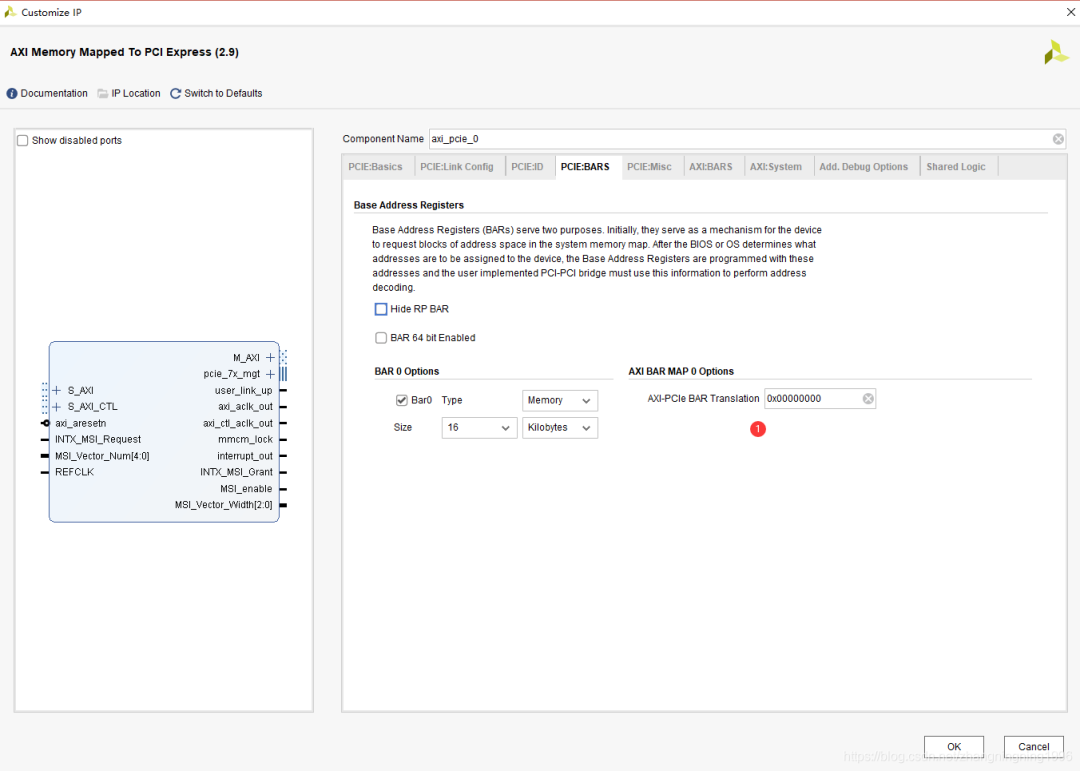

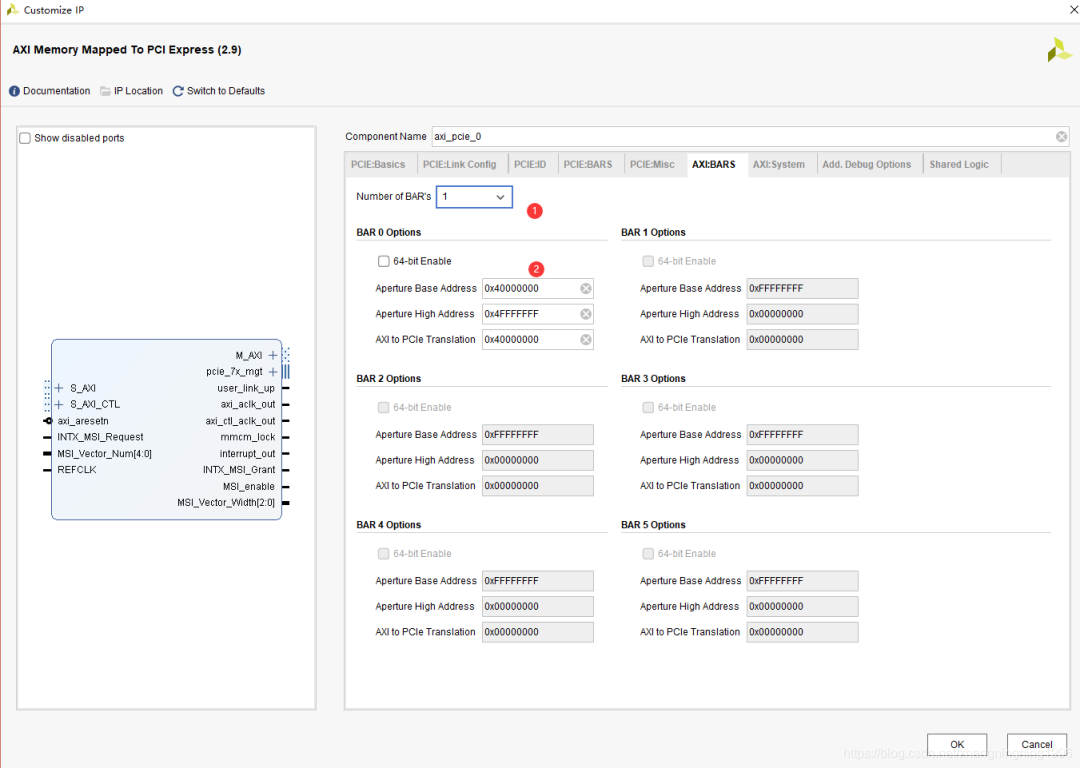

1、PCIE To AXI的BAR地址空間設(shè)置,用于IO的配置空間,也是endpoint to rootport的方向

默認(rèn)即可

1、2、AXI TO PCIE的BAR空間,也就是rootport to endpoint可以看見(jiàn)的方向。

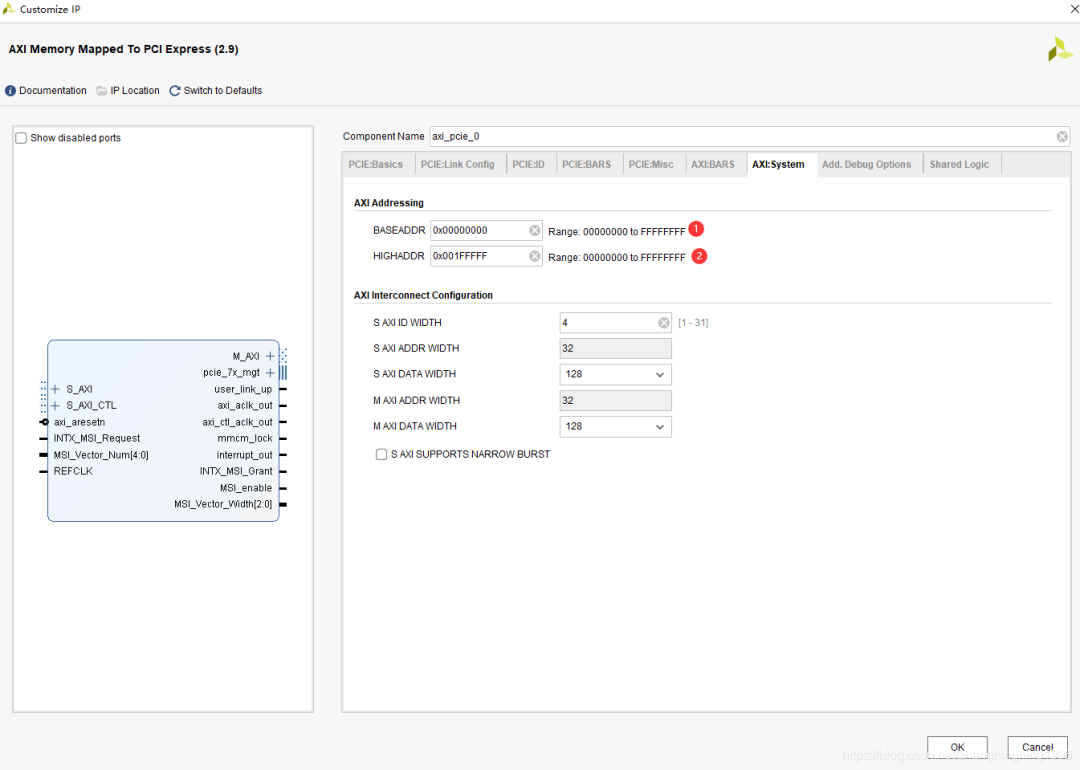

1、2、AXI總線的最低地址與最高地址

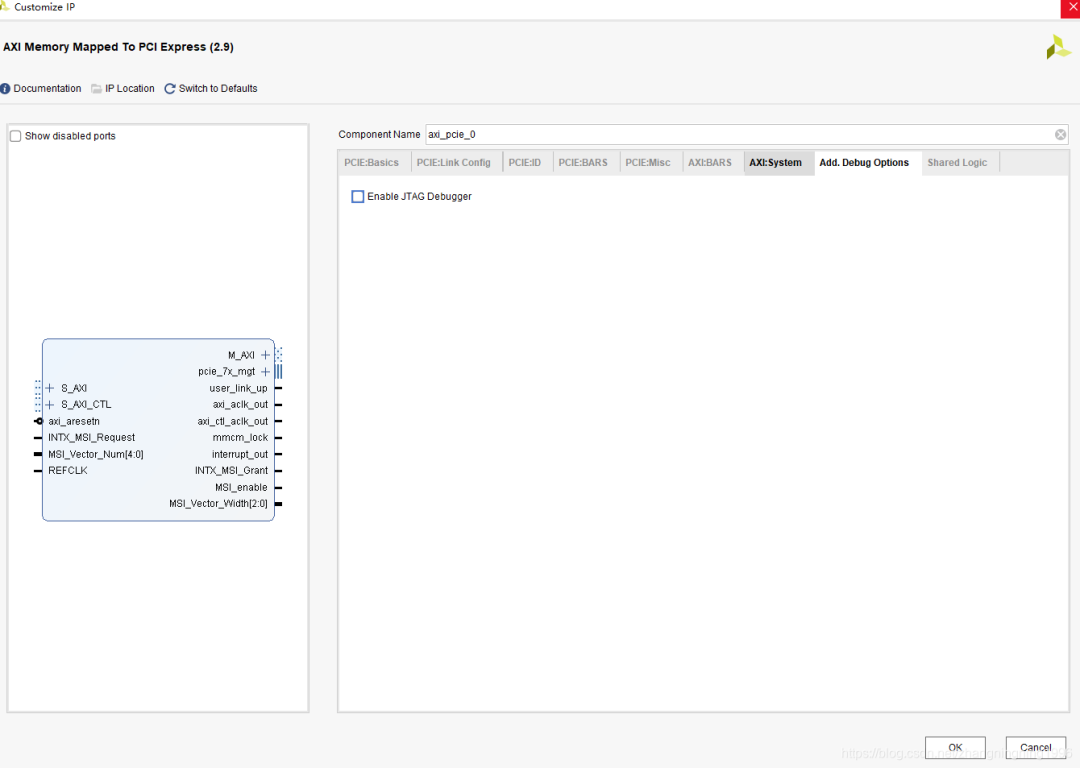

默認(rèn)即可

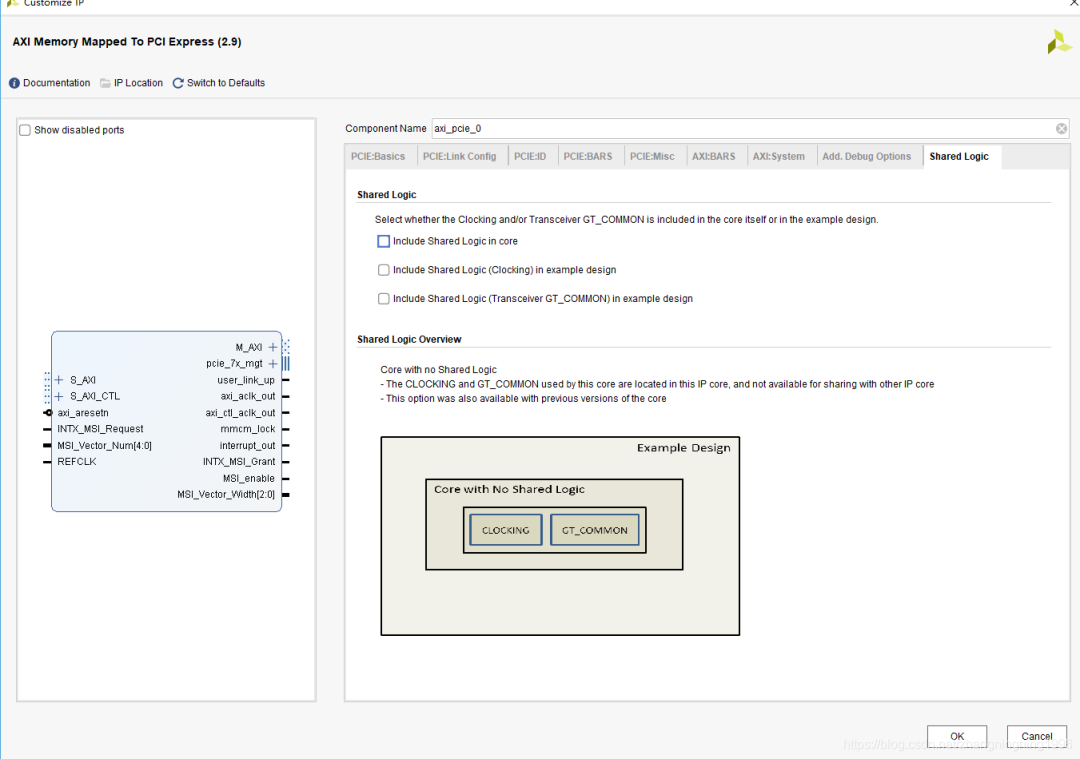

默認(rèn)即可。

PCIE root port的Block Design搭建

這里直接給出相應(yīng)的圖像,供大家簡(jiǎn)略學(xué)習(xí):

1、是endpoint讀寫(xiě)rootport的數(shù)據(jù)通路

2、是rootport讀寫(xiě)endpoint的數(shù)據(jù)通路

上面Block design的搭建其實(shí)我一直不明白centerDMA Ip的作用,也沒(méi)真正下板實(shí)現(xiàn)過(guò),這里也就不多說(shuō)了。因?yàn)镕PGA作為rootport來(lái)使用,本身就很少見(jiàn)。

上面的內(nèi)容,我們主要介紹了VIVADO中PCIE IP的使用,介紹的比較粗略。尤其是第一個(gè)很常用,想進(jìn)一步了解的同學(xué)可以找一找原本的資料,這里我只是介紹了自己的想法。

編輯:黃飛

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論