引言

在嵌入式系統(tǒng)或移動設(shè)備上使用SD卡,接口的構(gòu)建和文件系統(tǒng)實(shí)現(xiàn)是必須解決的問題。本文探討在CycloneII平臺為基礎(chǔ)的嵌入式系統(tǒng)上,實(shí)現(xiàn)SD卡接口和文件系統(tǒng)的實(shí)現(xiàn)方法。

基于FPGA IP軟核處理器的嵌入式系統(tǒng),因其集成度高、可靈活配置和性價比方面的優(yōu)勢,已經(jīng)逐漸逼近甚至趕超采用專用集成電路(ASIC)的設(shè)計(jì)方案。

利用Nios II可定制周邊設(shè)備的特點(diǎn),在FPGA中,通過DHL編程構(gòu)造出SD卡需要的SPI接口和其他控制信號的方式。在此基礎(chǔ)上,在Nios II處理器上實(shí)現(xiàn)了一個靈活的文件系統(tǒng)。

基于FPGA和Nios II軟核構(gòu)建SOPC嵌入式文件系統(tǒng),本文所做的工作包括:Nios II處理器IP軟核的最小SOPC系統(tǒng)的構(gòu)建,SD卡的底層扇區(qū)讀寫驅(qū)動程序的編寫方式,znFAT32文件系統(tǒng)的移植,以及對SD卡文件操作的實(shí)現(xiàn)等。

1 基于Nios II軟核的SOPC系統(tǒng)構(gòu)建

1.1 SOPC系統(tǒng)的結(jié)構(gòu)

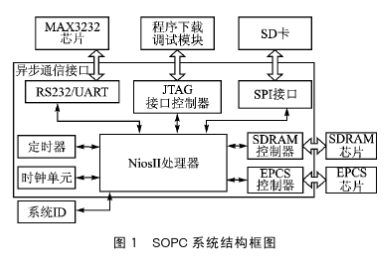

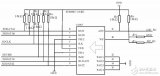

如圖1所示,基于NiosII的SOPC系統(tǒng)包括如下部分:

①系統(tǒng)核心模塊:Nios II處理器。

②處理器外圍支持電路:時鐘單元以及存儲器單元SDRAM控制器(包括存儲代碼的ROM與存儲變量的RAM)部分。

③程序下載調(diào)試模塊:JTAG接口控制器和異步通信接口(UART用于打印調(diào)試信息)。

④片上系統(tǒng)的內(nèi)部外設(shè)模塊:諸如定時器、UART、SPI、GPIO等,這部分總的功能電路可根據(jù)需要配置,在本例的實(shí)驗(yàn)驗(yàn)證中,主要用到SD卡的接口是SPI。

⑤EPCS控制器:由于FPGA是基于RAM的結(jié)構(gòu)框架,掉電后代碼會丟失。所以FPGA需要配置一個ROM在上電后將代碼加載到RAM中運(yùn)行。在SOPC系統(tǒng)中,EPCS控制器有兩個作用,一是用來幫助EDS工具將軟件程序下載到EPCS芯片中去,二是在FPGA配置完成后引導(dǎo)EPCS芯片中的程序加載到SDRAM中去運(yùn)行。

1.2 Cyclone II構(gòu)建SOPC系統(tǒng)的過程

Altera公司為在其生產(chǎn)的FPGA上構(gòu)建SOPC,不僅提供了各種使用的IP核模塊,還提供了極為友好的集成開發(fā)環(huán)境Quartus II。在Quartus II中,有一個工具SOPCBuilder,可以幫助用戶通過添加和配置(給出參數(shù))IP核的方式,自動構(gòu)建Verilog HDL語言硬件代碼。

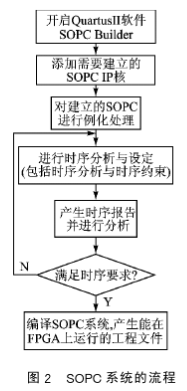

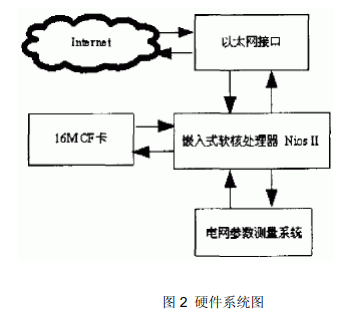

在Quartus II中,構(gòu)建SOPC系統(tǒng)的流程如圖2所示。

將需要的IP核模塊添加完成后,下一步是用Verilog HDL語言編寫頂層文件,對定制的SOPC進(jìn)行例化處理(模塊之間的連接關(guān)系定義,I/O引腳的配置),編譯頂層文件和模塊IP核,才能生成在FPGA上運(yùn)行的片上系統(tǒng)。

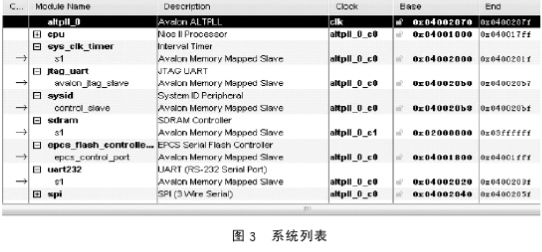

在添加IP核后,SOPCBuilder可生成資源列表,本文構(gòu)建的系統(tǒng)列表如圖3所示。

在實(shí)例中使用了Nios II模塊、時鐘模塊、定時器、SDRAM模塊、EPCS模塊、UART模塊和SPI共計(jì)7個模塊。

SOPC系統(tǒng)構(gòu)建完成后,模塊之間信號傳遞的時序并未確定。接下來的時序設(shè)計(jì)是SOPC能否正常運(yùn)行的關(guān)鍵。在片上系統(tǒng)生成后,首先要對系統(tǒng)進(jìn)行時序分析,以便使系統(tǒng)的時序符合設(shè)計(jì)邏輯的要求,并保證系統(tǒng)的正常工作,必要時要對系統(tǒng)的時序進(jìn)行適當(dāng)?shù)募s束。這一工作

可利用Quartus II軟件中內(nèi)嵌的TimeQuest完成,也可以使用第三方提供的時序分析軟件,如PrimeTime軟件等來實(shí)現(xiàn)。

本文采用Altera公司提供的TimeQuest來進(jìn)行時序約束。經(jīng)過時序約束后,對工程再編譯,可產(chǎn)生時序報告。通過分析時序約束報告,可對約束適當(dāng)修改,這個過程可反復(fù)進(jìn)行,直到滿足時序要求為止。

2 SD卡接口協(xié)議分析與驅(qū)動程序設(shè)計(jì)

2.1 SD卡通信接口協(xié)議分析

SD卡一般定義了SD和SPI兩種可選的總線操作方式,本文采用SPI方式與SD卡接口,可以直接利用Quartus II中提供的SPI控制器IP核。S PI協(xié)議是面向位傳輸?shù)耐酱型ㄐ艆f(xié)議。在SPI模式下,SD卡可以支持單塊與多塊的讀寫操作。

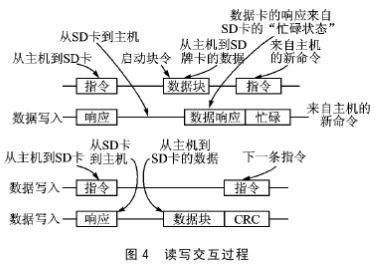

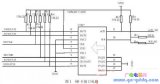

SOPC上的SPI控制器與SD卡之間的讀寫操作過程應(yīng)符合SD卡的通信協(xié)議,其讀寫交互過程如圖4所示。

從圖4中可以看出,任何操作都是由SPI控制器的SD寫命令開始,SD卡在接收到一個合法命令后,將給予應(yīng)答來響應(yīng),接下來便是數(shù)據(jù)塊的讀或?qū)懖僮鳌?/p>

2.2 SD卡驅(qū)動層程序的編寫

Nios II EDS是Altera公司為其Nios II處理器開發(fā)的一款C/C++語言編程軟件,其軟件架構(gòu)是基于HAL(Hardware Abstraction Layer)之上的,Nios II EDS為Nios開發(fā)者提供了編程接口、底層設(shè)備驅(qū)動、HAL API,以及C標(biāo)準(zhǔn)庫等資源。更重要的是,HAL系統(tǒng)庫為Nios II軟件設(shè)計(jì)人員提供了應(yīng)用程序與底層硬件交互的設(shè)備驅(qū)動接口,從而大大簡化了應(yīng)用程序的開發(fā)。此外,HAL系統(tǒng)庫還為應(yīng)用程序與底層硬件驅(qū)動之間劃分了一條清晰的界線,從而大大提高了應(yīng)用程序的可復(fù)用性,使得應(yīng)用程序不受底層硬件變化的影響。

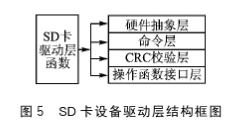

片上系統(tǒng)的SPI控制器硬件邏輯,是由SOPC Builder工具將一個SPI主控器軟核封裝到系統(tǒng)中的,此SPI控制器與Nios II軟核以Avalon總線相連接。SD卡的設(shè)備驅(qū)動層分為4層,包括硬件抽象層、命令層、CRC校驗(yàn)層與操作函接口層,其結(jié)構(gòu)框圖如圖5所示。

硬件抽象層主要實(shí)現(xiàn)Nios II處理器對SPI控制器相應(yīng)的功能寄存器的操作。

命令層定義了對SD卡各種操作的交互方法,包括命令碼與應(yīng)答碼的定義。

CRC校驗(yàn)層主要完成校驗(yàn)工作,對于命令與數(shù)據(jù)采取不同的校驗(yàn)方式。命令用CRC7校驗(yàn),數(shù)據(jù)用CRC16校驗(yàn)。

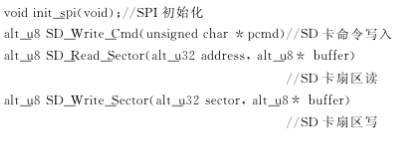

操作函數(shù)接口層的作用是向znFAT32文件系統(tǒng)提供SD卡的所有操作,這其中包括了SD卡的初始化、扇區(qū)讀寫等函數(shù)接口(這是文件系統(tǒng)對SD卡進(jìn)行文件操作所必需的),以供znFAT32文件系統(tǒng)調(diào)用。這里利用Nios IIEDS集成開發(fā)環(huán)境編寫的驅(qū)動實(shí)現(xiàn)SD對卡的塊讀寫(以扇區(qū)為基本單位進(jìn)行讀寫操作),為SD卡掛載文件系統(tǒng)提供API函數(shù)。

每個層的接口函數(shù)如下:

3 znFAT32文件系統(tǒng)的嵌入和SD卡的掛載

3.1 znFAT32文件系統(tǒng)概述

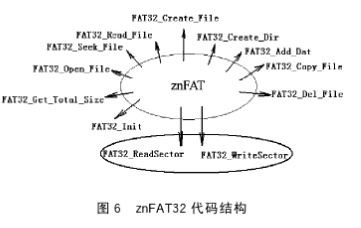

znFAT32是于振南為小型嵌入式設(shè)備完全獨(dú)立編寫,且開放源代碼的FAT32文件系統(tǒng)解決方案。znFAT32能夠支持眾多的存儲設(shè)備(SD卡、CF卡、Flash、U盤等),支持多個存儲器共同工作,可以支持同時訪問多個存儲器對文件的操作。對硬件資源要求低,能夠輕松地移植到51單片機(jī)、AVR、ARM、DSP、Nios II等處理器上,占用資源極少(僅占用800字節(jié)左右的RAM),非常適合嵌入式開發(fā)中文件系統(tǒng)的嵌入。其代碼完全由C語言編寫,能夠輕松閱讀,移植方便。其代碼結(jié)構(gòu)如圖6所示。

由圖6可知該文件系統(tǒng)包含兩層。

文件系統(tǒng)代碼層——主要提供對存儲設(shè)備進(jìn)行操作的各種函數(shù)。

存儲設(shè)備接口層——主要是為了掛載不同的存儲設(shè)備。

3.2 文件系統(tǒng)SD卡的掛載

znFAT32文件系統(tǒng)掛載需要SD卡驅(qū)動層提供的扇區(qū)讀寫函數(shù)。將編寫的扇區(qū)讀寫函數(shù)SD_Read_Sector、SD_Write_Sector取代文件系統(tǒng)中的FAT32_ReadSector與FAT32_WriterSector兩個函數(shù)即可。根據(jù)需要的處理器編寫SD卡驅(qū)動程序十分重要,只有保證驅(qū)動程序的正確性,才能進(jìn)行文件系統(tǒng)的正確掛接,才能在掛接完成后對SD卡進(jìn)行文件操作。

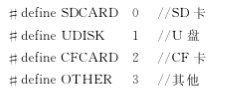

znFAT32文件系統(tǒng)的掛接需要對znFAT32文件系統(tǒng)提供的用于標(biāo)定存儲設(shè)備的全局變量Dev_No設(shè)備號進(jìn)行處理,znFAT32文件系統(tǒng)給我們提供的存儲設(shè)備宏定義如下:

對不同設(shè)備進(jìn)行文件操作,需要通過設(shè)備號來選擇不同的設(shè)備驅(qū)動函數(shù)。對SD卡操作需將Dev_NO定義為SDCARD。

4 文件系統(tǒng)在Nios II中的應(yīng)用實(shí)例

完成SOPC系統(tǒng)的創(chuàng)建后,在生成的Nios II系統(tǒng)上通過Nios II EDS編程,便可將SD卡與文件系統(tǒng)掛接。

4.1 znFAT32文件系統(tǒng)的使用

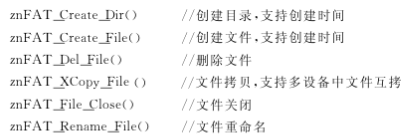

znFAT32文件系統(tǒng)為用戶提供的對文件的基本操作函數(shù)讓我們能夠輕松地對文件進(jìn)行操作。下面列舉了幾個基本函數(shù):

通過上面的函數(shù),可以完成對SD卡的文件讀寫、刪除、數(shù)據(jù)添加、目錄創(chuàng)建、文件拷貝、文件重命名等操作。

4.2 SOPC系統(tǒng)對SD卡文件讀寫操作的驗(yàn)證

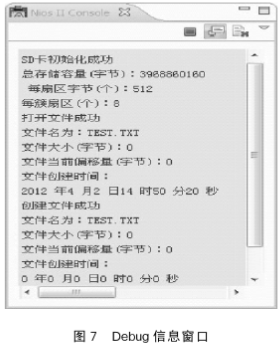

為了驗(yàn)證上述系統(tǒng)能否正常實(shí)現(xiàn)SD卡讀寫,筆者選用了4 GB容量的金士頓SDHC卡,進(jìn)行了文件讀寫實(shí)驗(yàn)。圖7為Nios II EDS給出的Deb ug信息窗口。信息顯示了在構(gòu)建的系統(tǒng)上SD卡的初始化(實(shí)現(xiàn)文件系統(tǒng)的掛接),接著讀取SD卡的存儲容量、扇區(qū)大小、每簇扇區(qū)數(shù),并在根目錄下面打開名為TEST.TXT的文件,并對該文件的信息進(jìn)行讀取。在一級子目錄下面,同樣建立一個TEST.TXT的文件,并對文件信息進(jìn)行讀取。

由運(yùn)行結(jié)果可知,初始化成功并識別此SD卡為SDHC卡,容量為964 256(總簇數(shù))×8(每簇扇區(qū)數(shù))×512(每扇區(qū)字節(jié)數(shù))≈3 968 860 160。根目錄下的TEXT.TXT文件被打開,打開文件成功后在DIR1子目錄下面創(chuàng)建TEST.TXT。由主函數(shù)創(chuàng)建的文件日期在TimeCreat[6]={12,1,4,17,40,28)中存放,文件成功后讀取創(chuàng)建的新文件的詳細(xì)信息。

為了進(jìn)一步驗(yàn)證本系統(tǒng)對SD卡的寫入操作,筆者將此SD卡通過讀卡器與PC機(jī)連接,在PC機(jī)的文件系統(tǒng)下,顯示了相同的結(jié)果。

結(jié)語

本文通過在CycloneⅡ系列FPGA上構(gòu)建SOPC系統(tǒng),并在該系統(tǒng)上基于NiosⅡ處理器構(gòu)建了SD卡文件系統(tǒng)。該系統(tǒng)以SPI接口方式與SD卡連接,文件系統(tǒng)是面向嵌入式系統(tǒng)的緊湊型開放源碼的系統(tǒng)。經(jīng)過對SD卡的操作驗(yàn)證,證明本文提供的方案具有設(shè)計(jì)靈活、集成度高、通用性強(qiáng)、移植性好等諸多優(yōu)點(diǎn)。在線陣CCD數(shù)據(jù)采集實(shí)驗(yàn)系統(tǒng)以及數(shù)控貼片控制系統(tǒng)上得到了很好的應(yīng)用。

責(zé)任編輯:gt

電子發(fā)燒友App

電子發(fā)燒友App

評論