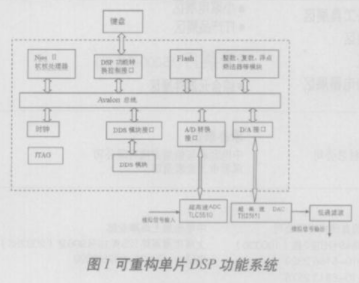

本文主要搭建一個多生理參數測量系統的數據處理平臺,在FPGA中嵌入一個32位Nios II軟核處理器,用于控制數據的傳輸、存儲及顯示。主要完成了此數據處理平臺硬件系統的定

2010-08-18 12:10:44 933

933

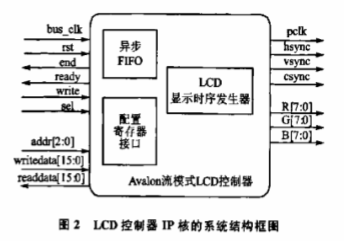

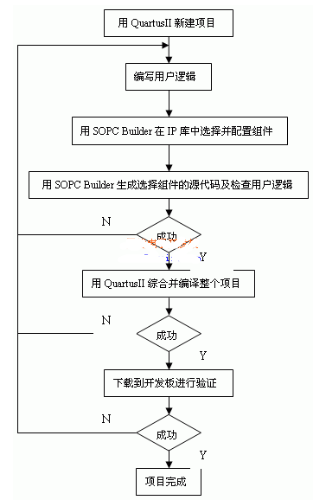

本文介紹了一種基于NIOS II軟核處理器實現對LCD-LQ057Q3DC02控制的新方法。在設計中利用FPGA的Altera的SOPC Builder定制NIOS II軟核處理器及其與顯示功能相關的“軟” 硬件模塊來協同實現顯示控

2011-11-09 11:30:07 2000

2000

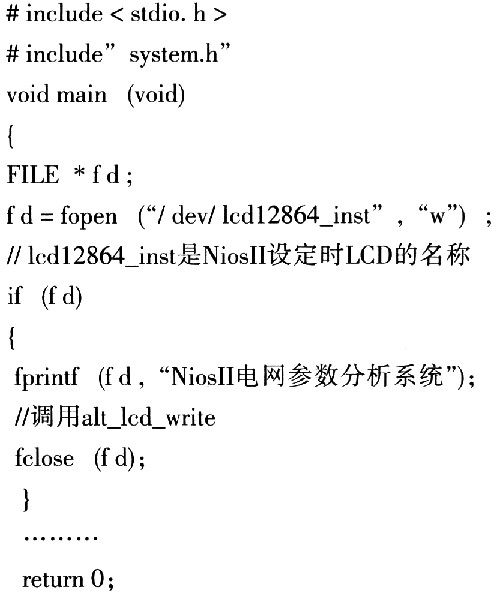

儀器、儀表和低功耗電子產品中。本文介紹一種基于NIOSⅡ的LCD的控制方法。利用SoPC技術,在NIOSⅡ系統中添加相應的I/O端口實現對液晶顯示器的控制。

2018-10-31 08:04:00 3719

3719

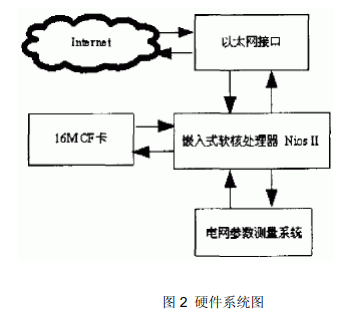

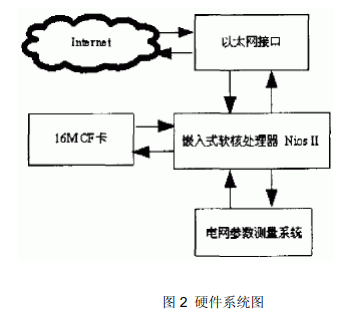

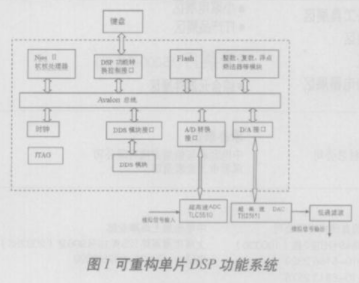

系統的硬件結構如圖2所示。硬件系統的核心是構建于Ahera Cyclone FPGA中的Nios II嵌入式軟核處理器。Nios II系列嵌入式處理器是一款通用的RISC結構的CPU,它定位于廣泛

2020-06-28 14:49:45 540

540

基于μC/OS-II實時操作系統實現多任務管理運行模式,采用Nios II 32位處理器作為LED顯示屏控制系統的核心,控制單屏幕多窗口任意顯示。整個控制系統在一片FPGA上實現,使用SOPC Builder軟

2011-10-02 16:00:21 2366

2366 。 基于NIOSⅡ的矩陣鍵盤和液晶顯示外設組件的設計 本文提出了一種針對LCD控制器和矩陣鍵盤的IP核的設計方法。該方法利用SOPC Builder中元件編輯器Create New

2015-01-16 22:10:42

,國際上只有I-Shou大學的Yu-Jung Huang等人設計了可驅動不同規模LCD的驅動電路IP核,通過在系統中植入嵌入式微處理器來實現這一功能。但是,這種嵌入式微處理器使系統更復雜,而且成本更高

2012-08-12 12:28:42

NIOS II 軟核中EPCS配置芯片的存儲操作 最近用CYCLONE FPGA做的視頻圖像疊加板需要存儲一些用戶配置信息,而EPCS4配置芯片除了存儲FPGA配置信息和NIOS II程序外,還有

2018-07-05 05:58:25

表1 Nios II處理器系統的最大時鐘頻率(tMAX)(MHz)表2 Nios II處理器系統的MIPS(每秒鐘一百萬個指令) 表3 在不同設備家族上的Nios II處理器系統的MIPS/MHz比

2018-07-03 02:30:47

問一個問題,為什么配置的PLL的IP核,如圖,紅框的那個接了輸入,在NIOS II中就會出現 [Target Connection]: Connected system ID hash

2016-10-04 21:05:25

,浪費生命。NIOS內核的裁剪問題,編譯出來的文件過大,導致Quartus_II軟件構造好的on chip memory下載不進去,顯示下載elf文件失敗elf文件下載失敗還有可能與你使用的IP核有關

2017-05-30 14:03:44

個最小系統僅僅需要:1、NIOS II f 或者s 處理器,帶硬件乘法器(建議使用NIOS II /f,使用NIOS II/s很慢)2、最小8M的SDRAM3、一個全功能的定時器4、JTAG/UART

2012-02-21 15:55:21

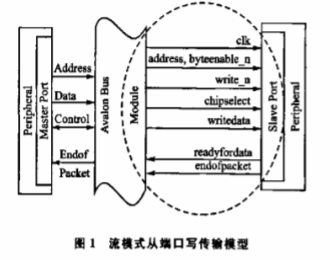

如何與AD采集融合。 查詢了一下,發現可以使用Avalon總線,將AD的verilog功能描述封裝成一個IP核,掛到Avalon總線,實現verilog與NIOS II的通訊。 但是不知道這種方法速度夠不夠

2017-11-21 10:11:22

nios ii雙核例子nios ii雙核例子NIOS II 雙核構建的簡單例子,希望對大家有所幫助。 1、 實現簡易功能 Cpu_0控制pio_cpu_0(輸出),令其輸出為1。此輸出和cpu_1

2012-08-12 15:18:48

可以移植到不同的半導體工藝中去生產集成電路芯片。隨著CPLD/FPGA的規模越來越大,設計越來越復雜,使用IP核是一個趨勢。 本文研究了ATM流量控制的原理,并給出了一種IP核的實現方法,該IP核不僅可以用于獨立芯片,還可以作為系統的一個子模塊直接調用。

2011-09-27 11:54:25

用Quartus II 調用IP核時,在哪可以查看IP核的例程

2014-07-27 20:28:04

CAN控制器IP核(可直接在Nios II中使用)

2016-08-24 16:54:21

在其業內領先的低成本Cyclone TM FPGA系列和Nios軟核嵌入式處理器成功的基礎上,Altera現在推出了第二代產品系列。Cyclone II器件為用戶提供更高的邏輯密度和新增硬件性能,比

2019-07-18 07:43:25

FPGA是現場可編程門陣列,是可編程邏輯器件(PLD)的一種。 NIOS II是一種知識產權核(IP Core),是嵌在FPGA內部的處理器軟核,相當于在FPGA內部設計了一個微處理器

2018-08-17 09:59:27

的SOPC系統中設計了LCD顯示驅動IP核,并下載到Cyclone系列的FPGA中,實現了對LCD的顯示驅動。

2019-08-06 08:29:14

很多人都說QUARYUSII中的IP核是收費的,不可以直接用的,其實不然,下面我以FIR濾波器的核的使用來給大家介紹IP核的使用,希望對大家有點幫助。 1.使用 (1)首先建立工程,這個就不

2019-06-03 09:09:51

如題:我之前用Quartus ii 13創建的工程。現在改用17了。想編輯以前的IP核但是找不到MegaWizard Plug-In Manager 了

2017-09-24 21:06:09

關于QuartusⅡ10.1中NIOS2軟核的構建、軟件編譯及程序固化 一、硬件開發1、構建CPU模塊2、構建EPCS控制器,SYSTEM ID模塊,JTAG UART模塊3、構建RAM模塊(1

2022-01-25 07:58:08

LCD上顯示,并可通過USB接口將信息拷貝,或通過RS-232接口將信息上傳給PC機,也可以通過GPRS將獲得的信息方便快捷地發往數據中心作驗證。 整個系統的核心部分是內嵌Nios II軟核

2018-10-31 16:54:52

用戶是可自定制的,具有靈活性和可裁減性等優點。結合內河航道航標管理的實際情況,介紹了一種新的基于Nios II軟核的航標監控系統的設計方案。根據系統的運行結果顯示,設計實現了系統預期功能,為監控中心能

2015-01-30 11:05:50

基于Qsys + Nios II SBT開發的Nios II教程,內容詳細,學習NiosII的同學可以關注下~點擊下載

2014-10-13 18:17:58

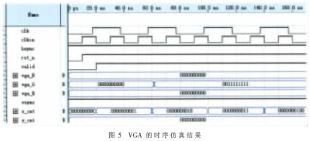

24M的時鐘信號,供640*480分辨率的VGA驅動電路使用。NIOS II CPU:實現系統的控制以及顯示內容的處理。SDRAM:NIOS II CPU運行內存和TFT顯示圖像幀緩存

2020-02-26 19:37:23

SPI、定時器、UART串口等IP核,只要在Qsys中添加好這些IP,然后在NIOS II的開發環境(定制版Eclipse)中編寫驅動程序和應用程序即可完成該控制器的使用。當然,為了讓這些IP用起來

2020-02-24 19:27:02

`附件為小梅哥SOPC公開課第二課NIOS II自定義IP的設計與使用的建隨堂工程。小梅哥SOPC公開課第二課主要講解如何使用Verilog自己編寫一個符合NIOS II Avalon MM接口總線

2016-08-13 11:04:32

內部中斷需要具備以下幾個條件:(1)Status控制寄存器中的PIE位為1; (2)某個中斷請求irqn有效;(3)在ienable寄存器中,該中斷源相應位為1 當內部中斷發生后,Nios II處理器會

2016-10-21 18:31:59

,近期主要深入學習了Qsys系統的硬件部分和軟件部分,首先學習了Nios II的硬件框架結構,收獲頗豐。 下圖是Qsys的系統結構框圖: 圖中主要包括Nios II軟核處理器和UART、SPI、定制外設

2016-10-21 16:47:44

FPGA學習嵌入式硬件最小系統搭建(一)(NIOS II處理器設置)本期學習目的:利用NIOS II系統點亮LCD1602屏及5.7寸LCD(8080接口)。前言概述上篇文章介紹了嵌入式硬件系統概述

2021-12-20 07:02:02

收到遠端的信號,進行解調解擴并傳給網絡,完成接收部分。其中一個NIOS II 核完成無線收發機接收和發送的信號處理和運算,另一個核運行操作系統,完成以太網傳輸和其他相關控制。之所以選擇使用NIOS

2009-10-06 15:05:24

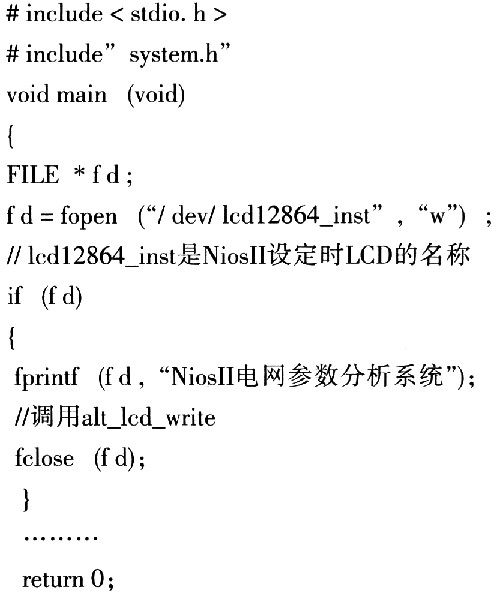

的程序設計在NiosⅡ和LCD的接口中,一方面可以通過在NiosⅡ系統中添加相應I/O口的方式來實現對液晶顯示屏LCD的間接控制,另一方面也可以利用構建IP核來直接進行控制。第一種是將LCD接口當作普通

2018-12-11 11:08:10

II軟核來完成,Nios II處理器將片上存儲器中的數據逐一讀取并進行處理之后顯示在LCD上,Avalon總線負責各個控制器模塊的數據傳輸。FPGA選用Altera公司的EP3C5E144C8。1.2

2019-06-03 05:00:06

II CPU如圖4所示。4 系統實現啟動Nios II IDE環境下,創建系統軟件控制部分后,運行程序即可采集指紋圖像,本系統環境下采集的指紋圖像5所示。圖6為作參考比較的光學采集指紋圖像,指紋圖

2019-04-29 07:00:08

、NiosII實現hello world1.1硬件設計芯片選擇如下設置系統時鐘,Tools -> Qsys添加Nios II Processor在搜索框中,輸入nio,找到Nios II Processor,點擊Add,最后保存即可添加On_Chip Memory在搜索框中,輸入on_ch

2021-12-27 08:13:55

基于NioslI的SOPC系統中設計了LCD顯示驅動IP核,并下載到Cyclone系列的FPGA中,實現了對LCD的顯示驅動。

2019-11-04 08:18:58

信息顯示在LCD液晶顯示屏上。各硬件模塊之間的協調工作通過嵌入式軟核處理器NiosⅡ用編程實現控制。本設計所搭建的LCD12864控制器是通過編程實現的IP核。關鍵詞:DDS;FPGA技術;順序存儲;NiosⅡ;IP核

2019-06-21 07:10:53

任務需求來定制顯示控制功能,可以增強系統可靠性和設計靈活性,降低了成本。目前針對LCD 顯示屏設計的控制器IP 核文章較多[1-2],但對于TFT-LCD 觸控屏設計的控制器IP 核文章較少[3],而且

2018-11-07 15:59:27

實例精煉》第四章_VHDL的數據類型.avihttp://115.com/file/e7wpz111#《基于VHDL的FPGA與NIOS_II實例精煉》第十四章_字符型LCD的顯示控制.avihttp

2012-02-06 11:22:55

驗證的IP模塊。參考演示包括將系統編程為具有墻壁和邊緣避免以及同步運動的自主車輛。簡單的PID控制將用于影響直流電機的速度和位置。步進電機將基于全步,半步和微步模式進行控制。附錄中包含最終演示,用于監控電池系統中剩余的電量并在LCD上顯示該值

2020-05-19 09:30:50

,LCD液晶顯示器憑借功耗低、體積小、輕薄及控制驅動簡單等特點,在智能儀器、儀表和低功耗電子產品中得到了廣泛應用。以深圳秋田視佳實業有限公司的液晶顯示模塊CBGl28064為例,告訴大家, 如何在SOPC的NiosII中設計LCD顯示驅動IP核?實現了對LCD的顯示驅動。

2019-08-05 07:56:59

時,Builder開發工具中沒有提供現成的數碼管顯示IP核,這使設計者工作量增加。這里把數碼管控制器設計為一個共陰極(或共陽極)7段數碼管動態顯示IP核,并給出此核的一個參考驅動程序。

2019-08-09 06:09:05

Altera公司的FPGA作為全定制芯片的一個代表正在得到日益廣泛的應用。為了用戶使用方便,Altera公司推出嵌入式軟核NiosⅡ可以便利地使用工具生成并放人FPGA芯片中。NiosⅡ軟核可以在用

2019-10-25 07:25:38

怎么實現基于Nios II DTMB單頻網適配器的設計?

2021-05-31 07:01:29

介紹如何在Altera開發平臺上,使用Nios軟核CPU來構建嵌入式Internet系統;并結合以太網遠程數據采集系統的實例,介紹此類系統硬件,軟件的設計方法。

2021-06-04 07:05:47

本文以 640*480的數字輸入的 TFT-LCD顯示屏為例,介紹了一種基于 NiosⅡ軟核處理器實現對 TFT-LCD接口的方法。解決了通常情況下必須使用LCD 控制專用芯片才能解決 LCD顯示的問題。

2021-06-08 06:46:33

是不是所有的cyclone IV系列的芯片都支持nios II軟核

2014-08-13 10:34:55

本文設計了一種在多處理器系統中的Nios II軟核處理器的啟動方案,這個方案在外部處理器向Nios II的程序存儲器和數據存儲器加載數據時,可以控制Nios II處理器的啟動。

2021-04-27 06:52:42

求大神給幾個VHDL寫的基于NIOS IIIP核源碼,簡單的就行,比如IIC AD什么的,多謝

2016-04-11 21:19:33

建立NIOS_Helloworld工程,進行IP核連線的時候,NIOS的jtag_reset信號如何與jtag_uart進行連接?

在原子哥的文檔中對這步的操作在下面,

上面是文檔中對連接方法的描述,但是我的qsys中在IRQ欄好像沒有進行連接的按鈕

請問軟件是如何操作的?

2019-05-15 06:35:26

片上Nios Ⅱ嵌入式軟核多處理器系統具有哪些優勢?如何實現片上嵌入式Nios Ⅱ軟核六處理器系統的設計?

2021-04-19 08:17:09

請問怎么去控制qsys搭建的SDRAM這個ip核,因為想把一個ram核當作一個外部AD數據的存儲器,將外部數據存儲起來,再用nios通過API函數讀出來作顯示,現在就是不知道怎么去去操作這個IP核

2019-08-25 17:35:20

、編譯和調試程序。Nios II IDE提供了一個統一的開發平臺,用于所有Nios II處理器系統。僅僅通過一臺PC機、一片Altera的FPGA以及一根JTAG下載電纜,軟件開發人員就能夠往Nios

2015-09-08 22:35:45

II軟核,可以直接放在FPGA中,它體現了把實現產品的全部單元電路集成到一個芯片之內的片上系統SOPC的思想。作為一種具有競爭力的技術,在國外已經有大量的產品使用了這種技術,在國內使用Nios II

2019-05-29 05:00:04

4為UPFC控制器IP核輸出的實際波形圖。4 結束語本UPFC控制器IP能使輸出正弦波頻率跟電網頻率保持一致,且輸出正弦波的幅值和相位可根據需要進行調節;輸出的三角載波的頻率、幅值和相位保持不變。同時,將UPFC控制器IP核和Nios II相結合還可提高系統的抗干擾能力。

2019-06-03 05:00:05

Nios II 軟件開發參考手冊

Nios II 軟件開發參考手冊

Nios II 軟件開發參考手冊

2007-06-05 18:56:43 120

120 首先介紹嵌入式實時操作系統μC/OS-II 和Nios 嵌入式處理器, 分析μC/OS-II 移植對目標處理器的要求, 重點介紹μC/OS-II 在Nios 處理器上的移植過程,最后在Nios 開發板上對移植工

2011-03-08 09:31:38 90

90 首先介紹嵌入式實時操作系統μC/OS-II 和Nios 嵌入式處理器, 分析μC/OS-II 移植對目標處理器的要求, 重點介紹μC/OS-II 在Nios 處理器上的移植過程,最后在Nios 開發板上對移植工作進行

2009-05-16 14:32:43 28

28 基于Nios II的自動指紋識別系統設計:介紹基于Nios II處理器的嵌入式自動指紋識別系統的實現方法;具體說明自動指紋識別系統的基本原理、系統總體結構、硬件結構設計、用戶自定

2009-06-25 08:16:23 22

22 介紹了基于NIOS II 軟核處理器的SOPC 技術,分析了傳統方法和基于SOPC 技術的方法實現擴頻收發機的優劣,詳細說明了嵌有雙NIOS II 的SOPC 技術的方案設計。該設計增強了系統功能,改善

2009-07-22 15:35:35 0

0 介紹了一種新的基于NIOS II的導航系統的設計方案. NIOS是建立在FPGA 上的嵌入式微處理器軟核, 由于它硬件設計上的靈活性和可裁減性,使得軟件設計上“平臺”的概念延伸到硬件設計

2009-08-05 11:05:00 20

20 本文以Nios II 嵌入式軟處理器為核心,利用USB 控制芯片CH372,設計了基于Nios II 嵌入式軟處理器的USB 通信接口。本文重點介紹了USB 接口的硬件實現方案,分析了CH372 的通信流程,并

2009-08-28 11:34:28 33

33 介紹了基于NIOS II 軟核處理器的SOPC 技術,分析了傳統方法和基于SOPC 技術的方法實現擴頻收發機的優劣,詳細說明了嵌有雙NIOS II 的SOPC 技術的方案設計。該設計增強了系統功能,改善

2009-11-27 14:23:43 15

15 為了提高傳統指紋識別系統處理速度和安全問題,研究一種基于NIOS II 處理器的高速嵌入式指紋識別系統。利用NIOS II 的定制指令,FPGA 實現算法的硬件設計,同時結合先進的射頻識

2009-11-30 14:18:01 28

28 在NIOS-II 系統中A/D 數據采集接口的設計與實現摘要:進行 SOPC 開發,很有必要學習一下定制NIOS 外設的方法和技巧。本文就是基于這種目的,詳細的論述了在NIOS 系統中A/D 數據

2010-02-08 09:55:43 23

23 NIOS II軟核處理器是Altera公司推出的一款靈活高效的嵌入式處理器。該處理器的應用常見于控制和通信領域。本文描述了在NIOS II系統上實現平臺直方圖均衡算法(Plateau Equalization ,PE)

2010-08-06 15:48:40 24

24 基于Nios-II設計和實現了支持PSTN網絡、Internet網絡的雙網傳真機系統,利用FPGA實現了傳真機系統的多個電路模塊,包括A/D采樣控制邏輯、二值化圖像處理模塊、MH編碼模塊、MH譯碼模

2010-09-30 16:33:21 31

31 提出了將Altera公司的Nios II軟核嵌入到FPGA器件內部來控制高性能直接數字頻率合成器AD9858的方法,在簡要介紹Nios II和AD9858的特性的基礎上,詳細說明了系統設計電路結構和軟件設計

2010-12-09 16:23:28 31

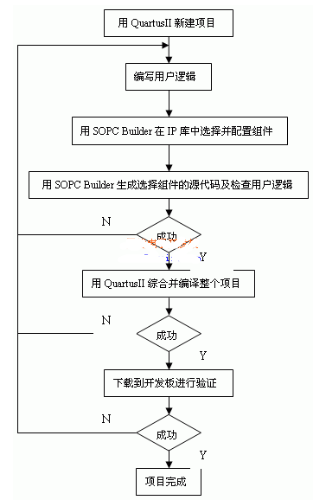

31 NIOS II的特性及開發設計流程

NIOS的主要特點NIOS II是一個用戶可配置的通用RISC嵌入式處理器。Altera推出的NIOS II系列嵌入式處理器擴展了目前

2010-02-08 14:47:31 1430

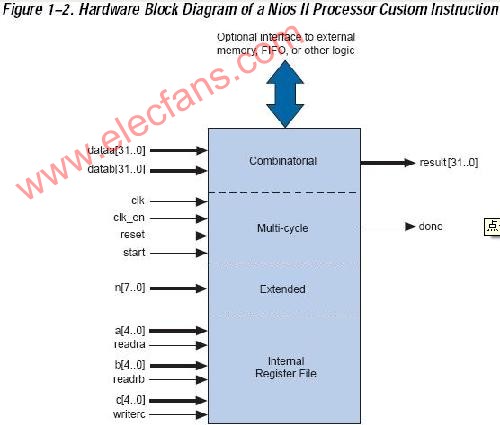

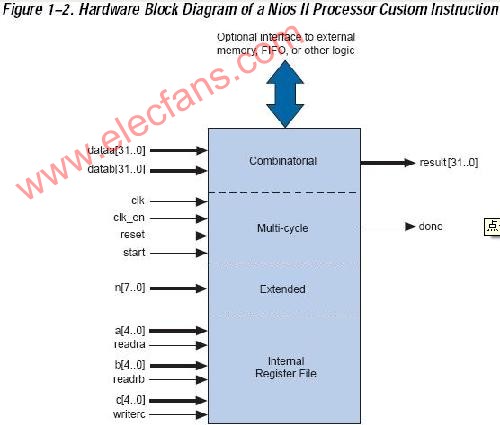

1430 NIOS II前哨計劃step by step 1(NIOS II用戶指令)

可編程軟核處理器最大的特點是靈活,靈活到我們可以方便的增加指令,這在其他SOC系統中做不到的,增加用戶指令可以把

2010-03-27 09:52:23 1040

1040

基于Nios-II設計和實現了支持PSTN網絡、Internet網絡的雙網傳真機系統,利用FPGA實現了傳真機系統的多個電路模塊,包括A/D采樣控制邏輯、二值化圖像處理模塊、MH編碼模塊、MH譯碼模

2010-06-23 11:13:10 1795

1795

0 引言

NIOSⅡ是Altera公司推出的第二代IP軟核處理器。它與其他IP核可構成SOPC系統的主要部分。Altera SOPC Builder提供有NiosⅡ處理器及一些常用外設接口,因此,對于一

2010-08-16 09:44:23 1476

1476

基于Nios II/

2011-01-09 20:59:04 29

29 摘要! 主要闡述了以FPGA為核心的基于NIOS II軟核的嵌入式LCD圖形顯示設計 方法$ 從系統的角度提出在LCD上顯示圖形的設計過程#給出搭建NIOS II軟核的系統整體結構圖#并 最終實現了圖形以及漢字在LCD上的顯示最后總結出利FPGA技術實現LCD 圖形顯示的優勢$

2011-02-11 14:17:40 42

42 Nios II內核詳細實現

2012-10-17 13:59:49 83

83 Nios II 系列處理器配置選項:This chapter describes the Nios II Processor parameter editor in Qsys and SOPC

2012-10-17 14:08:42 17

17 Nios II定制指令用戶指南:With the Altera Nios II embedded processor, you as the system designer can

2012-10-17 14:18:49 37

37 使用Nios II緊耦合存儲器教程 Chapter 1. Using Tightly Coupled Memory with the Nios II Processor Reasons

2012-10-17 14:43:25 48

48 怎樣使用Nios II處理器來構建多處理器系統 Chapter 1. Creating Multiprocessor Nios II Systems Introduction to Nios II

2012-10-17 14:51:06 19

19 電子發燒友網核心提示 :當您采用Nios II 嵌入式處理器進行設計時,您所使用的將是由Altera及其合作伙伴提供的可靠的軟件開發工具和軟件組件。 Nios II 嵌入式設計包 Nios II嵌入式設計

2012-10-17 15:31:13 1704

1704

為了實現對嵌入式系統中大量數據存儲的需求,提出了一種基于NIOS II的SD卡存儲系統設計方案,并完成系統的軟硬件設計。該存儲系統使用SPI模式對SD卡進行讀寫訪問,SPI時序由NIOS II的

2013-07-25 16:19:49 66

66 NIOS II 常見問題總結,如果你想要Altera的FPGA做嵌入式設計,肯定要涉及到NIOS II的使用,本文總結了一些NIOS II的常見問題與解決方法

2015-12-01 15:43:34 14

14 在 Nios II 中根據需求定制基于 Avalon 總線的 IP 核模塊,并使用定制的模

塊實現對數碼管的控制。通過本章,你能學到

(1)在 Nios II 中定制基于 Avalon 總線的 IP 核模塊。

(2)在 Nios II 中控制數碼管。

2015-12-14 15:39:39 3

3 NIOS_II各種性能表格對NIOS_II內核在各種型號的FPGA上的實現的性能說明

2015-12-21 17:19:15 22

22 介紹Modular Scatter-Gather DMA IP及如何與 Nios II 處理器搭配使用

2018-06-22 09:38:00 3030

3030

本文檔的主要內容詳細介紹的是如何制作一個方便在Quartus II和Nios II中使用的簡單IP。

2019-07-09 17:40:00 2

2 隨著電路規模越來越大,片上系統(SoC)已經成為IC設計的發展趨勢,相應地也有了更加靈活的片上可編程系統(SOPC)。Nios II CPU是一個基于流水線設計的通用RISC微處理器,擁有五級流水線

2020-04-11 17:01:12 1353

1353

本文論述了一種基于Nios II的可重構DSP系統設計。

2021-05-05 03:03:00 982

982

電子發燒友網站提供《基于NIOS II的SD卡讀寫控制設計.pdf》資料免費下載

2023-11-06 10:06:43 1

1

電子發燒友App

電子發燒友App

評論