DDS技術的工作原理是什么?DDS信號源如何應用于掃頻測試技術?如何進行模擬濾波器頻響測試?如何進行高分辨率數字濾波器的頻響測試?

2021-04-15 06:53:06

FPGA實現直接數字頻率合成(DDS)的原理、電路結構和優化方法介紹了利用現場可編程邏輯門陣列FPGA實現直接數字頻率合成(DDS)的原理、電路結構和優化方法。重點介紹了DDS技術在FPGA中的實現

2012-08-11 18:10:11

的數目之外,就是采用可編程邏輯器件,主要是FPGA芯片來實現。本課程以DSP設計在FPGA芯片上的開發為主線,遵照由淺入深的基本步驟和思路進行詳細講解,每一個知識點都給出了基于ISE(HDL語言

2009-07-21 09:22:42

級防護技術,深入研究與分析在FPGA平臺上實現針對DPA攻擊的電路級防護技術。1 FPGA上的電路防護技術1.1 FPGA的底層結構FPGA的簡化結構如圖1所示。FPGA內部最主要的、設計工程中最

2018-10-18 16:29:45

基于FPGA的嵌入式系統的開發工具包。本文介紹基于SoPC的波形發生器在EDK工具包下的設計與實現。本設計采用嵌入式軟處理器核 MicroBlaze以及自主編寫的包括實現DDS在內的多種IP Core

2009-06-25 08:12:37

GPS移動車輛監控系統存在的問題跳頻系統的組成GPS-AVL系統組網方案

2021-05-12 06:47:19

本文基于Matlab中的GUI設計了跳頻OFDM系統,界面設計友好,能夠動態地改變系統參數進行仿真,結果顯示該設計系統能夠很好地進行實時仿真,實用性較強。

2020-03-09 08:02:13

數字調諧濾波技術發展現狀如何?跳頻濾波技術原理及方案,不看肯定后悔

2021-05-26 06:21:42

,以確保通過擁塞的無線電頻譜進行有效的通信。其中最主要的是軟件定義的無線電(sdr) ,它使軟件能夠動態控制通信參數,如所用的頻帶、調制類型、數據速率和跳頻方案。 軍用無線電應用經常采用軟件無線電技術

2021-12-29 09:31:37

我是通信專業學,最近對跳頻通信技術感興趣,有沒有大神推薦一些介紹跳頻通信技術的文獻給我啊。 有沒有比較簡單的跳頻器設計方案呢?

2013-04-06 23:01:08

的AD985X系列)。從而為電路設計者提供了多種選擇。但在某些場合,專用DDS芯片在控制方式、置頻速率等方面與系統的要求仍然有很大差距,在這種情況下,采用高性能的FPGA器件設計符合自己需要的DDS

2019-06-18 06:05:34

的FFT設計,精度達到10-6。大大縮小了接收機體積,便于系統實現小型化、集成化。捕獲及跳頻同步等算法采用硬件實現,加快了捕獲跟蹤速度。實驗結果表明FPGA系統設計是正確可行的。

2021-02-22 07:36:49

,310-118.....),且每次掃頻要停到高端頻率。實現方法:采用DRG的非駐留模式,將非駐留低位0x01[18:17]設為[0:1],然后每個周期的啟示完成寫數據和更新后,再開始控制DRCTL下降沿觸發掃頻。遇到的問題:在

2018-10-18 10:27:53

ADI技術人員以及論壇同仁們:我正在使用AD9914快速跳頻功能,采用32位直接DDS內核參數訪問方式,無需I/O更新即可跳頻,但是該功能不能保證每次跳頻時相位為零,請問如果需要每次跳頻時保證相位為

2019-01-02 11:24:07

請問跳頻的實現機制是怎么樣?比如說接收機如何事先知道發射機的跳頻表,跳頻表是隨機生成的還是固定模式的?等。能否通過這個例程實現多發一收這樣的機制?

2022-08-23 06:09:20

WIFI的跳頻機制怎么實現的?想了解WIFI的跳頻機制怎么實現的。網上資料比較少啊!有些WIFI模塊好像都是固定工作在一個頻段的,要改頻段得自己設置,不知道WIFI有沒有通用的一些跳頻機制來防止數據碰撞,求指點

2016-03-15 17:55:53

處理器的數目之外,就是采用可編程邏輯器件,主要是FPGA芯片來實現。本課程以DSP設計在FPGA芯片上的開發為主線,遵照由淺入深的基本步驟和思路進行詳細講解,每一個知識點都給出了基于ISE(HDL語言

2009-07-21 09:20:11

處理器的數目之外,就是采用可編程邏輯器件,主要是FPGA芯片來實現。本課程以DSP設計在FPGA芯片上的開發為主線,遵照由淺入深的基本步驟和思路進行詳細講解,每一個知識點都給出了基于ISE(HDL語言

2009-07-24 13:07:08

頻率合成技術)產生掃頻信號,以XilinxFPGA為控制核心,通過A/D和D/A等接口電路,實現掃頻信號頻率的步進調整、幅度與相位的測量,計算機軟件作為儀器面板來顯示被測網絡幅頻特性與相頻特性的功能,并且測試結果可保存到各種存儲介質中。報名有點晚了,設計方案寫的很詳細,歡迎大家提意見和建議!!!

2012-07-07 11:09:41

發生器。函數信號發生器的實現方法通常是采用分立元件或單片專用集成芯片,但其頻率不高,穩定性較差,且不易調試,開發和使用上都受到較大限制。隨著可編程邏輯器件(FPGA)的不斷發展,直接頻率合成(DDS)技術

2012-05-12 23:01:54

各位FPGA用戶大家好,為了給本版塊營造更良好的學習氛圍,現特邀請我們的版主小梅哥帶我們一起做項目【基于DDS技術的信號發生器系統】 歡迎大家一起跟帖交流學習!題目:設計一個基于DDS技術的信號

2014-12-09 16:31:29

、工程設計等系統信號源的首選。在擴頻和跳頻系統、數字廣播、高清晰度電視、線性調頻以及儀器儀表以及電子測量等領域。DDS已經逐步成為高性能信號源發生器的核心技術Ill。本文提出了一種基于AT89S52

2011-03-08 13:37:06

,而且還可以現場開發新波形。在商業方面,可實現移動通信的無縫接入和完全自由的個人通信,縮短系統的開發周期和降低運營商的成本,現已成為3G和4G所采用的一項關鍵技術。 本文研究了中頻軟件無線電的實現方案

2019-05-28 06:39:46

為什么要使用無線跳頻技術?需要注意哪些事項?

2019-08-16 06:59:15

限,因此在設計工作頻率寬、調協精度高的頻率合成器時,這兩種方式均不能滿足技術要求。但是,采用DDS+PLL方式,可以滿足高精度和寬頻帶的需要,其實現的難點是如何提高合成器輸出頻譜純度。在實際印制電路板制作中,DDS的良好接地和合理布線非常有助于系統設計的實現。來源:與非網

2011-07-16 09:09:54

本人剛剛學習跳頻技術,對跳頻技術不是很了解,現在想將跳頻技術與DSP進行融合,不知道哪位大俠可以給我指點指點。希望哪位高手給我一份關于DSP驅動DDS的例程,本人不勝感激!!!!!!!!

2012-10-20 17:14:08

本人是剛剛開始接觸跳頻,想購買一塊跳頻通信技術的開發板,想請各位給小弟我介紹下,非常感激!!!!!

2012-11-06 17:00:03

脈寬調制技術(PWM)目前廣泛應用在電力、電子、微型計算機、自動控制等多個學科領域。本設計采用基于FPGA的直接數字頻率合成(DDS)技術,通過D/A轉換進行程控放大,實現了三相功率可控的PWM信號。

2019-08-26 06:54:24

的調整、校準及故障排除提供了極大的便利。北京普源精電(RIGOL)最新推出的DG5000 系列函數/任意波形發生器采用了DDS 直接數字合成技術,可生成穩定、精確、純凈和低失真的輸出信號。本文僅以

2019-06-06 07:39:43

信息顯示在LCD液晶顯示屏上。各硬件模塊之間的協調工作通過嵌入式軟核處理器NiosⅡ用編程實現控制。本設計所搭建的LCD12864控制器是通過編程實現的IP核。關鍵詞:DDS;FPGA技術;順序存儲;NiosⅡ;IP核

2019-06-21 07:10:53

跳頻技術是一種具有高抗干擾性、高抗截獲能力的擴頻技術。接收系統是跳頻通信系統中非常重要的部分,自適應跳頻技術、高速跳頻技術、信道編碼技術、高效調制解調技術成為近年來跳頻技術發展的新動態,基于FPGA的跳頻通信接收系統研究有很高的應用價值。

2019-09-25 06:15:14

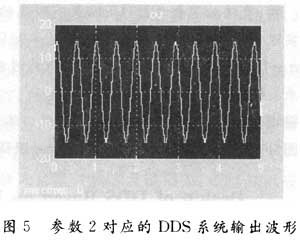

仿真及功能驗證。DDS電路、掃頻信號的控制及顯示電路均集成在FPGA中實現了片內集成,不僅減小了電路尺寸,而且還增強了抗干擾性,使可靠性得到了進一步的提高。該掃頻信號源克服了傳統掃頻信號源電路復雜、價格昂貴、體積龐大等缺點,具有掃頻和點頻兩種頻率輸出方式及測頻、掃速控制等功能。

2019-07-04 07:42:59

,希望有興趣的同志和我聯系!FPGA以太網傳輸系統介紹:1)平臺:ALTERA FPGA,cyclone系列器件即可支持;2)系統架構:硬件:FPGA + PHY,其中MAC在FPGA中以IP方式實現

2014-06-19 12:04:25

,希望有興趣的同志和我聯系!FPGA以太網傳輸系統介紹:1)平臺:ALTERA FPGA,cyclone系列器件即可支持;2)系統架構:硬件:FPGA + PHY,其中MAC在FPGA中以IP方式實現

2014-06-19 12:06:43

本文將介紹的系統采用相檢寬帶測頻技術,不僅實現了對被測信號的同步,也實現了對標頻信號的同步,大大消除了一般測頻系統中的±1個字的計數誤差,并且結合了現場可編程門陣列(FPGA),具有集成度高、高速和高可靠性的特點,使頻率的測量范圍可達到1Hz~2.4GHz,測頻精度在 1s閘門下達到10-11數量級。

2021-04-13 06:47:13

外設及其他功能部件,內部時鐘頻率可達到48 MHz。具有增強型的SPI 接口,可方便實現對nRF905 的控制。 2.1.2 跳頻通信模塊硬件電路 跳頻通信模塊硬件電路采用Nordic 公司推出

2011-08-04 09:52:58

跳頻通信系統作為擴頻通信體制中的一種重要類型,以其出色的抗遠近效應、抗干擾能力,在軍用、民用通信領域得到了廣泛應用。跳頻通信方式是指載波受一偽隨機碼的控制, 不斷地、隨機地跳變,可看成載波按照一定

2019-10-15 07:39:47

。近年來隨著半導體工藝和計算機技術的發展,dsp(Digital Signal Processor)、FPGA(Field Programmable Gates Array)等現代信號處理芯片越來越成熟和普遍使用,以前只能理論研究的跳頻技術有了實現的可能。

2019-08-28 07:13:20

。近年來隨著半導體工藝和計算機技術的發展,dsp(Digital Signal Processor)、FPGA(Field Programmable Gates Array)等現代信號處理芯片越來越成熟和普遍使用,以前只能理論研究的跳頻技術有了實現的可能。

2019-08-29 06:24:01

跳頻通信系統作為擴頻通信體制中的一種重要類型,以其出色的抗遠近效應、抗干擾能力,在軍用、民用通信領域得到了廣泛應用。

2019-10-16 08:03:45

通信網位同步方案——隙同步的方法,并基于TI公司TMS320C54X系列DSP,采用TMS320匯編語言對隙同步方案進行了硬件實現和分析。仿真結果表明:隙同步原理能較好地解決跳頻通信網中接收端的位同步

2021-07-16 07:00:00

通信系統的各種功能。短波高速跳頻電臺具有強抗干擾與抗截獲能力,在軍事上有極為重要的應用。本文介紹了軟件無線電技術應用于短波高速跳頻通信電臺的基本情況,闡述了跳頻通信的基本思想。在此基礎上討論了一種基于軟件無線電技術的短波高速跳頻電臺的軟硬件設計方案,指出了其廣闊的應用前景,并提出了進一步實現的建議。

2017-08-02 19:42:27

1.基帶跳頻和射頻跳頻原理2.基帶跳頻和射頻跳頻優缺點

2013-05-22 15:07:56

針對數據處理速度越來越高的要求,本文提出了基于FPGA+DDS的控制設計,能夠快速實現復雜數字系統的功能。

2021-04-30 06:17:49

硬件實現KEELOQ技術的加密過程HCS301跳碼編碼器的管腳及其功能TDH6301跳碼譯碼器的管腳及其功能HCS301的應用電路

2021-04-08 06:11:11

直接數字頻率合成器DDS具有哪些特點?DDS基本原理及工作過程解析采用VHDL硬件實現DDS的優化設計與實現

2021-04-12 06:28:28

DDS電路的工作原理是什么如何利用FPGA和DDS技術實現正弦信號發生器的設計

2021-04-28 06:35:23

跳頻通信是在惡劣的電磁環境中保證正常通信的主要手段。提高跳頻通信系統的跳頻速率和跳頻帶寬可以有利于對抗單頻窄帶干擾,頻帶阻塞干擾以及跟蹤干擾,是提高跳頻通信系統抗干擾能力的主要手段。

2019-08-22 06:01:11

介紹了利用現場可編程邏輯門陣列FPGA實現直接數字頻率合成(DDS)的原理、電路結構和優化方法。重點介紹了DDS技術在FPGA中的實現方法,給出了采用ALTERA公司的ACEX系列FPGA芯片EP1K30TC進行直接數字頻率合成的VHDL源程序。

2021-04-30 06:29:00

跳頻技術是一種具有高抗干擾性、高抗截獲能力的擴頻技術。接收系統是跳頻通信系統中非常重要的部分,自適應跳頻技術、高速跳頻技術、信道編碼技術、高效調制解調技術成為近年來跳頻技術發展的新動態,基于FPGA的跳頻通信接收系統研究有很高的應用價值。

2019-09-30 08:11:55

)fref (4) 當失鎖時,采用寬的環路濾波器,進行快速捕獲。鎖定后,切換到窄的環路濾波器,從而提高系統的跳頻時間、雜散以及遠端的相位噪聲。 3 改進型DDS驅動PLL電路實現 3.1 可變DDS

2020-12-03 16:06:44

。

Bluetooth采用跳頻擴頻(FHSS)技術,使用79個信道,每個信道占用1MHz,信號不斷以1600Hz的速率在79個調頻點間隨機跳躍,藍牙信號實際上占用79MHz頻帶。

3. WiFi

2023-05-10 16:15:10

簡單跳頻技術移動通信的跳頻要求用multisim軟件仿真 求大神解{:1:}

2013-06-17 18:58:26

求助。設計一個FM跳頻通信系統,實現通信保密。包括實現語音通信、載波范圍可調、頻點可調。

2014-03-21 16:52:48

,分頻后的時鐘波形在時鐘的上升沿對信號進行采樣,那么就會得到如圖1(a)中所表示的等效時間采樣。等效時間采樣技術的原理作用及采用FPGA器件實現系統的設計圖1 等效時間采樣示意圖2 、基于FPGA的等效

2020-10-21 16:43:20

本人菜鳥 學fpga沒多長時間,現在小弟有個問題想請教各位 希望各路大神給點建議 我現在想做個DDS 想通過FIFO和DDS來實現掃頻功能,基本的邏輯就是FIFO發個數給DDS 讓DDS發出正弦波

2014-05-27 09:12:18

在DDS系統中通過DDS內部倍頻得到芯片參考時鐘,內部倍頻是否對輸出信號有影響,比如說AD9951采用100M晶振然后芯片內部4倍頻得到參考時鐘,經過測試,輸出信號經過濾波之后存在100M頻率分量,總是不能完全抑制,這是什么原因導致的呢???

2018-09-26 14:15:33

我現在想要通過DDS實現靈活的調制輸出:1、(比如中心頻率250Khz,+-50Khz范圍內)線性掃頻功能2、(比如中心頻率250Khz,+-50Khz范圍內)隨機頻率掃頻或者periodic

2018-08-18 07:14:37

怎樣去設計一種跳頻OFDM系統?如何對跳頻OFDM系統進行仿真?

2021-05-20 07:05:48

請教下各位大神,能否用AD9910的單音模式來實現中心頻率60MHz,帶寬10MHz的跳頻了,我的想法的是:通過PN碼發生器,按照一定的順序隔一段時間就向Profile寄存器中寫入指定頻率的FCW

2018-10-22 09:22:30

的頻帶,但是時鐘頻率較高的DDS價格昂貴。采用鎖相環合成,雜散性能與相位噪聲性能較好,可實現的工作頻帶寬,但頻率切換速度較慢,跳頻時間較長。由于系統并沒有對頻率切換速度提出過高要求,因此從價格方面考慮

2019-06-21 06:32:34

基于FPGA的DDS信號源設計與實現

利用DDS和 FPGA 技術設計一種信號發生器.介紹了該信號發生器的工作原理、 設計思路及實現方法.在 FPGA 器件上實現了基于 DDS技

2010-02-11 08:48:05 223

223 基于DSP Builder的DDS設計及其FPGA實現

直接數字合成器,是采用數字技術的一種新型頻率合成技術,他通過控制頻率、相位增量的步長,產生各種不同頻率的信號。他具

2010-01-14 09:43:55 1292

1292

采用雙運算核在FPGA硬件平臺上實現小波變換模塊。采用單一時鐘,在不增加系統設計復雜性和功耗的情況下,使得系統達到實時處理的要求。系統通過仿真驗證,工作穩定可靠。

2011-12-07 13:59:56 22

22 討論一種基于DSP系統,利用FPGA設計接口通過DDS芯片產生MSK調制的方法,使用該方案的硬件電路簡潔且易于實現調制器的小型化。

2012-02-09 15:14:46 11

11 首先介紹了采用直接數字頻率合成(DDS)技術的正弦信號發生器的基本原理和采用FPGA實現DDS信號發生器的基本方法,然后結合DDS的原理分析了采用DDS方法實現的正弦信號發生器的優缺點

2012-11-26 16:23:32 49

49 利用現場可編程門陣列(FPGA)設計并實現直接數字頻率合成器(DDS)。結合DDS 的結構和原理,給出系統設計方法,并推導得到參考頻率與輸出頻率間的關系。DDS 具有高穩定度,高分辨率和高轉換速度,同時利用Altera 公司FPGA 內的Nios 軟核設置和顯示輸出頻率,方便且集成度高。

2016-04-01 16:14:19 24

24 詳細介紹了直接數字頻率合成器(DDS)的工作原理、基本結構。在參考DDS 相關文獻的基礎上,提出了符合結構的DDS 設計方案,利用DDS 技術設計了一種高頻率精度的多波形信號發生器,此設計基于可編程邏輯器件FPGA,采用Max+PlusⅡ開發平臺,由Verilog_HDL 編程實現。

2016-11-22 14:35:13 0

0 不同的應用領域,對DDS的性能有不同的要求。當把DDS用做雷達系統中的本振信號源時,對寄生信號抑制的要求可能比較高,如要求在60dB或70dB以上。當把DDS用于雷達干擾系統時,除了對寄生信號抑制有一定的要求外,更重要的是其產生寬帶信號的能力。

2018-10-07 11:14:14 7103

7103

DDS基于FPGA的DDSSPI系統結構功能實現:在SPI接口下掛接上DDS模塊,通過單片機向FPGA發送頻率字實現任意頻率正弦波的波形,并通過DAC模塊輸出單片機部分通過按鍵輸入待產生的信號頻率

2021-12-01 17:36:17 9

9

電子發燒友App

電子發燒友App

評論