隨著IC制造工藝水平的快速發展,片上系統(SOC)在ASIC設計中得到廣泛應用。微處理器IP核是SOC片上系統的核心部分。但是大多數公司和研究機構沒有足夠的財力與人力開發自己的處理器,所以業界比較流行的做法就是購買微處理器的IP核,例如ARM核或MIPS核,但需要數十萬美金的許可證費用的投入。

除了昂貴的ARM核與MIPS核以外,我們還有另外一種選擇,就是選擇開放源代碼的微處理器的IP核。目前可以實際使用的開放源代碼處理器有LEON系列與OPENRISC系列兩種。本文就介紹了LEON2微處理器核,快速的建立起一個SOC的平臺的原型對于驗證系統性能與加快軟件開發都是相當重要的。本文還詳細闡述了如何在Altera的FPGA開發板上建立基于LEON2微處理器的SOC原型平臺。

1 、LEON2微處理器

LEON處理器系列是歐洲航天局的下屬的研究所開發的32位微處理器,應用在航天局的各種ASIC芯片內。目前有LEON2,LEON3系列。LEON系列處理器是一個可配置,可綜合適于在SOC設計中應用的微處理器核。LEON2處理器是一個使用SPARC V8指令集的32位的RISC處理器,它的源代碼由可綜合的VHDL代碼構成。同時LEON2的性能也很不錯,使用Dhrystone2.1的測試平臺,LEON可以達到大約0.85MIPS/MHz。更大的好處是LEON處理器是一個公開源代碼,遵循GNU LGPL協議。任何人都可以其網站上免費下載其硬件代碼和各種開發軟件工具與相關文檔。并且在自己ASIC項目中使用。

LENO2的處理器具有以下的特點:

內部使用了5級流水線,兼容SPARC V8指令集。

具有硬件乘法,除法和MAC的功能。

具有分開的指令和數據cache結構(哈佛結構),可以根據需求靈活的配置cache的容量,大小范圍是1-64kbyte。

片上總線規范使用了AMBA2.0規范,支持APB,和AHB標準。

具備一些片上常用外設,包括UART,中斷控制,I/O端口,實時時鐘,看門狗等。

支持硬件調試功能。

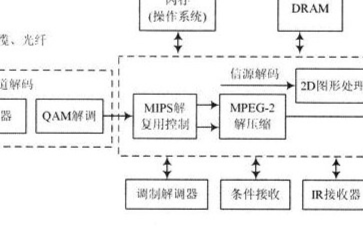

圖1是LEON2的結構框圖,虛線部分內是LEON2處理器的組成部分。

圖1 LEON處理器的結構框圖

從上面的介紹可以看出,LEON2的性能相當不錯,但是作為一個處理器,除了本身的性能以外,同時還必須要有高效的編譯器軟件開發環境,各種應用軟件和操作系統的支持。ARM和MIPS在嵌入式的廣泛應用,與其背后的高效的軟件編譯開發工具,以及眾多支持ARM和MIPS的實時操作系統軟件有很大關系。很多公司選擇ARM或MIPS,不僅看重微處理器的性能,更大的方面是看重其背后的軟件支持環境。雖然LEON系列在這一點上不如商用微處理器,但是也是相當不錯了。和硬件代碼一起,可以下載LECCS,一個基于GCC的免費的C/C++的交叉編譯系統,同時也可以使用GDB調試工具做源代碼級別的調試。開源社區還提供免費的實時系統RTEMS,UClinux,eCos等免費實時操作系統。上述實時操作系統都已在LEON2處理器上移植成功了。

由于LEON2處理器的源代碼是公開的,任何人都可以免費得到和使用。很多研究機構和公司沒有自己的處理器的核,如果去開發,需要大量的人力物力支持,而且附帶的各種軟件編譯器的開發也需要大量的工作,對于中小型的公司或研究院很難做到。如果通過購買ARM或者MIPS的核,通常都需要幾十萬美金的許可證的費用,同時以后的產品也必須要付一定的費用。而LEON系列處理器就給了這些公司和研究機構另外的一種選擇。雖然在功耗和性能上同常用的ARM,MIPS等處理器還有些不足,但是完全可以使用。LEON處理器是經過了多個ASIC芯片流片成功的實踐檢驗。目前基于LEON系列的ASIC芯片也有幾十個項目。

2 、在FPGA開發板上建立基于LEON2的SOC原型平臺

隨著片上系統復雜性的不斷增加,為了克服片上系統(SOC)設計的挑戰,半導體業界正在采取一種基于系統原型的平臺設計方法。這種方法就是通過將片上系統映射到FPGA,這樣可以在接近運行速度的前提下,驗證硬件和軟件。這樣不僅給為軟件部分能盡早的進行開發與調試工作提供了一個原型,同時也可以在實際運行中發現一些在系統設計中沒有注意的地方。這樣最終可以縮短設計周期,同時為ASIC設計一次成功提供了更大的把握。

在我們的設計中,為了上述的目的,所以決定在FPGA開發板上建立基于LEON2處理器的SOC平臺。使用這個原型系統,就可以很容易驗證系統的性能,并且加速軟件開發調試流程。圖2 就是我們的一個基于LEON2的平臺的模塊框圖。LEON2處理器作為核心部分,片內ROM存放monitor負責系統初始化和將程序拷貝到片外SRAM內的任務,片外RAM是FPGA開發板上memory,用來存放程序和數據。我們自己設計的IP核通過AHB總線和LEON2相互交互。

FPGA開發板是Altera公司的FPGA開發板NIOS。板上主要有以下資源,一塊APEX20KE的FPGA,256K字節的RAM(2個64K*16bit的片子),JTAG接口(通過JTAG接口我們可以從PC機上對APEX20KE進行編程),串行口和計算機的COM1口相連。APEX20KE是Altera公司的可編程邏輯器件,標準門數為20萬門左右,片上可配置RAM或ROM為10K。

開發流程如圖3開發流程圖。

硬件流程: LEON2軟核用VHDL代碼編寫的,和我們的VHDL設計文件一起使用Synplify綜合工具生成FPGA的網表文件,然后使用Altera公司的布局布線和下載的工具Quartus生成相應的SOF文件。通過JTAG端口將SOF文件下載到片子上去。對FPGA硬件進行配置。由于Quartus軟件可以預先配置APEX20KE片上ROM,所以我們可以利用這一點,在LEON2的片上ROM預先配置好1K大小的Monitor軟件。

軟件開發流程,當軟件代碼完成以后,使用LEON2的基于GCC的LECCS交叉編譯系統對C代碼編譯,得到二進制代碼以后,就可以通過串行口下載到FPGA開發板上。

3 、軟硬件詳細設計

在LEON的開發網站上可以下載VHDL代碼, LEON2是一個可配置的處理器核,可以根據具體系統的應用范圍,對處理器的性能進行權衡。例如可以將指令和數據cache進行設置,選擇從1kbyte到64kbyte的大小。同時選擇處理器是否要支持硬件乘法器。是否要有硬件debug的功能等等。圖四是LEON2的處理器配置的界面,將各個選項部分配置完畢,系統生成對應的VHDL代碼。

圖四 LEON2處理器的配置

在最終的設計中,選取了指令和數據cache分別是1kbyte,不帶有硬件乘法功能的模塊。得到LEON2的VHDL代碼,然后加入我們自己設計的HDL代碼,使用modelsim做簡單的功能仿真。等功能仿真通過后,使用synplify對VHDL綜合,應用 APEX20KE器件,最終的綜合結果是:占用 FPGA資源是5800個LE,可以達到的時鐘頻率最大46M。應當注意的是,由于APEX20KE器件是Altera公司2000年的產品,如果采用Altera新一代的FPGA器件,例如StratixII器件,時鐘頻率可以達到107M,可以滿足大多數的應用領域。

使用quartus進行布局布線時,需要將LEON2和外圍的memory連接起來, LEON2對程序存儲器和數據存儲器是統一尋址。但是在FPGA原型平臺設計時,軟件需要多次修改調試,所以不能采取將程序固化在片外flash這種做法。所以采用了圖5的結構,LEON2核同片內ROM和片外SRAM連接。其中ROM存放了一個monitor程序。由于這個部分是整個平臺正常工作的核心,所以下面我專門對它做詳細的解釋。

圖 5 LEON2與存儲器的連接

LEON2的平臺中有兩個memory,分別是片內ROM,片外SRAM,LEON2對存儲器是統一尋址的。分配如下:

Monitor的主要作用是在LEON2系統reset初始化的時候首先對處理器初始化,對LEON2的存儲配置寄存器進行配置。然后向UART口發送啟動信息,然后等待從UART信息。當軟件部分使用交叉編譯器LECCS在PC上編譯完畢后, PC機通過UART口和FPGA開發板相互通信,就可以將編譯好的srec文件下載到FPGA開發板上去,放置在片內rom里面的monitor程序就讀入程序的內容以及程序的起始地址。起先monitor將srec程序拷貝到SRAM程序區,等全部程序下載好以后, monitor最后一條程序就會自動跳轉到程序的起始位置,執行SRAM里的程序。

使用圖5的連接。由于data_to_leon[31:0]的數據線是單向的,我們使用多路復用器來選擇從外部SRAM的數據輸入或者內部ROM數據輸入和data_to_leon[31:0]相互連接,使用romsn[0]來選擇。romsn[0]只有當訪問PROM時才會置低,也就是地址為0x00000000-0x1FFFFFFF的時候。根據上面的描述只有系統reset初始化的時候訪問PROM,也就是romsn[0]置低,等下載的程序全部都拷貝到SRAM程序區以后,monitor會控制LEON2處理器跳轉到程序的起始位置,也就是片外的SRAM內,這時候romsn[0]保持高電平,也就是data_to_len[31:0]于ram_datain[31:0]連接。這樣系統就只會接收外部SRAM的數據。

也就是,程序下載完畢后,就只會執行下載的程序。這樣就可以反復修改程序,反復下載程序。可以在利用這個原型平臺開發和調試軟件硬件程序。

最終,在FPGA里根據上面圖5的連接將LEON2分別和片內ROM,片外SRAM相互連接,其中片內rom放入了前面所說的monitor的程序。使用quartus做布局布線和下載。最終在FPGA開發板上建立了LEON2的SOC原型平臺,系統可以穩定的工作在33M的時鐘下,并且由于FPGA的可多次配置的特性,極大的方便了軟件模塊和硬件模塊的開發調試工作。

4 、總結和題外話

上面的內容論述了如何利用Altera的FPAG開發板資源,使用開放源代碼的LEON2微處理器,建立一個基于LEON2的SOC原型開發平臺。并且從軟件結構和硬件設計的兩個方面詳細介紹了這個平臺的建立。經過實際使用,完全滿足要求,加快了我們的項目開發進度。

責任編輯:gt

電子發燒友App

電子發燒友App

評論