我們為什么需要高層次綜合

高層次綜合(High-level Synthesis)簡稱 HLS,指的是將高層次語言描述的邏輯結構,自動轉換成低抽象級語言描述的電路模型的過程。所謂的高層次語言,包括 C、C++、SystemC 等,通常有著較高的抽象度,并且往往不具有時鐘或時序的概念。相比之下,諸如 Verilog、VHDL、SystemVerilog 等低層次語言,通常用來描述時鐘周期精確(cycle-accurate)的寄存器傳輸級電路模型,這也是當前 ASIC 或 FPGA 設計最為普遍使用的電路建模和描述方法。

然而,HLS 技術在近十年來獲得了大量的關注和飛速的發展,尤其是在 FPGA 領域。縱觀近年來各大 FPGA 學術會議,HLS 一直是學術界和工業界研究最集中的領域之一。究其原因,主要有以下幾點。

第一,使用更高的抽象層次對電路建模,是集成電路設計發展的必然選擇。集成電路伴隨摩爾定律發展至今,其復雜性已經逐漸超過人類可以手工管理的范疇。例如,蘋果 iPhone11 內置的 A13 芯片,就有著約 85 億支晶體管。

然而,根據 NEC 2004 年發布的研究,一個擁有 100 萬邏輯門的芯片設計通常需要編寫 30 萬行 RTL 代碼。因此,完全使用 RTL 級的邏輯抽象設計當代芯片是不現實的,并將對設計、驗證、集成等各個環節造成巨大的壓力。

相比之下,使用諸如 C、C++等高層語言對系統建模,可以將代碼密度壓縮 7 到 10 倍,這極大的緩解了設計復雜度。

第二,高層語言能促進 IP 重用的效率。傳統的基于 RTL 的 IP 往往需要定義固定的架構和接口標準,在 IP 重用時需要花費大量時間進行系統互聯和接口驗證。相比之下,高層語言隱藏了這些要求,轉而由 HLS 工具負責具體實現。

對于 FPGA 而言,現代 FPGA 里有著大量成熟的 IP 單元,如嵌入式存儲器、算術運算單元、嵌入式處理器,以及最近逐漸興起的 AI 加速器、片上網絡系統等等。這些 FPGA IP 有著固定的功能和位置,因此可以被 HLS 工具充分利用,在提升 IP 重用效率的同時,簡化綜合算法、提高綜合后電路的性能。

第三,HLS 能幫助軟件和算法工程師參與、甚至主導芯片或 FPGA 設計。這是由于 HLS 工具能封裝和隱藏硬件的實現細節,從而使軟件和工程師能專注于上層算法的實現。對于硬件工程師而言,HLS 也能幫助他們進行快速的設計迭代,并專注于對性能、面積或功耗敏感的模塊和子系統的優化設計。

FPGA 高層次綜合的前世今生

伴隨集成電路的復雜性的飛速增長,芯片設計方法學也在不斷演進。早在 FPGA 出現之前,人們就已經開始嘗試擺脫依靠人工檢視芯片版圖的設計方法,轉而探索使用高層語言對電路邏輯進行行為級描述,并通過自動化工具將電路模型轉化為實際的電路設計。

在上世紀八九十年代,面向集成電路設計的 HLS 工具就已經是學術界研究的熱點。這其中比較有代表性的工作,包括卡耐基梅隆大學的 CMU-DA(design automation)工具,以及加拿大卡爾頓大學提出的 force-directed 調度算法等等。

從現在看來,這些工作為當前的電路綜合算法打下了基礎,并為后來 HLS 研究提供了很多寶貴的經驗和借鑒。然而,這個階段的 HLS 工作在成果轉化方面十分失敗,并未有效的轉化成工業實踐。一個最主要的原因,就在于“在錯誤的時間,遇上了對的人”。

當時正值摩爾定律蓬勃興起的時期,集成電路設計正在經歷史上最大的變革。在后端,自動布局布線已經逐漸成為主流;在前端,RTL 綜合也在逐漸興起。傳統電路設計工程師都紛紛開始采用基于 RTL 的電路建模方法,取代傳統的基于原理圖和版圖的設計,并由此帶來 RTL 綜合工具的飛速發展。相比之下,這個階段的 HLS 研究往往使用了特殊的編程語言,如 CMU-DA 采用的名為“ISPS”的語言,因此很難獲得那些正在和 RTL 處于“蜜月期”的工程師們的青睞。

伴隨著一段時間的沉寂,HLS 在 2000 年之后再次開始獲得學術界和工業界的關注,比較有名的工具包括 Bluespec 和 AutoPilot 等。主導這一變化的主要原因是,HLS 工具開始將 C/C++作為主要的目標語言,從而被很多不了解 RTL 的系統和算法工程師所逐漸接受。同時,HLS 工具綜合生成的結果也有了長足進步,在某些應用領域甚至可以和人工手寫 RTL 近似的性能水平。

此外,FPGA 的逐漸興起也對 HLS 的發展起到了重要的助推作用。和 ASIC 設計不同,FPGA 有著固定數量的片上邏輯資源。因此 HLS 工具不用過度糾結于 ASIC 設計中面積、性能和功耗的絕對優化,而只需要將設計合理的映射到 FPGA 的固定架構上即可。這樣,HLS 就成為了在 FPGA 上快速實現目標算法的絕佳方式。

時至今日,高層次綜合技術取得了進一步的發展。大型 FPGA 公司都推出了各自的 HLS 工具,如賽靈思的 Vivado HLS 和英特爾的 HLS 編譯器、OpenCL SDK 等。在學術界也有諸多成果涌現,如多倫多大學的 LegUp 等等。

接下來,老石將以 AutoPilot 這個 HLS 工具為例,簡單介紹高層次綜合的主要工作原理。

高層次綜合的主要工作原理

AutoESL 公司的 AutoPilot 工具,可以說是 HLS 領域最為成功的學術成果轉化案例。AutoPilot 源自于 UCLA 叢京生教授主導的 xPilot 項目,從隨后與當時負責該課題的博士生張志如(現任康奈爾大學副教授)一起創辦了 AutoESL 公司,并在 2011 年被賽靈思收購,成為了之后的 Vivado HLS。

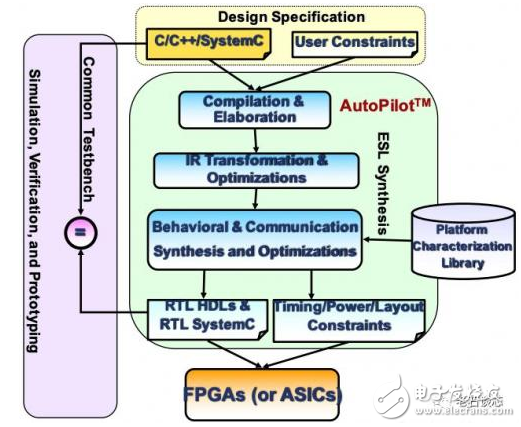

AutoPilot 的工作流程框圖如下圖所示。在前端,它使用了基于 LLVM 的編譯器架構,能夠處理可綜合的 ANSI C、C++,以及 OSCI SystemC 等語言編寫的模型。這個名為 llvm-gcc 的前端編譯器會將高層語言模型轉換為中間表達式(IR),并進行一系列針對代碼復雜度、冗余、并行性等方面的代碼優化。然后再根據具體的硬件平臺,綜合生成 RTL 代碼、驗證與仿真環境,以及必須的時序和布局約束等。

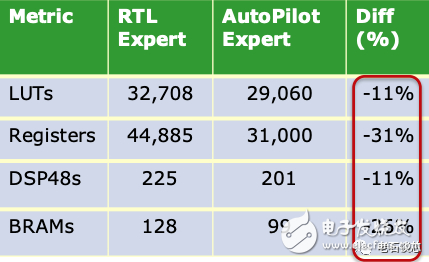

AutoPilot 的成功之處在于,它的 HLS 結果在某些應用領域完勝人工優化 RTL 取得的結果。例如,在一個無線 MIMO 系統中使用的 Sphere 解碼器 IP 中,AutoPilot 將 4000 行 C 代碼算法成功綜合到 Virtex5 FPGA 上,運行在 225MHz,并取得了比賽靈思 Sphere 解碼器 IP 更少的邏輯資源使用量,見下圖。這個結果放在現在也令人十分震撼,它很好的證明了 HLS 有潛力取得比 RTL IP 更為出色的性能。

高層次綜合工具常用的優化方法

傳統的處理器編譯器設計通常只有一個主要目標,那就是盡量提升性能。相比之下,高層次綜合工具需要統籌考慮各種電路設計的主要指標,如性能、功耗、面積等等,同時也要兼顧工具本身的性能,比如占用的資源和運行時間等。因此,在開發 HLS 工具時,要額外考慮和采用更多的優化方法,而這些優化方法也是當今學術界和工業界在 HLS 領域重點研究的方向。總的來說,HLS 工具的主流優化方法有以下幾種。

01

字長分析和優化

FPGA 的一個最主要特點就是可以使用任意字長的數據通路和運算。因此,FPGA 的 HLS 工具不需要拘泥于某種固定長度(如常見的 32 位或 64 位)的表達方式,而可以對設計進行全局或局部的字長優化,從而達到性能提升和面積縮減的雙重效果。

然而,字長分析和優化需要 HLS 的使用者對待綜合的算法和數據集有深入的了解,這也是限制這種優化方式廣泛使用的主要因素之一。

02

循環優化

循環優化一直是 HLS 優化方法的研究重點和熱點,因為這是將原本順序執行的高層軟件循環有效映射到并行執行的硬件架構的重點環節。

循環優化的最終目的,就是盡量將循環里兩次相鄰的操作以最小的時延實現,理想情況下,相鄰的循環操作可以完全并行執行。然而,由于硬件資源的限制,以及更多的是因為循環間存在嵌套和依賴關系,很難將循環完全展開。如何優化各種循環,以實現最優的硬件結構,就成為了學術界和工業界最為關心的要點。

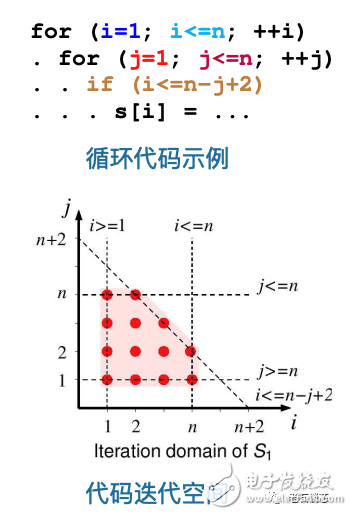

一個流行的循環優化方法,就是所謂的多面體模型,即 Polyhedral Model。多面體模型的應用非常廣泛,在 HLS 里主要被用來將循環語句以空間多面體表示(見下圖),然后根據邊界約束和依賴關系,通過幾何操作進行語句調度,從而實現循環的變換。

需要指出的是,多面體模型在 FPGA HLS 里已經取得了相當的成功,很多研究均證明多面體模型可以幫助實現性能和面積的優化,同時也能幫助提升 FPGA 片上內存的使用效率。

03

對軟件并行性的支持

C/C++與 RTL 相比,一個主要的區別是,前者編寫的程序被設計用來在處理器上順序執行,而后者可以通過直接例化多個運算單元,實現任務的并行處理。隨著處理器對并行性的逐步支持,以及如 GPU 等非處理器芯片的興起,C/C++開始逐漸引入對并行性的支持。例如,出現了 pthreads 和 OpenMP 等多線程并行編程方法,以及 OpenCL 等針對 GPU 等異構系統進行并行編程的 C 語言擴展。

因此作為 HLS 工具,勢必要增加對這些軟件并行性的支持。例如,LegUp 就整合了度 pthreads 和 OpenMP 的支持,從而可以實現任務和數據層面的并行性。

另外,Altera 在被英特爾收購之前就已經推出了 OpenCL SDK,可以將 OpenCL 進行高層次綜合,并生成 FPGA 電路邏輯與 CPU 代碼兩部分,從而實現 FPGA 作為硬件加速模塊的快速開發。

高層次綜合的發展前景

HLS 經過十數年的發展,雖然有諸如 AutoPilot、OpenCL SDK 等 FPGA HLS 商業化成功的案例出現,但距離其完全替代人工 RTL 建模還有很長的路要走。

比如,對于 FPGA 而言,內存瓶頸一直是制約系統性能的重要因素。除片上的各類 BRAM 之外,還有各類片外存儲單元,如 DDR、QDR,以及近年興起的 HBM 等等。因此,有效利用片上和片外各類存儲單元一直是 HLS 的研究熱點。

電子發燒友App

電子發燒友App

評論