電子發燒友網訊:目前有一種新型的轉換器接口正處于穩步上升的階段,根據其發展形勢,將來它或許會成為首選的轉換器協議,那就是JESD204。這種接口在幾年前就已經推出了,在經過幾次改版之后,它變成了一個很有吸引力的高效轉換接口。隨著轉換精度和速度的增強,對更高效率的接口的需求也日益增加。

JESD204不但帶了來高效率,并提供了CMOS和LVDS不能滿足的速度,大小和價格等優勢。采用JESD204的設計不但可以體會到其可以實現高速采樣率接口所帶來的好處。除此之外,還可以,得益于其針腳的減少,還可以降低其封裝大小,同時還可以使電路板的設計更加簡便,最重要還能降低整體成本。因為這個標準是很容易擴展的,因此它還能夠適應未來的設計需要。自從2006年發布以來,JESD204這個標準目前已經推出了兩個版本,現行的是B版本。

隨著這個標準逐漸被轉換器供應商和類似FPGA制造商等用戶采用,它變得更精確,同時也添加了更多的功能,這樣又提高了它的效率和操作的簡便性。這個標準適用于ADC和DAC,其最初的目的就是做一個基本的FPGA通用接口,或者也可以與ASIC一起用。

什么是JESD204?

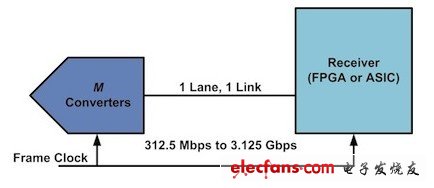

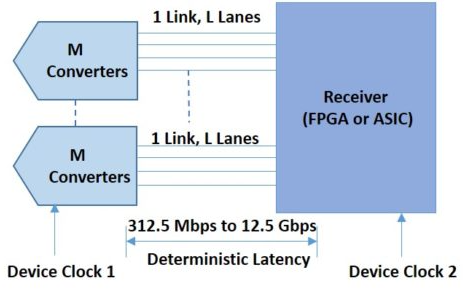

在2006年4月,JESD204的原始版本發布。這個標準被描述為一個轉換器和接收器(通常是FPGA或ASIC等設備)間的千兆位級的串行數據鏈接。在這個原始版本,串行數據連接定義為一個轉換器或者多轉換器和接收器之間的單獨一個串行通道。在圖一用圖形表示出來。展示的通道是M數量轉換器和利用CML驅動的差分互連接收器與接收器之間的實體界面。連接所展現的是轉換器和接收器之間已確定的串行數據連接。幀時鐘指定轉換器和接收器的路徑,同時給JESD204設備間的鏈接提供時鐘。

通道的數據速率定義在312.5Mbps到3.125Gbps之間,其負載阻抗定義在 。其差分電壓水平定義在0.72v到1.23V之間的普通模式電壓,并聲稱有著800mv的峰間電壓。

這個鏈接利用包含有嵌入式時鐘的8b/10b編碼器,從而就不需要額外布一條時鐘線,同時也免除了帶有高速率傳輸數據的額外時鐘信號復雜性調整的麻煩。隨著JESD204標準的逐步采用,改進這個標準去支持帶有多種轉換器的不同串行通道也就變得很有必要了,這樣也更能符合轉換器不斷增加的速度和分辨率的需要。

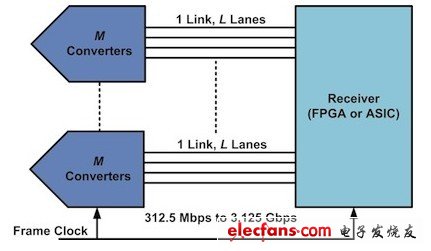

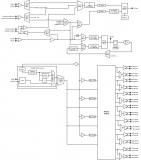

這些共識在2008年4月促進了JESD204第一個版本的推出,這也就是我們熟悉的JESD204A。這個標準的初版提供了對帶有多種轉換器的多樣串行通道的支持。通道的數據速率仍然保持在312.5Mbps到3.125Gbps之間不變,同時也保持一樣的幀時鐘和電氣接口規范。這個標準還增加了支持多樣化的串行通道的功能,這樣就能夠使帶有高采樣率和高分辨率的轉換器滿足3.125Gbps的數據速率要求。圖2展示了添加到JESD204A版本中以支持多種通道的的附加功能。

盡管原始版本的JESD204和改進版的JESD204A標準相對于傳統的接口有著更高的性能,但仍然缺少一個關鍵的要素。這個缺少的元素則是鏈接中的連續性數據的確定延遲。

?????? 為JESD204正名

當我們使用一個轉換器的時候,我們很有必要了解采樣信號及其數字表示之間的時序關系。這樣做就可以在接收到信號的時候在模擬區域對采樣信號進行適當的重建。會出現這種情況很明顯就是在進行模數轉換的時候,但在數模轉換的時候同樣適合。這個時序關系受到定義的ADC轉換器輸入信號瞬時采樣邊緣和轉換器輸出數字顯示之間多個時鐘周期的延遲影響。同樣地,在DAC,延遲定義為數字信號轉換成DAC直到模擬信號輸出改變的這段時間內的時鐘周期的數量。在JESD204和JESD204A的標準里,沒有給準確設置轉換器延遲和他的串行數字輸入和輸出定義的功能。

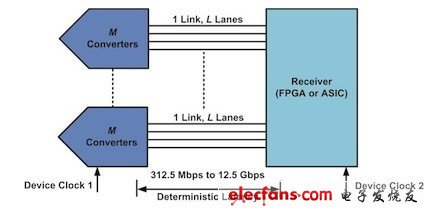

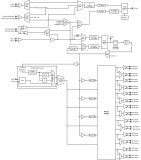

除此之外,轉換器將會繼續增加其速度和精度。這些要素就引出了這個標準第二個版本JESD204B的介紹。在2011年7月,第二個版本也就是現行本本的標準JESD204B推出,這個標準改進的一個管管元器件就是添加了規定去獲得確定延遲,除此之外,數據速率支持逼近12.5Gbps,這就將設備分解成不同的速度等級。這個版本標準需要從用幀時鐘作為時鐘源到用設備作為主時鐘源過渡。圖3表示出了添加到JESD204B版本標準中的附加功能。

在JESD204標準的前兩個版本里,沒有嚴格規定通過接口的確定延遲。JESD204B版本通過提供一個機制、從電壓升高周期到電壓升高周期和通過鏈接再同步化,這樣的話延遲就可以再重復和具有確定性。一個行之有效的方法就是通過初始化轉換器初始通道的轉換器排列順序,同時及時利用一個叫做SYNC的輸入信號對所有通道進行一個明確的定義。

另一個實施方法就是利用JESD204B最新定義的SYSREF信號。SYSREF信號相當于主時間基準,同時調整設備時鐘的內部分配器和在每一個發射器和接收器的多幀時鐘。這可以幫助通過系統確認確定延遲。JESD204B說明書介紹三個設備sub-classes:不支持確認延遲的Sub-class 0,通過SYSREF達到確認延遲的Sub-class 1和利用SYNC達到確認延遲的Sub-class 2。Sub-class 0可以簡單的看做JESD204A,Sub-class 1是定位應用在運行500MSPS以上的的轉換器,而Sub-class 2則只要為地獄500MSPS的轉換器服務的。

除了確認延遲,JESD204B版本將其通道數據速率增加到12.5Gbps,同時將設備分為不同的速度等級。對三個速度的設備來說,源和負載阻抗都是定義在100 ? ±20%。第一速度等級從JESD204和JESD204A版本的標準校準通道數據速率,也將電氣接口的通道數據速率定義在3.125Gbps。JESD204B的第二速度等級將電氣接口的通道數據速率定義為6.375Gbps。這個速度等級將最小差分電壓水平降到400mv的峰間值。而不是第一速度等級的500mv。 JESD204B的第三速度等級將其電氣接口通道數據速率定義為12.5Gbps。這個速度把電氣接口所需的最低差分電壓降到360mv峰間值。隨著速度等級的通道數據速率的上升,最低差分電壓則相應減小,之后降低驅動器的必要轉換速率會令物理實現變得更方便。

為了使JESD204B版本從幀時鐘到設備時鐘的過渡更具有靈活性。之前在JESD204和JESD204A版本中,JESD204系統的幀時鐘是絕對幀時間基準。一般來說,轉換器的幀時鐘和采樣時鐘是一樣的。當我們嘗試去給多樣化設備布置相同的信號,同時對不同路徑這樣就不能提供更多的靈活性,也有可能為嘗試給多設備配置相同信號的系統設計帶來不可預料的復雜性,也可以解析不同通路間的相交問題。在JESD204B,設備時鐘是JESD204系統的每個因素的定時基準。每一個轉換器和接收器都從時鐘發生器電路獲得相應的設備時鐘。這就為系統設計帶來更多的靈活性,但這要求指定給定設備的幀時鐘和設備時鐘之間關系。

為什么要關注JESD204

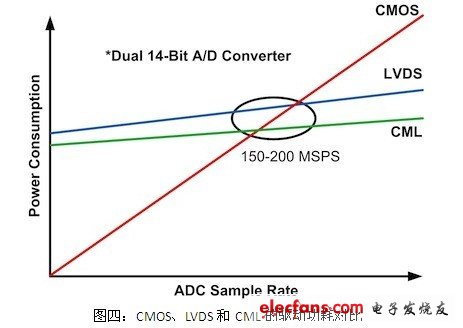

就如早幾年LVDS超越CMOS成為轉換器數字接口那樣,JESD204在以下的幾年也會走上這條道。當然,CMOS技術在這段時間內應該也是停步不前,因為它已經被LVDS全面壓制了。轉換器的速度和精確度及其低功耗彌補了COMS和LVDS所不能做到的。隨著CMOS輸出的數據速率的提升,順便電流也會同樣升高,這樣就會造成高功耗。然而LVDS的電流和功率損耗都相對平穩。圖四說明一個雙通道14位ADC的CMOS、LVDS、CML輸出的功率損耗。

?

總結

由于轉換的速度和分辨率的增加,更高效的數字接口的需求也有所增加。行業開始實現JESD204序列化的數據接口。在轉換器和FPGA(或ASIC)之間,接口規范持續發展提供了一個更好更快地傳輸數據。接口經歷了兩次修訂,改善了其性能,而且能滿足日益增長的需求,也帶來了更高的速度和更高的分辨率轉換。展望未來轉換器的數字接口,很明確,JESD204有望成為數字轉換器接口的行業標準。每個修訂已經回答了改善其實施的要求和允許標準的發展,以滿足轉換技術的變化所帶來的新要求。由于系統設計變得更加復雜和轉換器的性能的提高,JESD204標準必定要能夠適應發展的需要,以不斷滿足新的設計要求。

?

電子發燒友App

電子發燒友App

評論