信號發(fā)生器(Signal Generator)是一種產生特定類型信號的儀器,常用于電子設備的測試、測量和調試。差分信號(Differential Signal)是由一對反相且相等幅值的信號構成,常用

2024-02-23 16:35:53 381

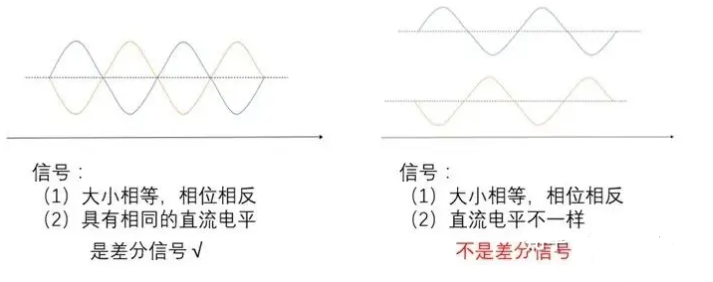

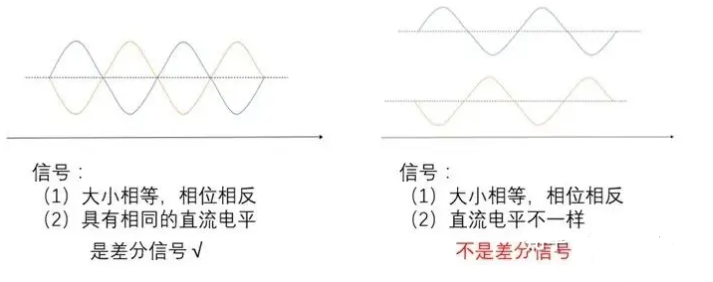

381 差分信號是一種在電子和通信系統中廣泛使用的信號傳輸方式,它通過比較兩個電信號之間的差異(電壓差)來傳遞信息。與單端信號不同,后者只參考一個單一的電位,差分信號依賴于一對導線上的電壓差。這兩個電信號

2024-02-16 11:38:00 366

366

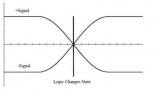

解讀差分信號、單端信號的優(yōu)缺點? 差分信號和單端信號是在信號傳輸中常用的兩種傳輸方式。它們各有優(yōu)缺點,在不同的應用場景中選擇合適的傳輸方式可以提高系統性能和可靠性。 差分信號是由兩個相互成對的信號

2024-01-17 15:37:25 207

207 另一個信號來得到的。常見的應用是在模擬和數字電路中用于傳輸和接收數據。差分信號具有很多優(yōu)勢,例如抗干擾能力強、噪聲抑制能力好等。 在差分信號中,通常會有兩個信號線,分別稱為正相和負相。正相信號是通過某種參考信號

2024-01-17 11:17:37 253

253 AD差分信號走線有哪些規(guī)則要遵循? AD差分信號走線是在電子系統設計中非常重要的一部分,它涉及信號傳輸的穩(wěn)定性、抗干擾性、匹配性等方面。下面我將詳細介紹AD差分信號走線的規(guī)則,以幫助您更好地理

2023-12-29 13:54:19 438

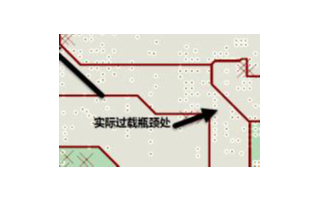

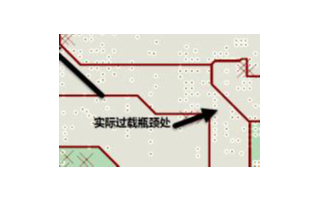

438 減少中間不一致部分的有效長度,如下圖所示。

IC管腳出線的線寬要小于或者等于焊盤寬度,出線寬度不能比焊盤寬度大,部分信號因載流等要求,線寬較寬的,布線可先保持與管腳寬度一致,布線引出焊盤后

2023-12-25 11:58:53

減少中間不一致部分的有效長度,如下圖所示。

IC管腳出線的線寬要小于或者等于焊盤寬度,出線寬度不能比焊盤寬度大,部分信號因載流等要求,線寬較寬的,布線可先保持與管腳寬度一致,布線引出焊盤后

2023-12-25 11:56:32

道路建設要求一去一回兩條線,PCB布線同樣道理,需要形成一個兩條線的回路,對于低頻電路角度上講,是回路,對于高速電磁場來講,是傳輸線,常見的 如差分信號線。比如USB、網線等。

2023-12-19 15:51:11 81

81 單端信號和差分信號是電信號的兩種常見傳輸方式,它們在信號傳輸中起著重要作用。本文將詳細討論單端信號和差分信號的區(qū)別和聯系,并以細致全面的方式描述這兩種信號傳輸方式。 一、單端信號 單端信號是指信號

2023-12-19 09:21:45 464

464 我的AD9446的工作在LVDS模式下,請問對于AD9446(100MHz),LVDS信號線的PCB走線的差分對間等長有沒有要求?(PS:16對差分線,都做等長好復雜)謝謝!

2023-12-18 06:26:51

我想用AD9235-65芯片,我的輸入信號頻率50K左右,輸入信號經過濾波后,離AD9235的距離很近,是不是就不需要單端轉差分輸入了?我的信號本來是單端的。或者更進一步,在什么情況下才需要單端轉差分信號?謝謝!

2023-12-14 07:57:13

抗干擾能力強,因為兩根差分走線之間的耦合很好,當外界存在噪聲干擾時,幾乎是同時被耦合到兩條線上,而接收端關心的只是兩信號的差值,所以外界的共模噪聲可以被完全抵消。

2023-12-13 15:52:23 53

53 (V4B)接模擬信號,平平 2 pin2(v4bgnd 的 v4bgnd)接模擬信號的參考GND;

差分信號時:平平1(V4B)接模擬信號的P端,平平 2 pin2(v4bgnd 的 v4bgnd)接模擬信號的N端?

謝謝!

2023-12-13 09:33:36

1.請問0-2V模擬信號經過AD8138轉為差分信號輸入AD6645,得到的差分信號是2.4±1V,是否超過了AD6645輸入范圍?

2.手冊上的這段話是說只能輸入在2.4±0.55V嗎?

2023-12-13 09:05:44

AD7606能支持差分信號輸入嗎?差分信號的P和N都在0-5V左右,能直接接入AD7606的那兩個輸入端嗎?

2023-12-13 07:01:24

差分傳輸是一種信號傳輸的技術,區(qū)別于傳統的一根信號線一根地線的做法,差分傳輸在這兩根線上都傳輸信號,這兩個信號的振幅相等,相位相反。在這兩根線上的傳輸的信號就是差分信號。

2023-12-06 16:10:28 1048

1048

一種常見的差分信號極性約定是,在接收器端,當正信號線上的電壓高于負信號線上的電壓時,被定義為正極性差分信號;當正信號線上的電壓低于負信號線上的電壓時,被定義為負極性差分信號。

2023-12-06 16:00:47 2390

2390

差分信號與單端信號走線的比較 在電子通信和數據傳輸領域,信號走線是非常關鍵的環(huán)節(jié)。差分信號與單端信號是兩種常用的信號傳輸方式,它們各自有著自己的特點和適用場景。本文將詳細比較差分信號和單端信號

2023-11-30 15:32:43 291

291 ±10V差分信號如何調理到差分ADC可以接受的±2.5V的范圍內?另外采用差分放大器驅動差分ADC時,發(fā)現在絕對最大額定值參數中,有個差分輸入電壓電壓,一般比較小,這個參數是不是說明只能輸入的差分信號就這么大?

2023-11-27 06:06:36

差分信號線中間可否加地線? 差分信號線是一種常見的電子設備連接方式,用于傳輸信號。它通常由兩條相互對稱的信號線組成,稱為正號線和負號線。差分信號線常用于音頻設備、通信設備以及高速數字信號傳輸

2023-11-24 14:44:33 554

554 為何差分對的布線要靠近且平行? 差分對是一種電路設計中常見的布線方式,它的作用是減小信號傳輸的干擾和噪音。差分信號傳輸是指將信號分解成兩個相等幅值、相位相反的信號,通過同時傳輸這兩個信號來進行

2023-11-24 14:38:13 334

334 PCB設計中常見的走線等長要求

2023-11-24 14:25:36 651

651

在使用AD8138單端轉差分信號時,使用的是經典電路,發(fā)現AD8138工作時,把輸入信號整體抬高了,請問這是什么原因?

2023-11-24 06:59:26

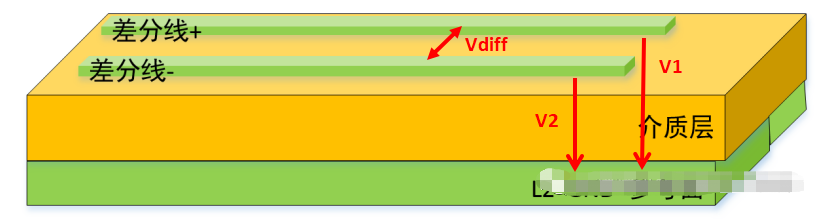

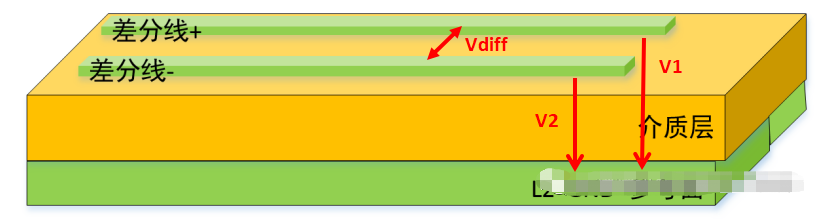

在PCB 電路設計中,一般差分走線之間的耦合較小,往往只占10~20%的耦合度,更多的還是對地的耦合,所以差分走線的主要回流路徑還是存在于地平面。當地平面發(fā)生不連續(xù)的時候,無參考平面的區(qū)域,差分走線之間的耦合才會提供主要的回流通路。

2023-11-23 15:36:38 127

127 測量儀表運放,需要有一個差分信號源,不用傳感器的話,如何用簡單的元器件模擬一個差分信號源呢?比如模擬一個稱重傳感器。

2023-11-23 07:15:36

一站式PCBA智造廠家今天為大家講講PCB設計關鍵信號如何去布線?PCB關鍵信號的布線要求。在PCB設計布線規(guī)則中,有一條“關鍵信號線優(yōu)先”的原則,即電源、摸擬信號、高速信號、時鐘信號、差分信號

2023-11-22 09:11:10 377

377

一個差分信號是用一個數值來表示兩個物理量之間的差異。從嚴格意義上來講,所有電壓信號都是差分的,因為一個電壓只能是相對于另一個電壓而言的。在 某些系統里,系統\'地\'被用作電壓基準點。當

2023-11-22 08:30:38

如題,AD8422僅支持最大+-40V的共模電壓,如何使用AD8422實現高達300V共模電壓的差分信號檢測?

2023-11-20 06:00:47

請教如何給高速運放差分信號提供偏置電壓?有相關偏置電壓的文章嗎

2023-11-17 08:13:25

當AD8237的差分信號是懸空狀態(tài)的時候,AD8237的輸出有50hz的干擾。另外當我的差分信號上有高頻干擾的時候,會影響到AD8237的電源輸出,我的AD8237的供電電源是3.3v,我們是用來

2023-11-17 06:36:08

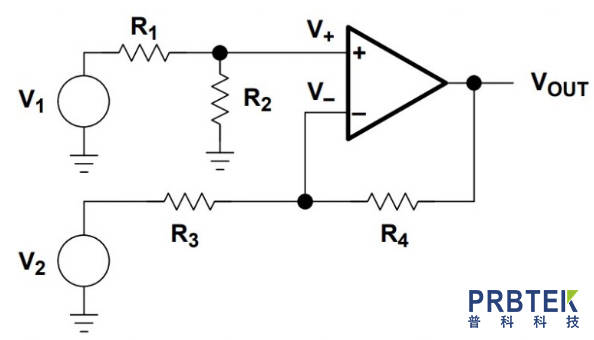

差分輸入需要與運放共地嗎,不共地的話,差分信號是怎么通過運放形成回路的,如本圖所示,求大神指教

2023-11-15 08:14:49

AD8014可以輸入兩路差分信號使其輸出一路單端信號嗎?

2023-11-15 06:33:08

一站式PCBA智造廠家今天為大家講講 pcb設計常見布線規(guī)則有哪些?PCB設計常見布線規(guī)則。

2023-11-14 09:17:55 606

606

差分信號進入ADC芯片,怎樣才能保證兩差分信號自動均衡呢? 差分信號進入ADC芯片時,為了保證兩差分信號自動均衡,可以采取以下措施: 1. 去除共模干擾:共模干擾是指差分信號的兩個輸入端引入的信號

2023-11-09 09:55:38 629

629 PCB布線對模擬信號傳輸的影響如何分析,如何區(qū)分信號傳輸過程中引入的噪聲是布線導致還是運放器件導致? PCB布線對模擬信號傳輸的影響是一項非常復雜的任務,需要考慮諸如電容、電感、阻抗、信號完整性

2023-10-31 14:34:18 439

439 一站式PCBA智造廠家今天為大家講講pcb設計布線解決信號串擾的方法有哪些?PCB設計布線解決信號串擾的方法。信號之間由于電磁場的相互而產生的不期望的噪聲電壓信號稱為信號串擾。串擾超出一定的值將可

2023-10-19 09:51:44 1234

1234 如何使用示波器測量差分信號 如何使用示波器測量信號的幅度 本文將介紹如何使用示波器進行差分信號測量以及信號幅度測量。 一、差分信號的測量 差分信號是指由兩個信號的差值直接產生的信號。在實際

2023-10-17 16:28:15 2573

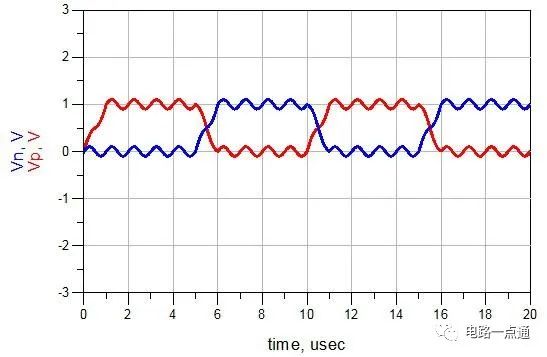

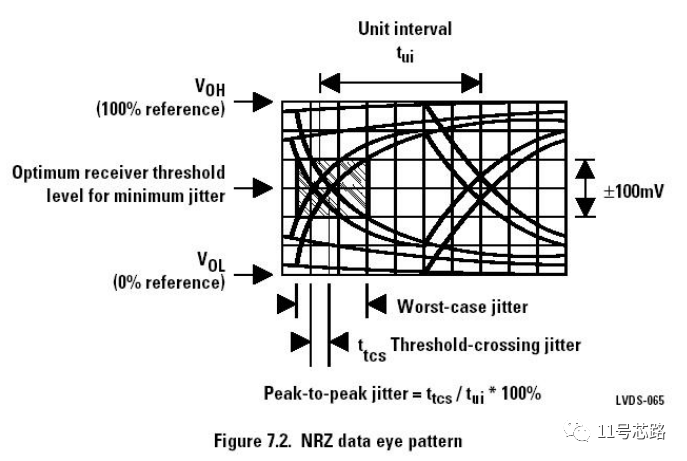

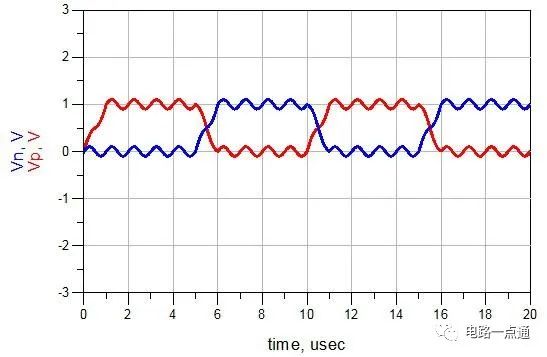

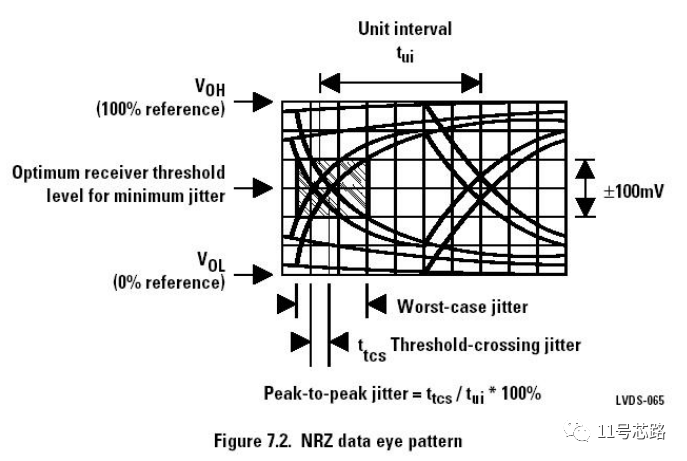

2573 LVDS是一種低擺幅的差分信號技術,它使得信號能在差分PCB線對或平衡電纜上以幾百Mbps的速率傳輸,其低壓幅和低電流驅動輸出實現了低噪聲和低功耗。

2023-10-02 16:44:00 586

586

差分信號和差模信號的區(qū)別聯系 在電路與傳輸中,信號可以用多種方式進行傳遞。其中包括差分信號和差模信號。差分信號和差模信號,可以用于很多的應用,例如在通信、功率放大器和模擬電路等領域中,起著非常重要

2023-09-19 17:33:46 1387

1387 信號發(fā)生器怎么產生差分信號? 信號發(fā)生器是電子儀器中非常重要的一個設備,它是用來產生高精度、高穩(wěn)定性電信號的設備。在電子行業(yè)中,它扮演著至關重要的角色,廣泛用于各種電子測試、電信實驗以及各種實驗室

2023-09-19 17:23:02 1619

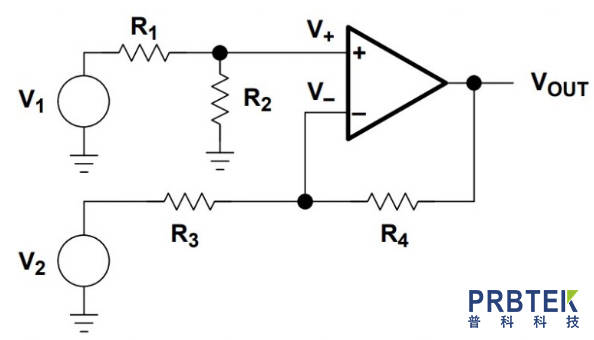

1619 差分信號如何轉換成單端信號? 差分信號和單端信號是電子信號傳輸中非常常見的兩種形式。差分信號由兩個互相反向的信號組成,單端信號只有一個信號。差分信號由于可以減少電磁干擾和提高傳輸距離,常被用于高速

2023-09-19 17:22:55 6006

6006 差分信號怎么用示波器測量? 差分信號是一種相對于地面電位或者參考電位進行測量的電信號。與普通電信號不同的是,差分信號由兩條互補線性電纜或者兩只信號線組成。這兩條線路中,一條線路攜帶著正極性信號,另一

2023-09-19 17:22:47 2087

2087 單端和差分信號的區(qū)別有哪些? 在電路系統中,信號傳輸是非常重要的。在一些特定的應用場合中,我們需要使用單端信號或差分信號來保證信號傳輸的穩(wěn)定性和可靠性。本篇文章將詳細介紹單端信號和差分信號的定義

2023-09-19 17:22:40 3227

3227 差分信號是5V的還是24V的?差分信號電壓是多少? 差分信號是指由兩個相同但電位不同的信號組成的信號,它們的電位差就是差分信號。在電子技術中,通常用差分信號來傳輸信號,差分信號可以使信號的抗干擾能力

2023-09-19 17:22:19 3072

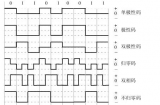

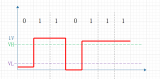

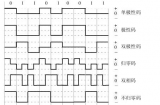

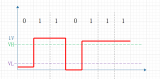

3072 差分信號怎么判斷0和1?? 差分信號是指信號的兩個不同狀態(tài)之間的差值,這種信號在很多通信系統中都被廣泛應用。傳輸數據時,差分信號被發(fā)送到接收端,接收端需要根據差分信號來判斷0和1。那么,差分信號

2023-09-19 17:22:16 1649

1649 差分線是 PCB 設計中非常重要的一部分信號線,因此我們對差分信號的處理要求相當嚴謹。 (差分信號原理圖示) 差分信號與單端信號的區(qū)別 單端信號指的是用一個線傳輸的信號,參考點為大地。換句話說

2023-09-12 10:15:15 1981

1981

▼關注公眾號: 工程師看海▼ ? 差分線是PCB設計中非常重要的一部分信號線,因此我們對差分信號的處理要求相當嚴謹。 (差分信號原理圖示) 差分信號 與 單端信號 的區(qū)別 單端信號 指的是

2023-09-05 08:46:52 1148

1148

在上期系列課程中,我們一起學習了綜合布線的測試標準,本期我們將和大家一起來探討如何打造一個高性能、高穩(wěn)定性的綜合布線系統?這是一個我們廣大用戶,尤其是數據中心用戶面臨的問題。我們將結合綜合布線的生命周期來進行探討與剖析,同時我們經常會遇到哪些誤區(qū)呢?

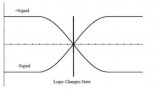

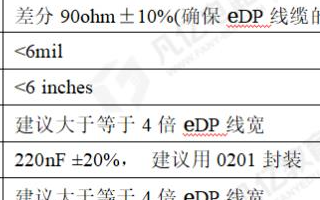

2023-09-01 15:15:58 279

279 接口的PCB設計布局布線注意事項: 1、遠離干擾源,防止其他信號干擾到傳輸速率以及信號的傳輸質量。 2、接口盡量靠在板邊放置,方便拔插,如PCB有結構上要求,要嚴格按照結構放置。 3、主芯片與顯示接口的位置不要放置的太遠,盡量縮短走線的距離,走線按照高速信號

2023-08-18 07:35:03 1133

1133

上期和大家聊的電源PCB設計的重要性,那本篇內容小編則給大家講講存儲器的PCB設計建議,同樣還是以大家最為熟悉的RK3588為例,詳細介紹一下DDR模塊電路的PCB設計要如何布局布線。

由于

2023-08-16 15:15:53

差分信號,英文名稱為differential Signal,是現在很常見的傳輸方式,在PCB板子上很容易見到。

2023-08-15 12:22:34 1759

1759 ,HDMI的傳輸速率也不斷的提升,HDMI2.0最大傳輸速率可達14.4Gbit/s,HDMI2.1最大傳輸數據速率可達42.6Gbit/s,因此對其PCB的布線也提出了更高的要求; 1、 HDMI接口

2023-08-12 07:35:03 938

938

單端信號是相對于差分信號而言的,單端輸入指信號有一個參考端和一個信號端構成,參考端一般為地端。

2023-08-07 09:39:05 496

496

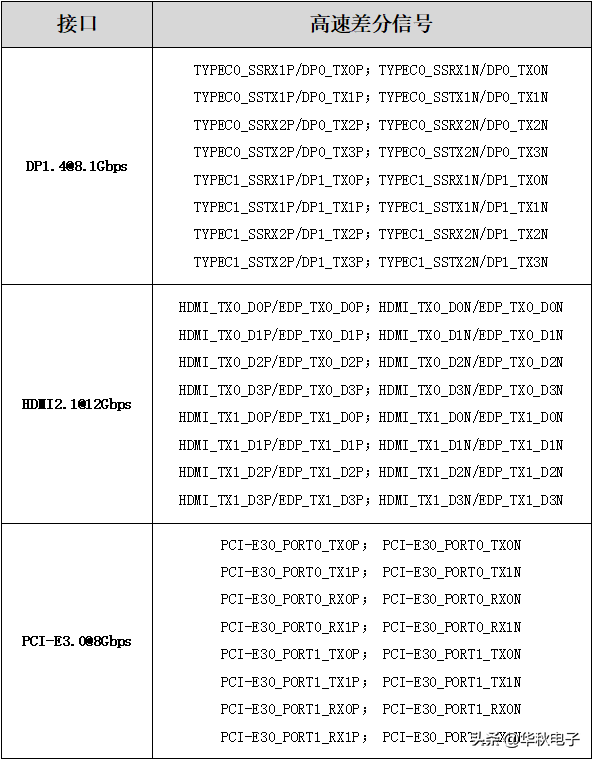

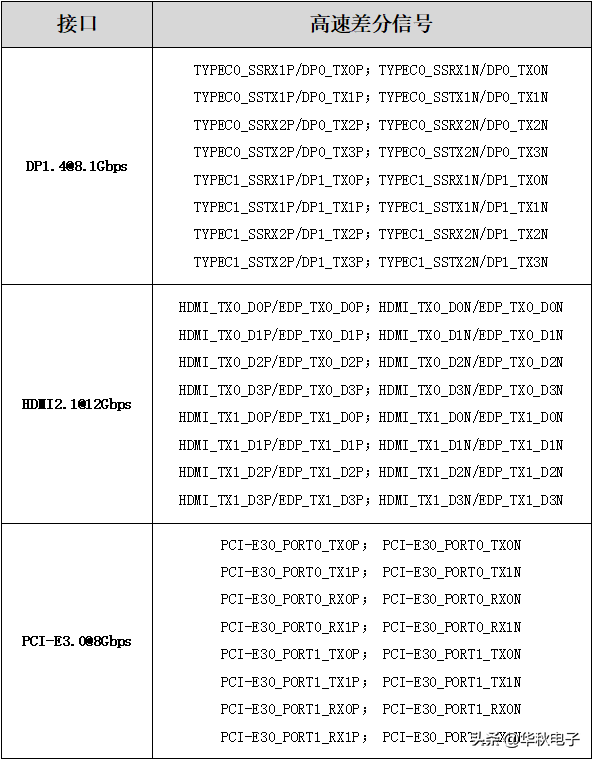

如下表所示,接口信號能工作在8Gbps及以上速率,由于速率很高,PCB布線設計要求會更嚴格,在前幾篇關于PCB布線內容的基礎上,還需要根據本篇內容的要求來進行PCB布線設計。

高速信號布線時盡量少

2023-08-03 18:18:07

如下表所示,接口信號能工作在8Gbps及以上速率,由于速率很高,PCB布線設計要求會更嚴格,在前幾篇關于PCB布線內容的基礎上,還需要根據本篇內容的要求來進行PCB布線設計。 高速信號布線時盡量

2023-08-03 18:15:02 486

486 如下表所示,接口信號能工作在8Gbps及以上速率,由于速率很高,PCB布線設計要求會更嚴格,在前幾篇關于PCB布線內容的基礎上,還需要根據本篇內容的要求來進行PCB布線設計。高速信號布線時盡量少打孔

2023-08-03 17:31:07 662

662

如下表所示,接口信號能工作在8Gbps及以上速率,由于速率很高,PCB布線設計要求會更嚴格,在前幾篇關于PCB布線內容的基礎上,還需要根據本篇內容的要求來進行PCB布線設計。 高速信號布線時盡量

2023-08-03 17:13:35 644

644

接口信號能工作在8Gbps及以上速率,由于速率很高,PCB布線設計要求會更嚴格,在前幾篇關于PCB布線內容的基礎上,還需要根據本篇內容的要求來進行PCB布線設計。 高速信號布線時盡量少打孔

2023-08-02 08:41:11 1432

1432

會更嚴格,在“PCBlayout 通用布線規(guī)范”的基礎上,還需要根據本章節(jié)的要求來進行PCB布線設計。 表1-1 RK3588 8Gbps及以上差分信號 高速信號布線時盡量少打孔換層,換層優(yōu)先選擇兩邊是GND的層面處理。盡量收發(fā)信號布線在不同層,如果空間有限,需收發(fā)信號走線同層時,應加大收發(fā)信號之間的

2023-08-02 07:35:01 422

422

如下表所示,接口信號能工作在8Gbps及以上速率,由于速率很高,PCB布線設計要求會更嚴格,在前幾篇關于PCB布線內容的基礎上,還需要根據本篇內容的要求來進行PCB布線設計。 高速信號布線時盡量

2023-08-01 18:10:06 1263

1263

如下表所示,接口信號能工作在8Gbps及以上速率,由于速率很高,PCB布線設計要求會更嚴格,在前幾篇關于PCB布線內容的基礎上,還需要根據本篇內容的要求來進行PCB布線設計。

高速信號布線時盡量少

2023-08-01 18:02:03

的板厚及層數要求,選擇合適阻抗模型,布線線寬按阻抗模型內計算的寬度進行設置,常見阻抗為單端50Ω,差分90Ω、100Ω等,注意天線50R信號是否應該考慮隔層參考。 圖2 常見的PCB層疊 3、如圖3所示,布線線寬需要滿足載流能力。一般情況下,可以基于

2023-07-31 07:45:01 5897

5897

一站式PCBA智造廠家今天為大家講講PCB設計差分布線有什么要求?PCB設計差分布線要求及操作技巧。高速串行總線的普及,使得PCB板上差分信號越來越多,那么,PCB設計如何進行差分布線呢?接下來

2023-07-07 09:25:21 3156

3156

一站式PCBA智造廠家今天為大家講講pcb布線后要怎么做檢查?pcb布線后的檢查技巧方法。布線作為PCB設計過程的重中之重,這將直接影響PCB板的性能好壞,設計過程也最繁瑣,要求更高。雖然現在很多

2023-06-14 09:50:42 1432

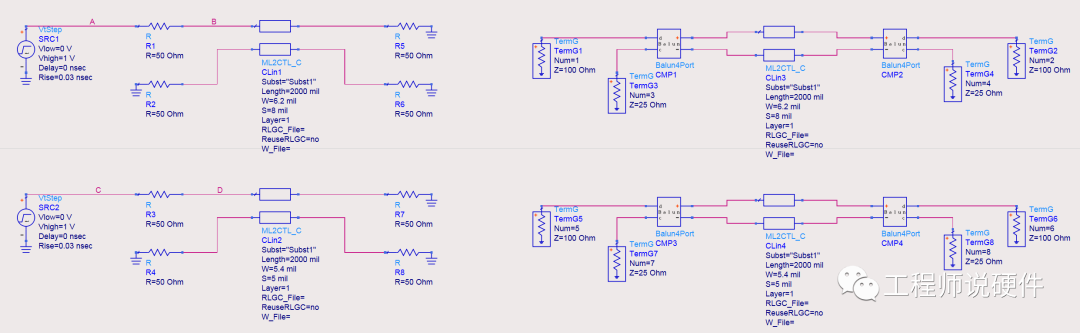

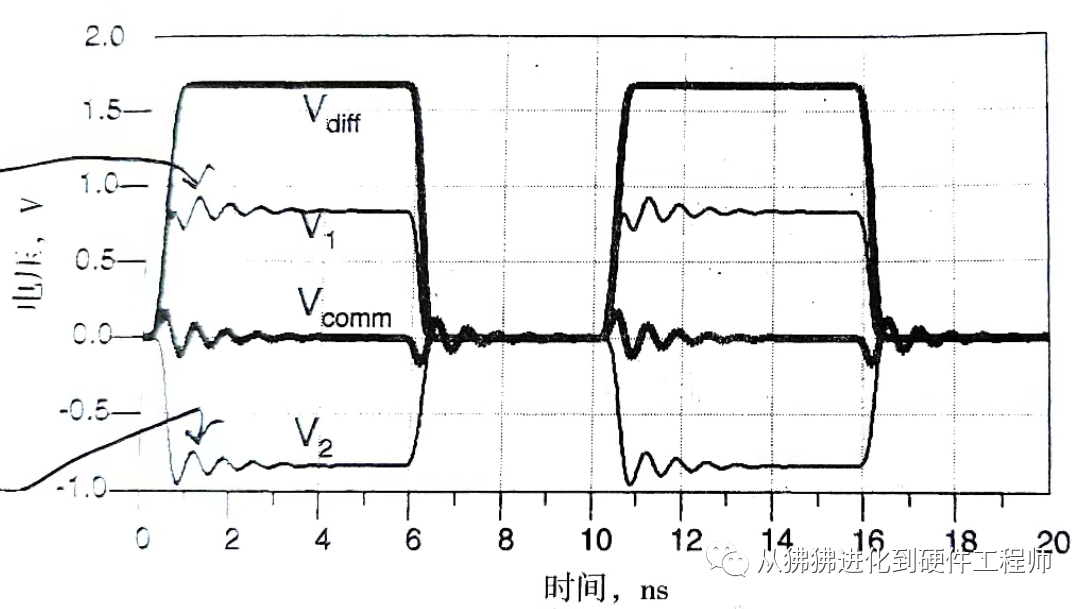

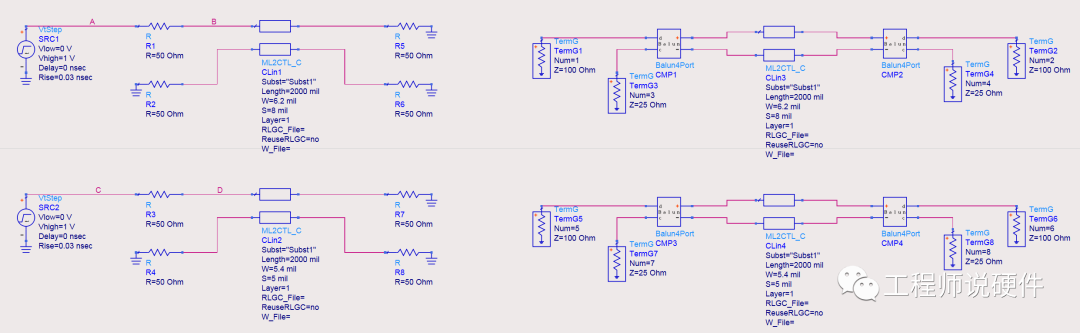

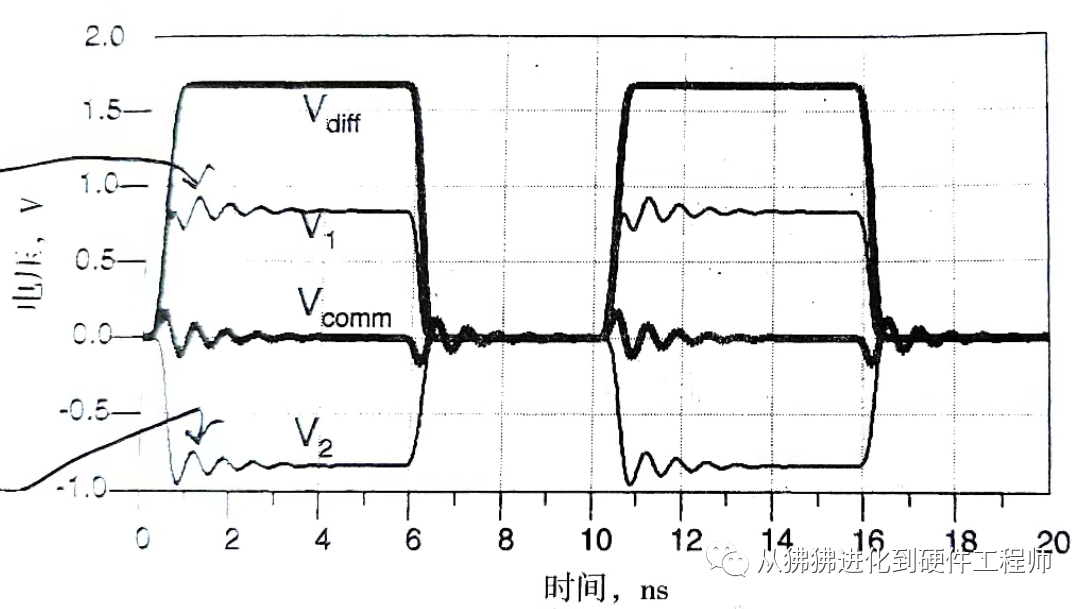

1432 本章我們開始《信號完整性基礎》 系列第五章節(jié)差分信號相關知識的講解。隨著信號速率的不斷提高,傳統并行接口的應用挑戰(zhàn)越來越大,基于差分信號的Serdes接口越來越普及,差分信號在其中的重要性不言而喻。

2023-06-09 10:37:38 2875

2875

差分信號是共模信號和差模信號的疊加,理想情況下共模信號是恒定的。

2023-06-09 09:08:13 1898

1898

USB協議定義由兩根差分信號線(D+、D-)傳輸數字信號,若要USB設備工作穩(wěn)定差分信號線就必須嚴格按照差分信號的規(guī)則來布局布線。根據筆者多年USB相關產品設計與調試經驗

2023-06-06 11:21:19 885

885

單端探頭是一種常見的測量工具,它可以用于測量電路中的電壓、電流、阻抗等參數。在差分信號測量中,單端探頭可以通過一些特殊的技術來實現對差分信號的測量。下面將介紹單端探頭如何測量差分型號。 1.

2023-06-02 10:06:16 1336

1336 在差分傳輸中,所有信息都由差分信號來傳送。保證差分信號質量很關鍵。

2023-05-09 16:45:44 1147

1147

can總線收發(fā)器如何識別傳輸線上的差分信號?這是怎樣一個過程?

2023-05-09 10:48:41

差分信號是指利用兩個輸出驅動pin去驅動兩根傳輸線。這兩根傳輸線,一根傳輸信號,另一根傳輸它的互補信號。接收端看到的信號是這兩條傳輸線上的信號壓差。差分對就是用來傳輸一對差分信號,并且存在耦合關系的傳輸線。例如LVDS就是一種常見的低壓差差分信號。

2023-05-06 16:02:47 6084

6084

如何使用僅配有單端探頭的示波器測量模擬差分信號?

2023-05-06 16:00:46

PCB布線技巧,筆記心得

一般規(guī)則

1.1 PCB板上預劃分數字、模擬、DAA信號布線區(qū)域。

1.2 數字、模擬元器件及相應走線盡量分開并放置於各自的布線區(qū)域內。

1.3

2023-05-05 10:21:48 0

0 運放是差分信號輸入單端信號輸出?運放有什么用呢?一般用在什么電路中

2023-04-25 16:18:33

對布局的要求:1A以上大電流元件、網絡、重要的時鐘信號、差分信號以及高速數字信號。

5、模擬小信號等易***擾信號。

布局基本原則

1、首先確定參考點,一般參考點都設置在左邊和底邊的邊框線

2023-04-24 15:56:45

差分放大器中單端信號轉差分信號時是否能將高頻的噪聲抑制?

2023-04-21 16:10:48

設計類型:主板 Pin數:2820 層數:6 難點: 1、4個HDMI3.0轉視頻接口之間的差分信號布線 2、外觀要求美規(guī)一致性 設計要點: 1、布局設計 在設計中如何放置特殊

2023-04-19 15:39:07

...................... 62.4 高速信號參考平面....................63 高速差分信號布線........................ 93.1 差分信號間距

2023-04-14 15:47:37

確保信號完整性的一個重要部分是信號走線的物理布線。PCB設計人員經常承受壓力,不僅要縮小設計,還要保持信號完整性。找到平衡點就是要知道問題可能發(fā)生的位置以及在系統出現故障之前可以推送信封的距離

2023-04-12 15:20:37

可使用兩個阻值各為50Ω的電阻,并在中間通過一個電容接地,以濾去共模噪聲。 通常對于差分信號的CLOCK等要求等長的匹配要求是+/-10mils之內。 誤區(qū)三 認為差分走線一定要靠的很近。 讓差

2023-04-12 15:15:48

注意事項 1 差分信號 高速串行總線的普及,使得單板上差分信號越來越多,對高速差分信號的處理主要有以下布線要求: 各類差分線的阻抗要求是不同的,根據設計要求,通過阻抗計算軟件計算出差分阻抗和對應

2023-04-12 15:08:27

高速電路器件管腳間的引線彎折越少越好。高速信號布線電路布線的引線最好采用全直線,需要轉折,可用45°折線或圓弧轉折,這種要求在低頻電路中僅僅用于提高鋼箔的固著強度,而在高速電路中,滿足這一要求卻可以減少高速信號對外的發(fā)射和相互間的耦合,減少信號的輻射和反射。

2023-04-12 11:33:46 961

961 PCB布線中串口通訊TXD和RXD需要遵循差分布線不?為什么?

2023-04-10 17:07:42

夾雜在差分信號之間的非查份(單獨一條)走線方式有什么要求嗎?這就是要畫的連接線PCB高速差分信號線四層怎么弄,還要求阻抗,就是一個連接線

2023-04-07 17:46:45

單端信號是相對于差分信號而言的,單端輸入指信號由一個參考端和一個信號端構成,參考端一般為地端。

2023-04-07 11:26:28 1214

1214 LVDS (Low Voltage Differential Signaling)是一種小振幅差分信號技術,它使用非常低的幅度信號 (250mV~450mv)通過一對平行的PCB走線或平衡電纜傳輸數據是一種專業(yè)的低電壓差分信號

2023-04-06 09:46:43 1285

1285 差分信號是一種常見的信號形式,它是指由兩個信號之間的差值構成的信號。在許多應用中,我們需要處理低壓差分信號,這就要求電路設計者使用帶有低偏置和高共模抑制的差分放大器。

2023-04-03 11:14:55 1285

1285

電子發(fā)燒友App

電子發(fā)燒友App

評論