網(wǎng)絡(luò)測(cè)試 NetWork 分析儀

2024-03-14 22:30:52

ADXRS910AWBRGZ-RL 特性高性能、層內(nèi)滾動(dòng)速率陀螺儀溫度補(bǔ)償,高精度偏移和靈敏度性能陀螺儀噪聲:2°/s rms(最大值)16位數(shù)據(jù)字串行端口接口(SPI)數(shù)字輸出靜態(tài)功耗:

2024-02-26 11:06:37

目前用到以下的電源芯片,請(qǐng)問以下的芯片thermalpad 是否需要加過孔到gnd層呢,還是直接在top層直接連接到地網(wǎng)絡(luò):

如果在thermalpad 上打過孔,應(yīng)該打幾個(gè)

LT3042

2024-01-05 08:25:19

薄TEM薄片+TEM觀察分析對(duì)于芯片膜層很薄的結(jié)構(gòu)層,一般是幾個(gè)納米的芯片膜厚,透射電鏡TEM分辨率比SEM高,透射電子顯微鏡的分辨率比光學(xué)顯微鏡高的很多,可以達(dá)到0.1~0.2nm,放大倍數(shù)為幾萬

2024-01-02 17:08:51

厚度建議全部采用1oZ,厚度為1.6mm。

板厚推薦疊層如下圖(上)所示(8層通孔1.6mm厚度推薦疊層),阻抗線寬線距如下圖(下)所示(8層通孔1.6mm厚度各阻抗線寬線距)。

10層1階HDI

2023-12-25 13:48:49

厚度建議全部采用1oZ,厚度為1.6mm。

板厚推薦疊層如下圖(上)所示(8層通孔1.6mm厚度推薦疊層),阻抗線寬線距如下圖(下)所示(8層通孔1.6mm厚度各阻抗線寬線距)。

10層1階HDI

2023-12-25 13:46:25

具體分析,我們來看看以下兩個(gè)只設(shè)計(jì)1個(gè)接地層的6層板分層方案,分析只有1個(gè)接地層時(shí),會(huì)帶來哪些不好的影響。

方案一: 該方案的問題是電源層和地層相隔較遠(yuǎn),中間隔了兩個(gè)信號(hào)層。所以其電源與地的耦合比較

2023-12-08 10:49:19

具體分析,我們來看看以下兩個(gè)只設(shè)計(jì)1個(gè)接地層的6層板分層方案,分析只有1個(gè)接地層時(shí),會(huì)帶來哪些不好的影響。

方案一: 該方案的問題是電源層和地層相隔較遠(yuǎn),中間隔了兩個(gè)信號(hào)層。所以其電源與地的耦合比較

2023-12-08 10:34:06

AD9164 JESD204B接口的傳輸層是如何對(duì)I/Q數(shù)據(jù)進(jìn)行映射的

2023-12-04 07:27:34

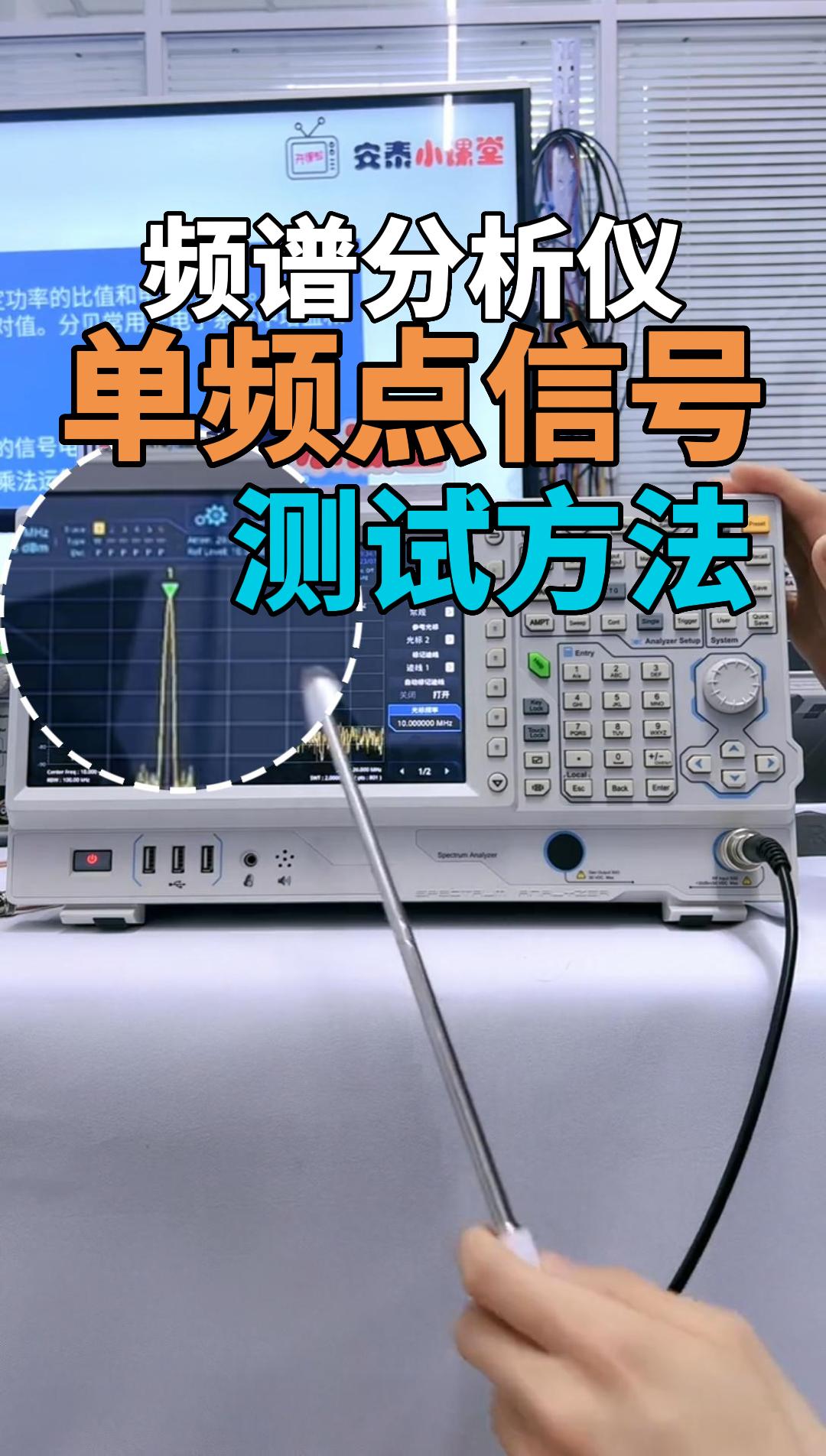

想畫出設(shè)計(jì)的電路THD值,隨頻率增益變化的曲線,怎么用分析儀測(cè)量。

2023-11-17 06:05:15

最近改了幾組電機(jī)線(3相線+接地線+屏蔽層):

1、地線電機(jī)與變頻器端都已經(jīng)接地;

2、屏蔽層入柜處接地;

運(yùn)行一天下來,發(fā)現(xiàn)以下幾個(gè)現(xiàn)象:

1、如果將屏蔽層在入柜處接地,電機(jī)在運(yùn)行過程中,間隔

2023-11-13 07:50:31

PCB設(shè)計(jì)時(shí),在那種情況下會(huì)使用跨層盲孔(Skip via)的設(shè)計(jì)?一般疊構(gòu)和孔徑怎么設(shè)計(jì)?

2023-11-09 16:21:10

請(qǐng)問帶顯示的和不帶顯示的USB邏輯分析儀的原理是什么 有沒有開源的資料分享?上位機(jī)分析軟件都是專用的嗎?

2023-11-09 06:48:01

在以TCP/IP5層模型中,應(yīng)用層是如何與傳輸層連接的 “封裝”又是指什么?顯示全部

2023-10-28 06:53:10

OPVXG便攜式網(wǎng)絡(luò)綜合協(xié)議分析儀 1-7層網(wǎng)絡(luò)全面透視,有線、無線集成式測(cè)試,網(wǎng)絡(luò)負(fù)載、壓力、吞吐量。。。全面的網(wǎng)絡(luò)故障診斷和數(shù)據(jù)包捕捉,現(xiàn)貨庫(kù)存。產(chǎn)品型號(hào)說明

2023-10-16 09:41:49

pcb裸銅的logo放在哪一層?

2023-10-16 07:29:19

紙張層間剝離強(qiáng)度試驗(yàn)儀層間結(jié)合強(qiáng)度是指紙或紙板抵抗層間分離的能力,是紙張內(nèi)部粘結(jié)能力的反映。強(qiáng)度較低會(huì)導(dǎo)致紙張和紙板,在使用粘性油墨印刷時(shí)出現(xiàn)拉毛問題,強(qiáng)度過高會(huì)給紙張的生產(chǎn)加工帶來難度,同時(shí)加大了

2023-10-12 16:40:13

邏輯分析儀測(cè)的波形是亂的

2023-09-27 07:07:13

復(fù)合膜層間剝離試驗(yàn)機(jī) 復(fù)合膜剝離力測(cè)試儀是一款專業(yè)用于測(cè)試復(fù)合膜、薄膜等相關(guān)材料剝離強(qiáng)度的儀器。該儀器采用先進(jìn)的電子測(cè)量技術(shù),能夠快速、準(zhǔn)確地測(cè)定復(fù)合膜或薄膜材料的剝離力。該設(shè)備主要由主機(jī)

2023-09-20 15:29:25

4層藍(lán)牙產(chǎn)品PCB設(shè)計(jì)素材

2023-09-20 07:43:16

我們的應(yīng)用層和內(nèi)核層是不能直接進(jìn)行數(shù)據(jù)傳輸?shù)摹N覀円脒M(jìn)行數(shù)據(jù)傳輸,要借助下面的這兩個(gè)函數(shù)。

static inline long copy_from_user(void *to, const

2023-08-29 09:54:29

如煙笑著說討厭。

趙理工,在七夕前一天投了一個(gè)板,一個(gè)8層,2.0mm的軟硬結(jié)合板。軟板2層,硬板是6層,內(nèi)層銅厚1OZ,線寬線距沒有走極限,且都滿足工藝能力,疊層如下:

從疊層中,我們可以看出

2023-08-22 16:48:12

的分析方法。利用干涉儀圖樣的分析,可以直接獲得相關(guān)參數(shù)(如膜層厚度、表面粗糙度、膜層折射率等),從而得到準(zhǔn)確的測(cè)量結(jié)果。

2、對(duì)于非同質(zhì)材料,由于其光學(xué)特性的差異性,分析方法相對(duì)更為復(fù)雜,通常需要借助

2023-08-21 13:46:12

在兩個(gè) tensorflow 模型上運(yùn)行模型優(yōu)化器,其中包含一個(gè)ctc_greedy_decoder和tf.keras.backend.ctc_decode的 CTC 層

這兩個(gè)錯(cuò)誤均未

2023-08-15 08:26:07

在 OpenVINO? 工具套件 2021.4 中使用 IENetwork.層 。

收到錯(cuò)誤:openvino.inference_engine.ie_api。IENetwork 對(duì)象沒有屬性“層”

2023-08-15 06:41:56

類型的不同,各參數(shù)的最佳工藝存在差異。 在恒壓模式下,隨電壓的升高,氧化膜生長(zhǎng)速率增大,膜層厚度、表面孔隙率及防腐性均增加,

2023-07-19 16:45:41

使用NUC970 官網(wǎng)自帶的mtd層nuc970_nand.c 驅(qū)動(dòng),硬件BCH ECC 已正確開啟,如何制造一個(gè)nandflash 層ECC錯(cuò)誤,并觸發(fā)數(shù)據(jù)糾錯(cuò),有什么辦法? 有沒有誰(shuí)做過類似測(cè)試的。

2023-06-27 15:09:52

“ 不同EDA對(duì)于PCB中物理層的定義基本相同,比如信號(hào)層、絲印、阻焊、助焊等。但對(duì)于工藝層(輔助層)的定義會(huì)略有不同,比如Altium Designer沒有專門的板框層及Courtyard層,通常

2023-06-21 12:13:20

?“ 使用Allegro的小伙伴應(yīng)該很清楚Courtyard層的用法,但使用Altium Designer的小伙伴可能對(duì)Courtyard層完全沒有概念。Courtyard層到底是什么?在KiCad

2023-06-13 13:01:24

)。

添加Logo或其他圖形(也可以在絲印層)。

在阻焊層上添加文本或圖形,可能不如絲印層引人注目。露銅的文字或圖形看起來是不是很酷,取決于銅的表面處理方式。與絲印層相比,阻焊層可以做到更高的分辨率

2023-06-12 11:03:13

我的客戶需要在 i.MX8mini ( iMX8MMINI ) 上有一個(gè)可用的 AVS SDK,我發(fā)現(xiàn)了以下可能適合的元層:

https://github.com/nxp-imx-support

2023-06-08 06:45:15

頻域上去分析。時(shí)域的話,雷豹已經(jīng)在信號(hào)眼圖上有對(duì)比過了,那么想繼續(xù)分析這個(gè)串?dāng)_的改善的話,就有在頻域上去做文章了。

Chris對(duì)雷豹調(diào)整疊層前后的走線結(jié)構(gòu)進(jìn)行建模,利用cadence的3D

2023-06-06 17:24:55

“ 經(jīng)常看到小伙伴們?cè)儐朘iCad中的Margin層有什么用,和板框層Edge.Cut有什么區(qū)別?雖然實(shí)際實(shí)際中可以完全忽略Margin層,但理解它并合理的加以使用,可以為設(shè)計(jì)帶來一定的便利

2023-06-06 09:46:43

。內(nèi)層的加工成本相同,但敷箔/核結(jié)構(gòu)明顯的增加外層的處理成本。

奇數(shù)層PCB需要在核結(jié)構(gòu)工藝的基礎(chǔ)上增加非標(biāo)準(zhǔn)的層疊核層粘合工藝。與核結(jié)構(gòu)相比,在核結(jié)構(gòu)外添加敷箔的工廠生產(chǎn)效率將下降。在層壓粘合以前

2023-06-05 14:37:25

為了比demo板有更好的成本優(yōu)勢(shì),在設(shè)計(jì)上使用了相鄰層走線的這個(gè)方法,也就是我們所說的GSSG的疊層結(jié)構(gòu),這樣的話的確在層數(shù)上可以省下幾層,但是就會(huì)帶來其他方面的一些壞處。雷豹一直都是在關(guān)注走線

2023-06-02 15:32:02

電解質(zhì)支撐,但是歐姆電阻很大,正常在1以內(nèi),我的歐姆電阻4-15甚至更多,開路電壓可以達(dá)到1V,集流層采用銀乙醇,想知道怎么改進(jìn)?謝謝,這個(gè)是燒后的SOFC

2023-05-20 16:46:05

的PCI Express Gen6,也開始采用了多通道技術(shù)。 安立的信號(hào)質(zhì)量分析儀-R MP1900A系列是一款具備8個(gè)模塊插槽的高性能BERT,通過PPG/ED、及抖動(dòng)/噪聲發(fā)生器等擴(kuò)展測(cè)量

2023-05-17 17:59:55

的PCI Express Gen6,也開始采用了多通道技術(shù)。 安立的信號(hào)質(zhì)量分析儀-R MP1900A系列是一款具備8個(gè)模塊插槽的高性能BERT,通過PPG/ED、及抖動(dòng)/噪聲發(fā)生器等擴(kuò)展測(cè)量

2023-05-17 17:57:44

的PCI Express Gen6,也開始采用了多通道技術(shù)。 安立的信號(hào)質(zhì)量分析儀-R MP1900A系列是一款具備8個(gè)模塊插槽的高性能BERT,通過PPG/ED、及抖動(dòng)/噪聲發(fā)生器等擴(kuò)展測(cè)量

2023-05-17 17:54:39

由于運(yùn)輸 SAM 要求高性能,客戶希望在做出決定之前看到一些預(yù)測(cè)試。我們與唯冠 DFAE 合作開發(fā) SW 小程序。SAM卡中的這個(gè)小程序可以按照客戶算法進(jìn)行辦理和充值交易。

交易時(shí)間是客戶可以接受的。所以客戶研發(fā)團(tuán)隊(duì)已經(jīng)完成了JCOP4.5 中的applet 移植。

2023-05-08 08:28:35

在多層電路板里是不是所有電源都必須放在內(nèi)電層呢?

2023-05-06 10:20:36

PCB四層板的電源和地的內(nèi)層到底怎么布線?

2023-05-06 10:19:18

PCB 四層板里面的電源層和地層是什么意思,或者多層板里面的電源層和地層是什么意思?

我只是把四層板里面的中間兩層當(dāng)做是裝換的或連接的,為什么教材里面說是電源層和地層呢?

2023-05-06 10:15:14

1.PCB中,兩個(gè)不同電壓的電源層可以共用一個(gè)地層嗎?

2.如果可以共用地層的話,對(duì)于兩個(gè)不同電壓的電源層是各自用一個(gè)地層好,還是共用一個(gè)地層好?

3. “兩個(gè)電源層:3.3V,2.1V; 兩個(gè)信號(hào)層 ;地層” 怎樣布局最好?

2023-05-06 10:12:52

我們正致力于為基于 IMX8MPlus 的定制板開發(fā) Windows IOT 支持。我們使用 DP83867 以太網(wǎng)物理層代替 IMX8MPlus 板中使用的 RTL8211F 以太網(wǎng)物理層。

我們

2023-05-06 07:34:35

我建板s32g274ardb2,它可以制作圖像。現(xiàn)在我想向項(xiàng)目添加新層,所以我設(shè)置了新的 layaer meta-mylayer,我創(chuàng)建了 .bb .c 和 makefile。

然后我將

2023-04-25 09:59:34

層將再次被“百分比覆蓋率”方法,假設(shè)的50%的銅覆蓋和1盎司/ ft2(35μm)厚度。第4層仍然和以前一樣不連接到任何一個(gè)器件。 因此,4層結(jié)構(gòu)總結(jié)在圖8中。層4仍然是一個(gè)覆蓋整個(gè)底面的固體平面

2023-04-21 15:04:26

4.3.6 實(shí)驗(yàn)設(shè)計(jì)6:一個(gè)4層的PCB板與熱散熱過孔 為了完整性,“4層+散熱過孔”結(jié)構(gòu)也被實(shí)驗(yàn)設(shè)計(jì)為1層銅的幾個(gè)尺寸,并再次疊層,如圖8所示。結(jié)果如圖13所示。 (1)單層板。 (2

2023-04-21 14:51:37

SDK 軟件組件和抽象層文檔

2023-04-21 07:18:06

走線組成,而不是大型連續(xù)面積。對(duì)這些層進(jìn)行詳細(xì)的實(shí)驗(yàn)設(shè)計(jì)顯然是不可行的,因此采用了“百分比覆蓋率”方法。采用這種方法,計(jì)算出結(jié)構(gòu)的平均電導(dǎo)率,以銅層厚度占總面積的百分比計(jì)算。這些實(shí)驗(yàn)設(shè)計(jì)的目的,我們將

2023-04-20 17:10:43

我遇到了一個(gè)與 meta-rust 層相關(guān)的 I.MX yocto 構(gòu)建錯(cuò)誤,這是我之前在 bitebake 構(gòu)建過程中沒有看到的。在它下面是錯(cuò)誤線, 錯(cuò)誤:任務(wù)(虛擬:本機(jī):/home/dand

2023-04-20 08:49:07

4層PCB是一種常見的多層PCB類型,具有多種用途。您是否有興趣了解更多關(guān)于它們的信息,特別是它們的堆棧設(shè)計(jì)和類型?它們的優(yōu)點(diǎn)是什么,與2層PCB相比如何?

2023-04-14 15:38:20

功率分析儀進(jìn)行諧波測(cè)試是采用FFT算法還是其他算法呢?

2023-04-13 11:09:35

PCB四層板中我將中間兩層設(shè)置成了信號(hào)層,能否給點(diǎn)實(shí)用的布線的經(jīng)驗(yàn)???當(dāng)布完線后該怎么進(jìn)行敷銅呢?需要在哪層進(jìn)行敷銅,最好是能說說為啥。如果將中間層設(shè)置成電源層和地層,那中間層還能走信號(hào)線嗎???需要注意些什么???在此謝過。。。。

2023-04-11 17:33:46

多層PCB如何定義疊層呢?

2023-04-11 14:53:59

請(qǐng)教一下大神PCB多層板為什么都是偶數(shù)層呢?

2023-04-11 14:52:31

將BLE抽象層添加到新項(xiàng)目的正確方法是什么,應(yīng)該從哪里下載抽象。

2023-04-11 07:06:33

PCB板阻抗設(shè)計(jì):阻抗線有無參考層阻抗如何變化?生產(chǎn)PCB時(shí)少轉(zhuǎn)彎的阻抗線的阻抗更容易控制穩(wěn)定性?

2023-04-10 17:03:31

矢量網(wǎng)絡(luò)分析儀串?dāng)_如何測(cè)試,設(shè)備如何設(shè)置

2023-04-09 17:13:25

看到有f.cuf.adhes f.paste f.silks f.mask dwgs.user cmts.user eco1.user margin 有這些預(yù)定義的層,分別代表什么意思呢?分別在什么時(shí)候用呢?

2023-04-02 17:58:34

FPC基本結(jié)構(gòu)材料介紹 從撓性印制線路板的基本結(jié)構(gòu)分析,構(gòu)成撓性印制線路板的材料有絕緣基材、膠粘劑、金屬導(dǎo)體層(銅箔)和覆蓋層 。 01.銅箔基板(Copper Film) 銅箔:基本分

2023-03-31 15:58:18

大家好,我正在研究 VAR-SOM IMX8,我正在構(gòu)建 Qt5 圖像,yocto 版本是dunfell-fslc-5.4-2.1.x-mx8-v1.5。當(dāng)我嘗試將 meta-webkit 層添加到

2023-03-30 07:45:15

我正在研究 MBDT 中 BMS 與新 S32K344 和 MC33775 與先前版本 BMS MC33771 和 MC33664 的集成。我發(fā)現(xiàn)最新的 MBDT 使用 MCAL 層通過

2023-03-30 07:05:40

PADS設(shè)計(jì)4板,第一層基板挖一個(gè)大矩形槽,露出第二層基板,再在第二層基板挖一個(gè)小矩形槽,嵌套的。請(qǐng)問怎么實(shí)現(xiàn)?

2023-03-24 11:16:33

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論