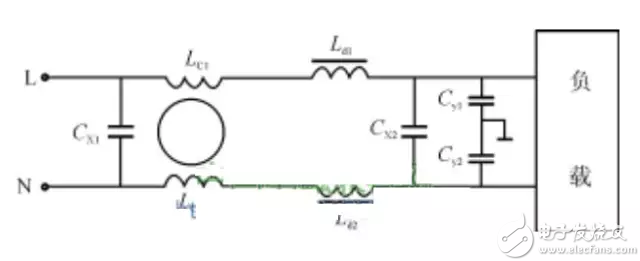

如圖所示,該電源電路中右下角的差模電感有無用處?

2024-03-19 11:23:33

我看到ADS1278上寫輸入?yún)⒖措妷?.5V,輸入共模電壓2.5V。一般輸入共模電壓不是一個(gè)范圍嗎,為什么是一個(gè)確定的數(shù)了?我現(xiàn)在混亂了。

2024-03-08 10:56:54

AD8260工作電壓+5V,High current driver作為差分輸入端,測試1-25MHz的100mV共模信號,實(shí)測High current driver輸出端共模<26dB

2024-03-06 06:58:28

多dB,光靠增加差模電容不太現(xiàn)實(shí),而且客戶的產(chǎn)品上已經(jīng)用了2級LC濾波;所以還是從整個(gè)濾波模塊上做處理,首先將板子上的磁環(huán)繞線共模電感換成扁平線共模電感BWCF1918SQL2P103L7A5(之前

2024-02-28 10:31:44

多dB,光靠增加差模電容不太現(xiàn)實(shí),而且客戶的產(chǎn)品上已經(jīng)用了2級LC濾波;所以還是從整個(gè)濾波模塊上做處理,首先將板子上的磁環(huán)繞線共模電感換成扁平線共模電感BWCF1918SQL2P103L7A5(之前

2024-02-28 10:26:20

書上說相位,大小相同電壓叫作共模電壓,但我不明白共模輸入為什么是uic=1/2(ui1+ui2),我認(rèn)為它應(yīng)該跟差模計(jì)算方式一樣才對,共模輸入電壓我覺得應(yīng)該是零才對啊,被共模電壓弄糊涂了啊~~~~~

2024-02-22 06:17:21

)+0.035V(AC),這樣算下來,差分電壓應(yīng)該是:Vid=V1-V2=0.433V(DC)+0.035V(AC),共模電壓是:Vcm=(V1+V2)/2=0.0025V(DC)+0.035V(AC

2024-01-09 07:12:33

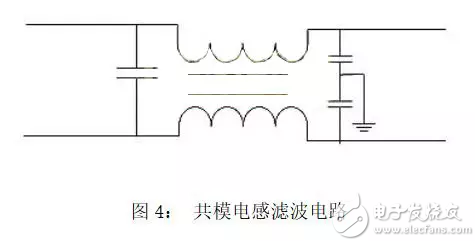

;所以常見的濾波、防護(hù)器件,多是共模形式,典型的代表就是共模電感;共模電感因其對共模干擾呈高阻特性、而對差模信號幾無損耗,所以在各種產(chǎn)品的電源輸入端、信號輸入/輸出端基本都有共模電感的身影。

圖1 CAN

2023-12-25 10:53:31

我加的共模電壓是1.5V。我空載的時(shí)候,該運(yùn)放輸出的共模電壓,四路都是還比較準(zhǔn)的1.5V,可是當(dāng)我加上IQ信號后,四路的直流輸出就不一樣了,I+和I-之間存在60mV左右的偏差,Q路也一樣,這是為什么呢?

求高手賜教!

2023-12-22 07:46:19

現(xiàn)采用AD9117應(yīng)用于正交調(diào)制電路,AD9117的輸出直接接芯片級濾波器后傳輸給正交調(diào)制芯片。設(shè)置差分輸出電流為20mA,輸出端負(fù)載電阻為50歐姆,則VDIFF=1V。如何設(shè)置才能使其差分輸出電壓的共模電壓在0~1.2V可調(diào)?我設(shè)計(jì)的電路如下:

2023-12-21 07:42:28

電路設(shè)計(jì)時(shí),將AD9266的VCM端與變壓器的中心抽頭相連了,但是誤把變壓器輸出的信號又進(jìn)行了隔直處理,即模擬輸入的共模電平為0V,輸入峰峰值可到1V左右,即VIN-最低可到-0.5V,請問是否會對

2023-12-21 06:53:34

AD7795輸入端能承受的最大共模電壓

2023-12-15 07:53:25

AD2S1210共模問題:

由于設(shè)計(jì)中電機(jī)上的旋變與控制電路上的RDC解碼芯片距離較遠(yuǎn),且旋變電纜和電機(jī)三相(300V)電纜距離較近,盡管使用了屏蔽線及端部接殼處理等處理,仍然產(chǎn)生了較大的共模干擾

2023-12-14 08:20:51

LTA180電流檢測放大器 是專為成本優(yōu)化型應(yīng)用設(shè)計(jì)。可在獨(dú)立于電源電壓的-0.2v至+26V范圍內(nèi)的共模電壓中檢測電流檢測電阻器上的壓降。LTA180以四個(gè)固定增益器件選項(xiàng)集成匹配的電阻器增益網(wǎng)絡(luò)

2023-12-13 16:50:27

在AD9117的測試中,發(fā)現(xiàn)I,Q分別的差分輸出端口,有很小的共模噪聲(噪聲頻率不確定),會造成波形會有非常輕微的抖動(dòng),請問是否有人有經(jīng)驗(yàn)解決。

2023-12-13 08:01:53

請問AD9124內(nèi)部的PGA架構(gòu),是否會自動(dòng)偏移共模電壓offset在AVDD-AVSS / 2?

還是設(shè)計(jì)上得放一顆OPA做Offset調(diào)整?

2023-12-05 08:22:16

LT1395運(yùn)放的共模輸入電壓范圍是多少?輸入共模電壓和電源電壓之間的關(guān)系是怎樣的。數(shù)據(jù)手冊只給出了5V和±5V條件下的輸入共模電壓范圍。假如采用Vs=+7V單端供電,輸入共模電壓范圍是多少?

同樣運(yùn)放輸出電壓和電源電壓的關(guān)系呢?

想用這款芯片做電壓跟隨,有沒有推薦的資料呢?謝謝!

2023-12-05 06:29:47

近期在使用AD9162時(shí),配置的模式不成功,測試時(shí)鐘CLK發(fā)現(xiàn),CLK±單端信號共模電壓接近0V,手冊上是0.6V,但測試9162-FMC-EZB參考板上的CLK也是共模電壓為0V,請問這個(gè)會有什么影響嗎?

我們現(xiàn)在測試配置JESD204B接口模式不正確,不確定是否CLK的影響?

2023-12-05 06:14:24

AD7760 datasheet里似乎沒有明確的說明內(nèi)置運(yùn)放輸入(VinA+/VinA-)的允許共模電壓范圍,圖52的例子里給的是共模電壓0V,輸入±2.5V的信號。

如果我希望在VinA+

2023-12-04 06:32:39

AD7403的規(guī)格書里只顯示了輸入電壓共模范圍的典型值是?200至+300 mV, 而沒有標(biāo)注最大值和最小值。如圖。 我這邊使用發(fā)現(xiàn),輸入共模現(xiàn)在到2V的時(shí)候,還可以正常運(yùn)行,所以有這個(gè)疑問。

2023-12-01 09:38:28

), the common-mode input includes ground. 這里共模竟然包含GND,也就是輸入AIN+可以是100mV以下的電壓,難道有矛盾

2023-11-30 06:13:43

,(IN+)接0-10v單端信號。增益為1,那么其輸出就是 Vout=(IN+)-( IN-)在這里共模信號是 (0~10)/2=(0~5)v嗎?差模信號是 (0~10v)嗎?

其輸出:Vout= 差模

2023-11-28 08:22:50

問題?

我的理解:

輸入的直流電壓信號應(yīng)該在0-90mv內(nèi)變化,輸出都應(yīng)該成線性變化。(理解有誤?)正確的電路應(yīng)該怎樣?

我用ADI公司的仿真軟件模擬過,如果共模電壓在2V左右或者接正負(fù)5V供電,(0-88mv)上述電路基本沒問題。如果不采用正負(fù)電壓供電,怎么樣在輸入端產(chǎn)生一個(gè)2V的共模電壓?

期盼解答!

2023-11-28 07:54:59

怎么計(jì)算共模電壓大小

2023-11-27 12:43:45

您好,附件是AD8138的外圍電路,是參考芯片手冊的電路設(shè)計(jì)的。主要是為了實(shí)現(xiàn)單端轉(zhuǎn)差分的功能。現(xiàn)在出現(xiàn)幾個(gè)問題:

1. 對于Vocm引腳,我從0V變化到750mV的過程中,輸出的共模電壓并不是

2023-11-27 08:24:44

1. 原理圖

圖1

2. 測試結(jié)果

圖2

3. 問題

1) 實(shí)驗(yàn)原理如圖1,根據(jù)計(jì)算,輸出信號V+和V-應(yīng)該是共模在Vocm=2V,但是測試結(jié)果如圖2,測試結(jié)果高于2V,這是問

2023-11-24 07:13:20

歐,此時(shí)當(dāng)輸入端差模電壓為3.4mV時(shí),輸出電壓為3.4V,放大倍數(shù)變?yōu)?000倍,與數(shù)據(jù)手冊描述也不符合。

請問該電路是否存在問題?為何放大倍數(shù)存在如此大的偏差?

在單電源供電時(shí),我考慮過是否是因?yàn)檩斎?b class="flag-6" style="color: red">共模電壓過低導(dǎo)致?請問在單電源供電情況下,輸入共模電壓是否在1/2VCC最合適?

2023-11-24 07:01:27

你好,ADI工程師,最近在做手持式的信號采集系統(tǒng),系統(tǒng)模擬前端采用+5V供電,用到AD8138與AD9233配合,現(xiàn)在問題是,AD8318在單電源+5V供電,輸出的共模偏置電壓是2.5V,而

2023-11-23 07:37:30

你好,我想咨詢下運(yùn)放OP282的共模輸入電容和差模輸入電容是多少?在45度的相位裕度時(shí)帶寬是多少?謝謝

2023-11-23 07:23:24

AD8331VGA的差分輸出采用什么耦合方式轉(zhuǎn)成單端信號,能大大提高抑制共模噪聲?我現(xiàn)在用的是ADT1-6T,原理圖如下,希望ADI工程師幫我分析下這個(gè)電路可行嗎?有什么需要改進(jìn)的地方?

2023-11-23 06:42:03

,頻率低于5MHz,請問:

1)在AD8139反相輸入端接地時(shí),可以將AD7626輸出的共模信號(VCM:2.048V)直接接到AD8139的Vocm端嗎?

2)AD8139的datasheet中第21

2023-11-22 07:55:43

大家好,為什么有些差分放大器可以工作在很高的共模電壓條件下,比如說AD629就可以工作在正負(fù)290V的共模電壓下,是因?yàn)樾酒瑑?nèi)部有特殊處理的電路嗎?

2023-11-20 07:10:42

在一些需要正弦激勵(lì)源的電橋激勵(lì)下,儀表放大器輸入RFI濾波器共模濾波和差模濾波截止頻率的選取?

參考儀表放大器指南:

按照描述,本截止頻率應(yīng)該針對直流電壓激勵(lì)電橋,所以截止頻率設(shè)置略高于

2023-11-20 07:01:41

脈沖信號的帶寬100m,干擾的頻譜應(yīng)該更好,然后找出它,通過設(shè)計(jì)RC的濾波進(jìn)行信號線濾波,c一般要到pf。這樣是否合理?我看一些資料介紹用磁珠濾波,這樣總感覺不可控,100m下的阻抗應(yīng)該需要比較小才不會損失信號本身能量,還有的方法是采用共模電感,這樣不會損失差模信號,也就是信號線。請大神們分析?

2023-11-20 06:30:02

如題,AD8422僅支持最大+-40V的共模電壓,如何使用AD8422實(shí)現(xiàn)高達(dá)300V共模電壓的差分信號檢測?

2023-11-20 06:00:47

請教一下ADA4932-2的問題,單端轉(zhuǎn)差分和差分轉(zhuǎn)單端的電路接法,實(shí)際調(diào)試過程中,按照附件的連接方法,差分轉(zhuǎn)單端使用±5V供電,但是上電之后,電源之間會相互影響,+5V會拉低到0V;還有單端轉(zhuǎn)差分的電路中+OUT1、-OUT1、和+OUT2、-OUT2輸出的共模電壓不一致,不知道什么原因?

2023-11-17 16:18:41

你好,我是從事IC測試的,目前在測試AD8138,其中差分輸入失調(diào)電壓這個(gè)參數(shù),產(chǎn)品手冊給的信息是它等于二分之一的差模輸出電壓,即,Vosdm=1/2 Vodm。而共模輸入失調(diào)電壓等于共模輸出電壓

2023-11-17 16:13:48

在設(shè)計(jì)電路時(shí),需要考慮儀表放大器對共模電壓的抑制能力,怎么才能計(jì)算出電路中會產(chǎn)生多大的共模電壓呢

2023-11-16 06:02:47

HMC960芯片應(yīng)用時(shí),采用阻容耦合,CMI(輸入共模電壓)、CMO(輸出共模電壓)必須連接嗎?

2023-11-15 07:05:33

儀表放大器AD620的共模輸入范圍超過電源電壓,會影響共模抑制比嗎?比如AD620采用正負(fù)5V電源供電,放大倍數(shù)為10倍,測試時(shí)共模輸入范圍為7.07V / 100Hz,會影響共模抑制比嗎?

2023-11-15 06:49:17

求微弱電流檢測用的共模電壓范圍最大值大于65V的運(yùn)算放大器或儀表放大器

2023-11-14 07:21:08

Can總線加共模電感是如何定義的?

2023-10-16 06:35:54

黑金Spartan6開發(fā)板的Verilog教程詳細(xì)說明

2023-10-11 18:02:45 1

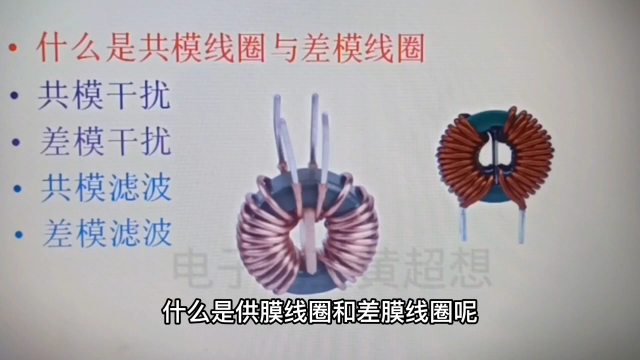

1 。共模電感是可以抑制共模干擾的器件,它對于共模信號呈現(xiàn)出大電感具有抑制作用,而對于差模信號呈現(xiàn)出很小的漏電感幾乎不起作用。是消滅電路中電磁兼容問題的一大利器;

二、共模電感在EMC電路里的原理流過共模

2023-10-11 10:58:22

本文檔的主要內(nèi)容詳細(xì)介紹的是電子管的代換資料詳細(xì)說明。

2023-09-26 07:24:46

的屬性。假設(shè)一個(gè)閉合回路的電流改變,由于感應(yīng)作用而產(chǎn)生電動(dòng)勢于另外一個(gè)閉合回路,這種電感稱為互感(mutual inductance)。

差模電感

差模電感(Differential Mode Choke

2023-09-21 06:23:30

車規(guī)級共模扼流圈

過濾汽車和工業(yè)應(yīng)用中的功率和信號噪聲

Abracon最新的共模扼流圈(CMC)可用于電源線和信號線的應(yīng)用。此外,信號線CMC可以支持can、can-FD和以太網(wǎng)數(shù)據(jù)傳輸中的噪聲

2023-09-12 14:48:02

電源用共模電感,感量越大越好?|深圳比創(chuàng)達(dá)EMC(下)電源用共模電感,感量越大越好?(下)相信不少人是有疑問的,今天深圳市比創(chuàng)達(dá)電子科技有限公司就跟大家解答一下!

一、共模電感特性測試分析通過對比

2023-08-23 10:58:20

共模電感后有效降低輻射更換共模電感后輻射有效降低,說明確實(shí)是最初電源口的共模濾波電路的插損不足;既然增大感量可有效降低輻射,鑒于余量仍不足3dB,就繼續(xù)增大共模電感感量,故選用了另一款30mH的共模

2023-08-22 10:42:02

使用STNRG011做的一款150W 電源,目前傳導(dǎo)測試低頻段有PFC工作頻率段的倍頻干擾導(dǎo)致裕量不夠,試了加大X電容,增大共模電感和增加差模電感始終無法降低倍頻干擾的值。有什么辦法降低干擾嗎?

2023-08-07 08:12:30

WCM-3216-222T:共模扼流程線圈(共模電感),常用在USB/LVDS/HDMI/以太網(wǎng)/485/CAN等差分信號濾波電路。SM712:SM712系列瞬態(tài)抑制二極管陣列專為保護(hù)具有非對稱工作

2023-07-05 11:25:42

對稱式電路

長尾式差分放大電路

二、對共模信號影響

當(dāng)電路輸入共模信號時(shí):

一方面:基極電流和集電極電流的變化相等,因此集電極電位的變化也相等,即uC1=uC2。使得輸出電壓uo

2023-05-15 16:34:10

將共模電感兩個(gè)引腳接反是不是就可以變成差模電感?因共模電感作用原理是共模干擾輸入兩個(gè)線圈時(shí)候產(chǎn)生的磁通方向相反而產(chǎn)生抑制,如果把第二個(gè)線圈接反,共模抑制作用就不存在了,是不是就變成差模電感了?

2023-05-09 11:12:28

共模電感兩邊繞線匝數(shù)一樣而電感量不一樣是什么原因?

2023-05-09 11:09:26

差動(dòng)放大電路由雙端輸入改為單端輸入,則差模電壓放大倍數(shù)保持不變。對嗎?

2023-04-26 11:46:25

差分放大電路輸入共模信號時(shí)

為什么說RE對每個(gè)晶體管的共模信號有2RE的負(fù)反饋效果

這里說的每個(gè)晶體管的共模信號是指什么信號 是指輸入信號 還是指ie1 ie2 uoc ?

另外為什么是負(fù)的反饋

2023-04-25 16:15:31

運(yùn)算放大器的差模輸入與共模輸入是什么意思?怎么區(qū)別呢?

2023-04-25 11:13:09

我們解決EMC問題首先要了解電路中的差模電流和共模電流問題! 分析如下: 在上圖中;最右邊的共模實(shí)際上就是我們等效的輻射的信號源的等效天線模型-也稱天線模! 共模(CM)電流和差模(DM

2023-04-19 16:27:17

差模共模定義: 1.從一個(gè)系統(tǒng)的一對輸入端看,若信號的極性以及電流方向相同,稱為共模信號。 2.從一個(gè)系統(tǒng)的一對輸入端看,若信號的極性以及電流方向相反,稱為差模信號。 如PCB中從芯片A

2023-04-18 14:47:15

抑制效果越明顯。而共模扼流圈的阻抗來自共模電感Lcm=jwLcm,從公式中不難看出,對于一定頻率的噪聲,抗干擾磁環(huán)的電感越大越好。但實(shí)際情況并非如此,因?yàn)閷?shí)際的抗干擾磁環(huán)上還有寄生電容,抗干擾磁環(huán)

2023-04-01 15:50:00

請問一下放大器的共模抑制和失調(diào)電壓有什么區(qū)別呢?

2023-03-31 15:29:51

差分放大電路的差模信號是兩個(gè)輸入端信號的和,共模信號是兩個(gè)輸入端信號的差。這是為什么,能舉個(gè)例子嗎?

2023-03-31 14:06:38

Part 01 這兩天有機(jī)會測SERDES,對AC COMMON MODE VOLTAGE有一點(diǎn)點(diǎn)認(rèn)識。 差模/共模電壓的概念可能從學(xué)生時(shí)代的來源要追溯到模擬電子線路了,公式很簡單: 我們

2023-03-24 15:28:59

電子發(fā)燒友App

電子發(fā)燒友App

評論