濾波器和接口設(shè)計(jì)程序 - ADI實(shí)驗(yàn)室電路:帶抗混疊濾波器的寬帶接收機(jī)

2012年12月14日 14:16 來源:ADI 作者:秩名 我要評(píng)論(0)

本部分說明放大器/ADC與濾波器的接口設(shè)計(jì)的一般方法。為了實(shí)現(xiàn)最佳性能(帶寬、SNR、SFDR等),必須考慮放大器和ADC對該一般電路的一些設(shè)計(jì)限制:

放大器應(yīng)具有數(shù)據(jù)手冊針對最佳性能而推薦的合適直流負(fù)載。

放大器與濾波器提供的負(fù)載之間必須使用大小合適的串聯(lián)電阻,這是為了防止通帶中出現(xiàn)不合需要的峰化現(xiàn)象。

ADC的輸入應(yīng)通過外部并聯(lián)電阻降低,并且應(yīng)使用合適的串聯(lián)電阻將ADC與濾波器隔離。此串聯(lián)電阻也能降低峰化。

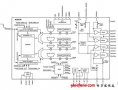

圖5所示的一般化電路適用于大多數(shù)高速差分放大器/ADC接口,將用作討論的基礎(chǔ)。這種設(shè)計(jì)方法利用多數(shù)高速ADC相對較高的輸入阻抗和驅(qū)動(dòng)源(放大器)相對較低的阻抗,通常可以最大程度地降低濾波器的插入損耗。

基本設(shè)計(jì)流程如下:

選擇ADC外部端接電阻RTADC,使得RTADC 和RADC 的并聯(lián)阻抗介于200 Ω和400 Ω之間。

根據(jù)經(jīng)驗(yàn)和/或ADC數(shù)據(jù)手冊建議選擇RKB ,通常在5 Ω與36 Ω之間。

通過下式計(jì)算濾波器負(fù)載阻抗:

ZAAFL = RTADC || (RADC + 2RKB)

選擇放大器外部串聯(lián)電阻RA。如果放大器差分輸出阻抗在100 Ω至200 Ω之間,則RA。應(yīng)小于10 Ω。如果放大器輸出阻抗為12 Ω或更小,則RA。應(yīng)介于5 Ω和36 Ω之間。

選擇RTAMP ,使得放大器的總負(fù)載ZAL對于所選的特定差分放大器是最佳的,計(jì)算公式如下:

ZAL = 2RA + (ZAAFL || 2RTAMP)

計(jì)算濾波器源阻抗:

ZAAFS = 2RTAMP || (ZO + 2RA)

利用濾波器設(shè)計(jì)程序或表格,以及源阻抗ZAAFS 、負(fù)載阻抗ZAAFL、濾波器類型、帶寬、階數(shù)等,設(shè)計(jì)濾波器。帶寬應(yīng)比采樣速率的一半高大約40%,以確保DC至fs/2頻率范圍內(nèi)的平坦度足夠好。

程序產(chǎn)生的最終并聯(lián)電容值應(yīng)減去ADC內(nèi)部電容CADC。程序會(huì)給出差分并聯(lián)電容的值CSHUNT2 ,最終共模并聯(lián)電容為CAAF2 = 2(CSHUNT2 – CADC)。

完成上述初步計(jì)算后,應(yīng)快速檢查一下電路的下列項(xiàng)目。

CAAF2的值應(yīng)比 CADC大好幾倍,至少應(yīng)為10 pF。這是為了最大程度地降低濾波器對 CADC變化的敏感度。

ZAAFL 與 ZAAFS 的比值應(yīng)等于或小于7左右,使得該濾波器在大多數(shù)濾波器表格和設(shè)計(jì)程序的限制以內(nèi)。

CAAF1的值至少應(yīng)為5 pF,以便最大程度地降低濾波器對寄生電容和組件變化的敏感度。

電感 LAAF的值應(yīng)合理,至少應(yīng)有數(shù)nH。

某些情況下,濾波器設(shè)計(jì)程序提供的解決方案可能不止一個(gè),特別是對于高階濾波器。此時(shí)應(yīng)選擇組件值組合最為合理的一種解決方案。此外,所選的配置應(yīng)結(jié)束于并聯(lián)電容,以便能與ADC輸入電容結(jié)合。

電路優(yōu)化技術(shù)和權(quán)衡

該接口電路的參數(shù)相互影響,因此,幾乎無法優(yōu)化電路的所有關(guān)鍵特性(帶寬、帶寬平坦度、SNR、SFDR、增益等)。然而,通過改變 RA 和 RKB,可以最大程度地降低通常出現(xiàn)在帶寬響應(yīng)中的峰化。

請注意圖6中通帶峰化如何隨著輸出串聯(lián)電阻RA的值提高而降低。但是,此電阻的值越高,信號(hào)衰減就越大,放大器必須驅(qū)動(dòng)更大的信號(hào)以填充ADC的滿量程輸入范圍。

RA 的值也會(huì)影響SNR性能。較大的值一方面會(huì)降低帶寬峰化,但另一方面,往往也會(huì)略微提高SNR,因?yàn)轵?qū)動(dòng)ADC滿量程所需的信號(hào)電平更高。

ADC輸入端串聯(lián)電阻RKB的選擇應(yīng)能最大程度地降低ADC內(nèi)部采樣電容的任何殘余電荷注入引起的失真。提高此電阻往往也會(huì)降低帶寬峰化。

但是,提高 RKB 會(huì)使信號(hào)衰減增大,放大器必須驅(qū)動(dòng)更大的信號(hào)以填充ADC的輸入范圍。優(yōu)化通帶平坦度的另一個(gè)辦法是少許改變?yōu)V波器并聯(lián)電容CAAF2。

ADC輸入端接電阻RTADC的選擇一般應(yīng)使ADC凈輸入阻抗介于200 Ω和400 Ω之間。降低其值會(huì)降低ADC輸入電容的影響,并且可能使濾波器設(shè)計(jì)更加穩(wěn)定,但不利的一面是會(huì)增大電路的插入損耗。提高其值也會(huì)降低峰化。

圖6. 通帶平坦度性能與放大器輸出串聯(lián)電阻RA的關(guān)系

要在這些因素之間取得平衡可能比較困難。本設(shè)計(jì)對每個(gè)參數(shù)一視同仁,因此,所選的值代表了所有設(shè)計(jì)特點(diǎn)的接口性能。某些設(shè)計(jì)中,根據(jù)系統(tǒng)要求,可能會(huì)選擇不同的值,以便優(yōu)化SFDR、SNR或輸入驅(qū)動(dòng)電平。

本設(shè)計(jì)的SFDR性能取決于兩個(gè)因素:圖1所示的放大器和ADC接口組件值,以及AD9467通過內(nèi)部寄存器的內(nèi)部前端緩沖偏置電流設(shè)置。表1和圖4所示的最終SFDR性能數(shù)值是在按照AD9467數(shù)據(jù)手冊所述優(yōu)化SFDR之后獲得的。

該特定設(shè)計(jì)中可以權(quán)衡的另一個(gè)因素是ADC滿量程設(shè)置。對于利用此設(shè)計(jì)(優(yōu)化SFDR)獲得的數(shù)據(jù),ADC滿量程差分輸入電壓設(shè)置為2 V p-p。滿量程輸入范圍變?yōu)?.5 V p-p可以使SNR性能提高大約1.5 dB,但會(huì)略微降低SFDR性能。輸入范圍由載入AD9467內(nèi)部寄存器的值設(shè)置,詳情參見數(shù)據(jù)手冊。

注意,本設(shè)計(jì)中的信號(hào)通過0.1 μF電容交流耦合,以便抑制放大器、其端接電阻與ADC輸入端之間的共模電壓。有關(guān)共模電壓的更多信息,請參閱AD9467數(shù)據(jù)手冊。

無源組件和PCB寄生效應(yīng)考慮

該電路或任何高速電路的性能都高度依賴于適當(dāng)?shù)腜CB布局,包括但不限于電源旁路、受控阻抗線路(如需要)、組件布局、信號(hào)布線以及電源層和接地層。有關(guān)高速ADC和放大器的PCB布局布線詳細(xì)信息,請參閱教程MT-031 和 MT-101。

濾波器中的無源組件應(yīng)使用低寄生效應(yīng)的表貼電容、電感和電阻。所選的電感為Coilcraft 0603CS系列。濾波器使用的表貼電容為5%、C0G、0402型,以確保穩(wěn)定性和精度。

常見變化

針對要求較窄帶寬、較低功耗的應(yīng)用,可以使用差分放大器 ADL5561 。ADL5561的帶寬為2.9 GHz,功耗僅40 mA。如果要求更低的功耗和帶寬,也可以使用ADA4950-1 ,其帶寬為1 GHz,功耗僅10 mA。如需更高的帶寬,可以使用6 GHz差分放大器ADL5565,它與上述器件引腳兼容。

電路評(píng)估與測試

本電路使用修改的AD9467-250EBZ 電路板和基于 HSC-ADC-EVALCZ FPGA的數(shù)據(jù)采集板。這兩片板具有對接高速連接器,可以快速完成設(shè)置并評(píng)估電路性能。修改的AD9467-250EBZ板包括本筆記所述的評(píng)估電路,HSC-ADC-EVALCZ數(shù)據(jù)采集板與Visual Analog評(píng)估軟件一起使用,此外還使用SPI控制軟件器來適當(dāng)控制ADC并采集數(shù)據(jù)。

本文導(dǎo)航

- 第 1 頁:ADI實(shí)驗(yàn)室電路:帶抗混疊濾波器的寬帶接收機(jī)

- 第 2 頁:濾波器和接口設(shè)計(jì)程序

上周熱點(diǎn)文章排行榜

上周資料下載排行榜

論壇熱帖

熱門博文

創(chuàng)新實(shí)用技術(shù)專題

瘋PK:2015,大陸IC設(shè)計(jì)趕超臺(tái)灣?

熱評(píng)

- LM3S9B96開發(fā)板手冊及原理圖

- NI推出Single-Board RIO嵌入式介面

- LED手電筒電路圖

- 3.15投訴:揭開天翼3G手機(jī)的“欺騙”

- STM32F103ZET6紅牛電路圖

- 高通發(fā)布全新設(shè)計(jì)DragonBoard板

- 3gqq.com 網(wǎng)頁登錄

- 新款 Apple TV 將在3月8日出貨

- 小米手機(jī)2工程機(jī)月底將上市

- protel99se正式漢化版免費(fèi)下載

博文

- 一個(gè)女生對電子信息工程專業(yè)的感悟

- 請問KEIL軟件使用及流水燈設(shè)計(jì),要掌握到什么程度和深度才是過關(guān)呢?請大俠們給以指點(diǎn)迷經(jīng)

- 《論模電與愛情》

- 電子工程師爆料——撕掉電子業(yè)現(xiàn)狀強(qiáng)大的遮羞布

- 我是小小技術(shù)員(一)

- 拯救大學(xué)生

- 《昨夜無眠,為了一個(gè)學(xué)生》

- 5V-USB充電器電路圖,有詳細(xì)制作步驟

- 大三了

- 華為思考人生

帖子

- 32X64雙色點(diǎn)陣時(shí)鐘+頻譜效果 分享制作 diy視界

- 51單片機(jī)新手(初學(xué)者)進(jìn)階必備 zhihuizhou

- 無線供電 新人求帶

- altium designe設(shè)計(jì)全部最全資料 申請加精。 hukaipanwenjing

- 年度總結(jié):2012,這一年,我收獲了什么? xiaoliu241

- 電子發(fā)燒友之電子工程師2012船票獨(dú)家發(fā)行 xiaoliu241

- 我們要如何正視考研問題 cherr番茄

- 十年技術(shù)不再迷茫 北京烤鴨

- 那些年你獲得了哪些證書? zhihuizhou

- 轉(zhuǎn)載:AVR——12864液晶動(dòng)畫顯示 ningkui

用戶評(píng)論

查看全部 條評(píng)論

查看全部 條評(píng)論>>