基于PLD的CCD Sensor驅(qū)動邏輯設(shè)計

0 引 言

視覺信息是客觀世界中非常豐富,非常重要的部分。隨著多媒體系統(tǒng)的發(fā)展,圖像傳感器應(yīng)用越

2010-01-14 11:33:27 1448

1448

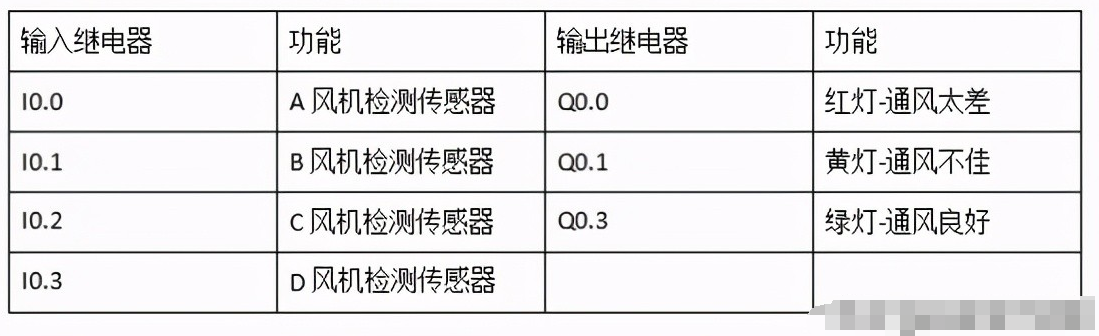

在了解了程序結(jié)構(gòu)和編程方法的基礎(chǔ)上,就要實際地編寫 PLC 程序了。PLC控制系統(tǒng)設(shè)計需要經(jīng)歷如下過程。

2015-09-17 10:13:16 7980

7980 PLC 程序設(shè)計常用的方法主要有經(jīng)驗設(shè)計法、繼電器控制電路轉(zhuǎn)換為梯形圖法、邏輯設(shè)計法、順序控制設(shè)計法等。

2023-11-01 15:49:37 1468

1468

2011 沙特big 5 五大行業(yè)展(北京邁斯百特)展會時間:2011年02月27日—03月02日 展會地點:沙特吉達(dá)國際會展中心 &

2010-07-05 17:09:25

步驟編程法有哪些功能?步驟編程法的程序有哪些?

2021-10-11 07:02:28

邏輯設(shè)計和校驗工具v3.3版本下載完整資料。大小:61.1M[hide]邏輯設(shè)計和校驗工具v3.3.rar[/hide]

2009-10-29 14:32:52

偏硬件:接口電路中的門組合電路;偏軟件:算法、接口控制器實現(xiàn)中的狀態(tài)機群或時序電路。隨著邏輯設(shè)計的深入,復(fù)雜功能設(shè)計一般基于同步時序電路方式。此時,邏輯設(shè)計基本上就是在設(shè)計狀態(tài)機群或計數(shù)器等時序電路

2021-11-10 06:39:25

ZYNQ將CPU和FPGA集成到了一起 開發(fā)人員需要具備技能: 1.ARM操作系統(tǒng)應(yīng)用程序 2.設(shè)備驅(qū)動程序 3.FPGA硬件邏輯設(shè)計 需要了解Linux操作系統(tǒng),系統(tǒng)架構(gòu),F(xiàn)PGA和ARM系統(tǒng)之間

2021-07-22 08:55:46

ARM Cortex-M33處理器的五大特色

2021-01-29 07:35:54

DSP的五大發(fā)展趨勢雙SHARC+內(nèi)核加Cortex-A5,提升工業(yè)和實時音頻處理性能單片處理器可應(yīng)對多種應(yīng)用需求開源操作系統(tǒng)是工業(yè)領(lǐng)域必然趨勢

2021-02-19 06:11:21

圖像采集系統(tǒng)的結(jié)構(gòu)及工作原理是什么FPGA邏輯設(shè)計中的常見問題有哪些

2021-04-29 06:18:07

請教各位,F(xiàn)PGA在邏輯設(shè)計中有哪些注意事項?

2021-05-07 07:21:53

以及高速數(shù)字電路的時序設(shè)計與優(yōu)化。相信通過三天的學(xué)習(xí),將會對學(xué)員在邏輯設(shè)計領(lǐng)域的工作和學(xué)習(xí)大有裨益。課程時間的安排上授課占60%,實驗占40%。五、培訓(xùn)對象課程適合于使用FPGA器件進(jìn)行科研、教學(xué)和產(chǎn)品

2009-07-24 13:13:48

時,我沒有在總線上看到任何 FlexSPI 事務(wù)。閃存配置塊與 1170 EVK 相同。為了簡單起見,我使用的是在 1170 EVK 上正確運行的 hello world 應(yīng)用程序,而不是我們

2023-04-10 07:15:40

`MCS-51單片機與FPGA接口的邏輯設(shè)計.........`

2013-06-08 11:25:29

MPEG-2編碼復(fù)用器中的FPGA邏輯設(shè)計,看完你就懂了

2021-04-29 06:13:34

NI DMM提供的五大工具分別是哪些?如何高效利用這些工具?

2021-05-11 07:13:30

分別轉(zhuǎn)為PROTEL格式文件,在PROTEL中調(diào)入兩層,如果兩層的PAD和VIA的位置基本重合,表明前幾個步驟做的很好,如果有偏差,則重復(fù)第三步,直到吻合為止,將TOP層的BMP轉(zhuǎn)化為TOP.PCB

2018-09-21 10:26:19

Sequential Logic Design principles 時序邏輯設(shè)計原則[hide][/hide]

2009-09-26 13:00:22

靜態(tài)時序分析與邏輯設(shè)計

2015-05-27 12:28:46

交通燈控制邏輯設(shè)計n 1、紅、綠、黃發(fā)光二極管作信號燈,用傳感器或邏輯開關(guān)作檢測車輛是否到來的信號,實驗電路用邏輯開關(guān)代替。n 2、主干道處于常允許通行的狀態(tài),支干道有車來時才允許通行。主干道亮綠

2017-09-15 10:25:06

華為 大規(guī)模邏輯設(shè)計指導(dǎo)書 方法 論

2019-11-22 22:52:12

本帖最后由 eyesee 于 2017-3-2 09:29 編輯

華為_大規(guī)模邏輯設(shè)計指導(dǎo)書

2017-03-01 11:56:34

華為_大規(guī)模邏輯設(shè)計指導(dǎo)書

2012-08-18 08:11:53

華為大規(guī)模邏輯設(shè)計指導(dǎo)書

2015-04-20 13:41:35

華為大規(guī)模邏輯設(shè)計指導(dǎo)書。非常詳細(xì)地介紹了邏輯設(shè)計的規(guī)范要求及方法。

2020-01-27 17:58:38

華為靜態(tài)時序分析與邏輯設(shè)計

2014-05-20 22:55:09

單片機應(yīng)用程序框架時間片輪詢法的學(xué)習(xí)。根據(jù)所見的,學(xué)的,看的。大致分為三類程序結(jié)構(gòu)。1. 簡單的前后臺順序執(zhí)行程序。2. 時間片輪詢法。3. 操作系統(tǒng)。簡單的順序執(zhí)行的程序,寫起來往往很混亂。越復(fù)雜

2021-07-20 08:33:50

本文使用符合PCI電氣特性的FPGA芯片進(jìn)行簡化的PCI接口邏輯設(shè)計,實現(xiàn)了33MHz、32位數(shù)據(jù)寬度的PCI從設(shè)備模塊的接口功能,節(jié)約了系統(tǒng)的邏輯資源,且可以將其它用戶邏輯集成在同一塊芯片,降低了成本,增加了設(shè)計的靈活性。

2021-05-08 08:11:59

前言FPGA 可以實現(xiàn)高速硬件電路,如各種時鐘,PWM,高速接口,DSP計算等硬件功能。這是Cortex-M 處理器軟件無法比擬的。要實現(xiàn)FPGA 的邏輯設(shè)計,對于嵌入式系統(tǒng)工程師又是比較復(fù)雜和具有

2021-12-21 06:13:49

小編科普工業(yè)無線技術(shù)的五大考慮因素

2021-05-26 07:08:12

本帖最后由 daworencai 于 2016-1-21 14:46 編輯

崗位職責(zé):1.負(fù)責(zé)部門存儲系列產(chǎn)品的邏輯設(shè)計開發(fā)工作;2.負(fù)責(zé)存儲系列產(chǎn)品的BCH算法優(yōu)化、高速存儲技術(shù)實現(xiàn)等;負(fù)責(zé)

2016-01-21 14:42:39

行業(yè)的進(jìn)步離不開技術(shù)的創(chuàng)新,就在感知規(guī)避、GPS跟隨、室內(nèi)視覺定位等技術(shù)的熱度還未消退之時,又一批新銳技術(shù)已經(jīng)登上歷史的舞臺。下面宇辰網(wǎng)獨家整理了無人機領(lǐng)域的五大新銳技術(shù),看看你知道多少?

2020-08-21 06:59:20

什么是支路電流法?支路電流法的解題步驟有哪些?

2021-09-28 09:35:29

一個電路板焊接完后,在檢查電路板是否可以正常工作時,通常不直接給電路板供電,而是要按下面的步驟進(jìn)行,確保每一步都沒有問題后再上電也不遲。1、連線是否正確。檢查原理圖很關(guān)鍵,第一個檢查的重點是芯片

2019-10-20 08:00:00

要使用哪種方法去驗證 FPGA 的邏輯設(shè)計?FPGA的優(yōu)缺點是什么?

2021-04-08 06:57:32

請問直流伺服電機有哪五大類別?

2021-09-26 06:25:16

降低測量噪聲的五大技巧…………

2012-07-12 15:06:00

什么是陶瓷傳感器?陶瓷傳感器的五大應(yīng)用分別是什么?

2021-05-12 07:08:09

靜態(tài)時序分析與邏輯設(shè)計

2017-12-08 14:49:57

中規(guī)模集成時序邏輯設(shè)計:計數(shù)器:在數(shù)字邏輯系統(tǒng)中,使用最多的時序電路要算計數(shù)器了。它是一種對輸入脈沖信號進(jìn)行計數(shù)的時序邏輯部件。9.1.1 計數(shù)器的分類1.按數(shù)制

2009-09-01 09:09:09 13

13 時序邏輯設(shè)計原則 (Sequential Logic Design principles):A sequential logic circuit is one whose outputs

2009-09-26 12:54:35 33

33 時序邏輯設(shè)計實踐 (Sequential Logic Design Practices)The purpose of this chapter is to familiarize you

2009-09-26 12:57:53 13

13 基于PLD芯片的時序邏輯設(shè)計與實現(xiàn):原理圖輸入設(shè)計直觀、便捷、操作靈活;1-1、原理圖設(shè)計方法簡介QuartusII已包含了數(shù)字電路的基本邏輯元件庫(各類邏輯門及觸發(fā)器),宏

2009-10-29 22:03:10 0

0 本文介紹了一種基于FPGA 的用自定義串口命令的方式實現(xiàn)MDIO 接口邏輯設(shè)計的方法,并對系統(tǒng)結(jié)構(gòu)進(jìn)行了模塊化分解以適應(yīng)自頂向下的設(shè)計方法。所有功能的實現(xiàn)全部采用VHDL 進(jìn)行描

2009-12-26 16:48:44 103

103 摘要:“邏輯設(shè)計”課是近二、三十年隨著信息類一批新專業(yè)(自動化、計算機、通信和信息等)陸續(xù)建立而開設(shè)的一門重要的學(xué)科基礎(chǔ)課。只要掌握“邏輯設(shè)計”課的特點和主要問題

2010-05-25 10:10:29 0

0 ASIC與大型邏輯設(shè)計實習(xí)課

AgendaCell Base IC DesignModelSimLibraryProjectVHDL Compiler & SimulationSimulation WindowsTutorialLab

2010-06-19 09:45:20 0

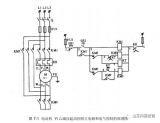

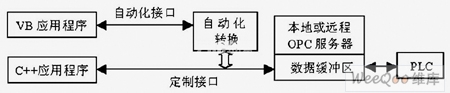

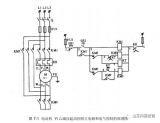

0 利用OPC實現(xiàn)VC應(yīng)用程序與PLC的數(shù)據(jù)交換

VC(Visual C++)是功能強大的一種Windows應(yīng)用程序可視化軟件開發(fā)工具。VC支持面向?qū)ο蟮脑O(shè)計方法,并可以使用功能強

2010-04-17 18:04:10 4716

4716

組合邏輯設(shè)計實例_國外:

2011-12-16 15:08:59 24

24 《數(shù)字電路與邏輯設(shè)計》答案

2012-06-25 08:19:15 23

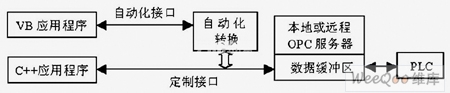

23 PLC系統(tǒng)控制電機,其中含有詳細(xì)的轉(zhuǎn)換程序和操作步驟

2015-12-31 11:19:06 2

2 多分辨率圖像實時采集系統(tǒng)的FPGA邏輯設(shè)計

2016-08-29 15:02:03 6

6 華為靜態(tài)時序分析與邏輯設(shè)計,基礎(chǔ)的資料,快來下載吧

2016-09-01 15:44:10 56

56 在線座談回放資料:5月27日 Altera 如何令邏輯設(shè)計在新一代CPLD中盡顯優(yōu)勢 (問答記錄)

2017-01-08 14:27:49 0

0 學(xué)習(xí)單片機不可欠缺的八大步驟

2017-01-12 21:52:46 15

15 使用標(biāo)準(zhǔn)集成電路的邏輯設(shè)計課題

2017-09-19 11:41:06 19

19 繼電器控制系統(tǒng),因此用邏輯設(shè)計方法同樣也適用于PLC應(yīng)用程序的設(shè)計。當(dāng)一個邏輯函數(shù)用邏輯變量的基本運算式表達(dá)出來后,實現(xiàn)這個邏輯函數(shù)的線路就確定了。當(dāng)這種方法使用熟練后,甚至梯形程序也可以省略,可以直接寫出于邏輯函

2017-10-24 10:44:30 4

4 芯片制造主要有五大步驟:硅片制備、芯片制造、芯片測試與挑選、裝配與封裝、終測。集成電路將多個元件結(jié)合在了一塊芯片上,提高了芯片性能、降低了成本。隨著硅材料的引入,芯片工藝逐步演化為器件在硅片上層以及電路層的襯底上淀積。

2018-01-30 11:03:39 79020

79020

本文開始介紹了三菱plc的相關(guān)概念,其次介紹了三菱PLC程序讀取的詳細(xì)步驟,最后介紹了三菱plc讀取時鐘程序。

2018-04-10 14:47:52 29408

29408

本文主要介紹了MES系統(tǒng)實行精細(xì)化管理的六大步驟。

2018-06-04 08:00:00 4

4 本文檔的主要內(nèi)容是臺達(dá)DVP系列PLC解密軟件應(yīng)用程序免費下載。

2018-07-04 08:00:00 163

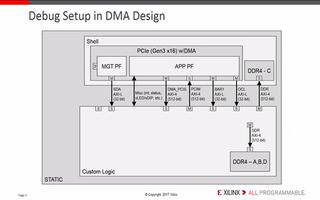

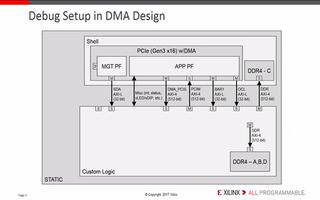

163 本視頻將向您展示為定制邏輯設(shè)計添加調(diào)試內(nèi)核的步驟。此外,它還包含一個演示,展示如何使用Vivado硬件管理器連接F1實例,如何調(diào)試在膝上型電腦/ Linux機器上運行的定制邏輯

設(shè)計。

2018-11-21 06:13:00 2932

2932

本文檔的主要內(nèi)容詳細(xì)介紹的是三菱PLC-FX軟件應(yīng)用程序免費下載。

2018-12-26 14:15:47 19

19 今天我們主要學(xué)習(xí)西門子PLC的程序下載步驟,下面以S7-200SMART為例進(jìn)行說明.

2019-07-25 11:25:50 26742

26742 PLC程序設(shè)計一般分為以下幾個步驟

2020-05-13 08:51:31 9638

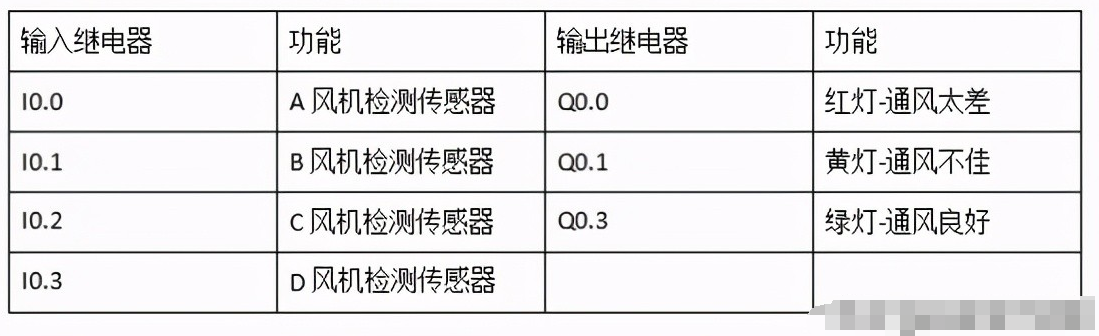

9638 組合邏輯設(shè)計法適合于設(shè)計開關(guān)量控制程序,它是對控制任務(wù)進(jìn)行邏輯分析和綜合,將元件的通、斷電狀態(tài)視為以觸點通、斷狀態(tài)為邏輯變量的邏輯函數(shù),對經(jīng)過化簡的邏輯函數(shù),利用PLC邏輯指令可順利地設(shè)計出滿足要求且較為簡練的程序。這種方法設(shè)計思路清晰,所編寫的程序易于優(yōu)化。

2020-05-22 08:49:00 3842

3842 就是應(yīng)用邏輯代數(shù)以邏輯組合的方法和形式設(shè)計程序。邏輯法的理論基礎(chǔ)是邏輯函數(shù),邏輯函數(shù)就是邏輯運算與、或、非的邏輯組合。

2020-06-04 11:49:49 4101

4101 本文檔的主要內(nèi)容詳細(xì)介紹的是數(shù)字電路與邏輯設(shè)計實驗報告模板。

2020-06-05 08:00:00 8

8 PLC的種類很多,功能和指令不同,但結(jié)構(gòu)和工作原理相似,通常由主機,輸入/輸出接口,功率擴(kuò)展器接口和外部設(shè)備接口等幾個主要部分組成。你對六種常見的應(yīng)用程序了解多少? 1、主機。 主機部分包括處理器

2020-06-17 14:40:33 4359

4359 在了解了程序結(jié)構(gòu)和編程方法的基礎(chǔ)上,就要實際地編寫PLC程序了。編寫PLC 程序和編寫其他計算機程序一樣,都需要經(jīng)歷如下過程。

2020-09-11 16:12:00 22

22 隨著機器人核心關(guān)鍵技術(shù)不斷的發(fā)展,經(jīng)過很長一個階段的技術(shù)攻關(guān),巡檢機器人已走在相關(guān)領(lǐng)域的前沿,并且可以實現(xiàn)設(shè)備安全管理、園區(qū)安全管理,因此,國辰機器人就將園區(qū)巡檢機器人及管理分為5大步驟,供大家參考。

2020-12-30 10:20:13 2899

2899 采用PLC作為中間過程控制的電梯電氣控制,在電路原理圖和安裝接線圖設(shè)計繪制完成后,還必須設(shè)計繪制與電路原理圖對應(yīng)的PLC梯形圖程序,梯形圖程序是PLC內(nèi)各種軟硬繼電器的邏輯控制圖

2021-04-04 17:15:00 3329

3329 我們都知道PLC控制程序是整個PLC控制系統(tǒng)的關(guān)鍵,程序指令的好壞對控制系統(tǒng)的性能也有影響,可能大部分初學(xué)者對程序設(shè)計感覺很困難,不知道如何下手。

2021-04-18 11:33:46 3399

3399

機載機電管理系統(tǒng)的通道故障邏輯設(shè)計

2021-06-22 14:15:49 16

16 一、邏輯設(shè)計 (1)組合邏輯設(shè)計 下面是一些用Verilog進(jìn)行組合邏輯設(shè)計時的一些注意事項: ①組合邏輯可以得到兩種常用的RTL 級描述方式。第一種是always 模塊的觸發(fā)事件為電平敏感信號列表

2021-06-23 17:45:10 4643

4643

設(shè)計plc控制系統(tǒng)時,除了解決輸出部件和輸入部件的連線方式外,最主要的工作是程序設(shè)計與調(diào)試。通常程序設(shè)計按如下步驟進(jìn)行。 (1)了解被控系統(tǒng)的工藝過程和控制要求,并作出流程圖,以描述控制過程

2021-12-17 16:17:31 2772

2772 《數(shù)字電路與邏輯設(shè)計》李曉輝版課后答案詳解

2021-12-27 11:18:39 0

0 。PLC系統(tǒng)調(diào)試一般可按以下步驟進(jìn)行:應(yīng)用程序離線調(diào)試、控制系統(tǒng)硬件檢查、應(yīng)用程序在線調(diào)試、現(xiàn)場調(diào)試。經(jīng)過調(diào)試、總結(jié)和整理相關(guān)信息,系統(tǒng)可以正式投入使用。(初學(xué)者可以結(jié)合plc視頻教程來學(xué)習(xí)) 一.通電前檢查 一般情況下,通電前確認(rèn)PLC處

2022-01-12 11:13:55 7939

7939 很多讀者對于怎么進(jìn)行約束,約束的步驟過程有哪些等,不是很清楚。明德?lián)P根據(jù)以往項目的經(jīng)驗,把時序約束的步驟,概括分成四大步

2022-07-02 10:56:45 4974

4974

我在數(shù)字邏輯設(shè)計方面并沒有經(jīng)驗。也就是說,直到最近我才決定嘗試設(shè)計自己的 CPU,并在 FPGA 上運行!如果你也是一名軟件工程師,并對硬件設(shè)計有興趣,那么我希望這一系列關(guān)于我所學(xué)到的知識的文章能夠?qū)δ阌兴鶐椭⒆屇愀械接腥ぁ1鞠盗形恼碌牡谝徊糠种校瑢⒒卮鹨韵聠栴}:

2022-11-01 09:25:03 1255

1255 上文中我們指出,不管我們是創(chuàng)建自定義 ASIC 芯片還是配置 FPGA,都可以使用相同的數(shù)字邏輯設(shè)計工具。

2022-11-01 09:23:39 1442

1442 PLC梯形圖是根據(jù)PLC程序設(shè)計的邏輯流程圖畫出來的。PLC程序設(shè)計的邏輯流程圖是由輸入、處理和輸出三個部分組成的,用于描述PLC系統(tǒng)中控制邏輯的運作過程。在梯形圖中,輸入和輸出通常表示為開關(guān)、傳感器和執(zhí)行器等硬件元件,而所有的處理邏輯則以梯形的形式展現(xiàn)。

2023-03-16 16:02:20 8778

8778 控制的邏輯并根據(jù)該邏輯編寫梯形圖邏輯程序。而篇文章,我們將詳細(xì)地寫在梯形圖(LAD)PLC程序為這個簡

單的水泵系統(tǒng),并在部分本示例的第3部分,我們將使用 PLC 模擬器S7-PLCSIMV16對其進(jìn)行測試。

2023-04-18 10:33:30 0

0 。PLC系統(tǒng)調(diào)試一般可按以下步驟進(jìn)

行:應(yīng)用程序離線調(diào)試、控制系統(tǒng)硬件檢查、應(yīng)用程序在線調(diào)試、現(xiàn)場調(diào)試。經(jīng)過調(diào)試、總結(jié)和整理相關(guān)信息,系統(tǒng)可以正式

投入使用。(初學(xué)者可以結(jié)合plc視頻教程來學(xué)習(xí)

2023-04-18 09:49:45 11

11 PLC應(yīng)用程序應(yīng)最大限度地滿足被控對象的控制要求,在構(gòu)思程序主體的框架后,要以它為主線,逐一編寫實現(xiàn)各控制功能或各子任務(wù)的程序。

2023-06-25 10:04:52 154

154

電器硬件的工作中而引申出來的,借用它可以分析與確定相關(guān)的邏輯量間的時序關(guān)系。采用時序圖法設(shè)計 PLC 程序的一般步驟如下:

2023-10-05 09:55:00 2065

2065 電路板抄板簡稱抄板,是對現(xiàn)有的電路板進(jìn)行克隆而進(jìn)行的反向技術(shù)研究。電路板抄板步驟如下:

2023-11-18 16:23:44 1063

1063 怎么讀取plc中已存在的程序呢? PLC(可編程邏輯控制器)是一種重要的自動化設(shè)備,用于控制和監(jiān)控各種工業(yè)過程。PLC中的程序是由用戶編寫的,它們定義了PLC在操作中的行為。本文將詳細(xì)介紹如何讀取

2023-11-21 16:10:45 3172

3172 電子發(fā)燒友網(wǎng)站提供《成功實現(xiàn)功率器件熱設(shè)計的4大步驟.pdf》資料免費下載

2023-11-22 09:58:17 0

0 ava是一種面向?qū)ο蟮木幊陶Z言,廣泛用于開發(fā)各種類型的應(yīng)用程序。在開發(fā)Java應(yīng)用程序時,有一些基本步驟需要遵循,以確保應(yīng)用程序的正確性和可靠性。 1.確定需求:這是開發(fā)任何應(yīng)用程序的第一步,包括

2023-11-28 16:52:01 504

504 電子發(fā)燒友網(wǎng)站提供《基于TouchGFX的智能手表設(shè)計 —MVP 架構(gòu)下的邏輯設(shè)計.pdf》資料免費下載

2024-01-05 11:21:38 0

0 電子發(fā)燒友網(wǎng)站提供《數(shù)字電路與邏輯設(shè)計.ppt》資料免費下載

2024-03-11 09:21:44 0

0 電子發(fā)燒友網(wǎng)站提供《基于VHDL的組合邏輯設(shè)計.ppt》資料免費下載

2024-03-11 09:23:29 2

2

電子發(fā)燒友App

電子發(fā)燒友App

評論