您的位置:電子發(fā)燒友網(wǎng) > 電子技術(shù)應(yīng)用 > 測(cè)量儀表 > 可靠性分析 >

深亞微米CMOS IC全芯片ESD保護(hù)技術(shù)(3)

2012年03月27日 16:27 來源:本站整理 作者:秩名 我要評(píng)論(0)

(2)VDD加電情形

由于CMOS IC在正常工作時(shí),其VDD是偏壓在一同定的電壓(例如5伏特)。但是在加電瞬間,VDD電壓自0伏特逐漸上升到5伏特,這就是一般所謂power-on瞬時(shí)。在這power-on瞬時(shí),要保持STFOD器件在這power-on情形下仍保持關(guān)閉,但在:ESD放電情形下導(dǎo)通,可通過RC時(shí)間常數(shù)的設(shè)計(jì)來達(dá)到此目的。因?yàn)閂DD power-on電壓上升時(shí)間是約1ms左右,但ESD電壓的上升時(shí)間約10ns,因此把ESD偵測(cè)電路的RC時(shí)間常數(shù)設(shè)在0.1~1.0us之間,它便可以分辨出VDD Power-on與ESD)放電兩種不同的工作情形。

5 全芯片ESD保護(hù)架構(gòu)

ESD保護(hù)電路的安排必須全方位地考慮到ESD測(cè)試的各種組合,因?yàn)橐活wIC的ESD失效閾值定義為整顆IC所有引腳在各種測(cè)試模式下,最低的ESD耐壓值。因此,一個(gè)全芯片ESD保護(hù)電路的安排要如圖6所示,輸入輸出PAD要能夠抑制PS、NS、PD、ND四種模式的靜電放電,另外,VDD到VSS也要有ESD保護(hù)電路。

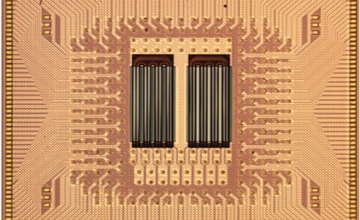

根據(jù)實(shí)際需要,結(jié)合上述各種ESD保護(hù)結(jié)構(gòu),我們提出了一種新穎的深亞微米CMOS IC全芯片ESD保護(hù)架構(gòu)如圖7。其中,輸入輸出PAD外圍ESD保護(hù)電路都采用改進(jìn)的SCR結(jié)構(gòu)。其中,輸入PAD外圍我們選用基于互補(bǔ)式LVTSCR結(jié)構(gòu)設(shè)計(jì)的ESD保護(hù)電路,考慮對(duì)下級(jí)芯片輸入信號(hào)的影響,輸出PAD上采用抗噪聲能力較強(qiáng)HINSCR和HIPSCR器件。實(shí)測(cè)表明,它們對(duì)發(fā)生在輸入輸出PAD上PS、PD、NS和ND四種模式的ESD都起到了很好的抑制作用。

對(duì)于VDD與VSS之間的ESD保護(hù)電路設(shè)計(jì),一方面,要兼顧內(nèi)部電路版岡設(shè)計(jì)規(guī)則和先進(jìn)的工藝要求,保護(hù)電路在能夠?qū)崿F(xiàn)保護(hù)目的的同時(shí),還要盡量節(jié)省版圖面積;另一方面,由于電源地線較長,VDD與VSS上的寄生電阻電容也較大,如果保護(hù)電路的擺放位置離:ESD發(fā)生位置較遠(yuǎn),其保護(hù)作用就會(huì)因卜述寄生參數(shù)影響而削弱。因此ESD保護(hù)電路在芯片中的布局也同樣重要。基于以卜考慮我們采用了節(jié)省芯片面積的sTFOD結(jié)構(gòu)ESD偵測(cè)電路,該電路可完全按照內(nèi)部芯片的版岡設(shè)計(jì)規(guī)則設(shè)計(jì)實(shí)現(xiàn),而且不必增加工藝版次。保護(hù)電路的安放參照了一套現(xiàn)成的ESD布局設(shè)計(jì)規(guī)則,其布局如圖7所示,圍繞電源地線均勻地放在芯片四周,巧妙地避免了電源地線之間寄生參數(shù)的負(fù)面影響。

該全芯片ESD防護(hù)設(shè)計(jì)架構(gòu)已實(shí)際地被用來改善某一IC產(chǎn)品的ESD耐壓能力。該IC產(chǎn)品原本ESD耐壓能力,在輸入/輸出腳對(duì)VDD/VSS ESD放電測(cè)試情形下只能承受1 000V的ESD,在腳對(duì)腳的ESD放電測(cè)試情形下只能承受500V的ESD。經(jīng)過圖7的應(yīng)用之后,該IC的ESD耐壓能力,在輸入/輸出腳對(duì)VDD/VSS ESD測(cè)試下能承受到4000V以上的ESD,在腳對(duì)腳ESD測(cè)試下能承受到3000V以上的ESD。該全芯片ESD架構(gòu)在小布局面積下提供了有效而又高水平的ESD保護(hù)能力。

6 結(jié)論

ESD的防護(hù)是整顆集成電路的問題,而不只是輸入輸出PAD或電源地PAD的問題,即使各個(gè)PAl)都有很好的ESD防護(hù)能力,不見得整顆集成電路就有很高的ESD防護(hù)能力。采用適當(dāng)?shù)娜酒╳hole-chip)防護(hù)架構(gòu)設(shè)計(jì),才能真正提升整顆集成電路的ESD防護(hù)能力。本文采用改進(jìn)SCR結(jié)構(gòu)和STFOD器件,提出了一個(gè)新穎的深亞微米CMOS IC全芯片ESD保護(hù)架構(gòu),該架構(gòu)節(jié)省了布局面積,實(shí)現(xiàn)了對(duì)整個(gè)芯片全方位的ESD保護(hù)。

本文導(dǎo)航

- 第 1 頁:深亞微米CMOS IC全芯片ESD保護(hù)技術(shù)(1)

- 第 2 頁:基于STFOD結(jié)構(gòu)的ESD偵測(cè)電路

- 第 3 頁:VDD加電情形

用戶評(píng)論

發(fā)表評(píng)論

CMOS業(yè)界動(dòng)態(tài)

CMOS技術(shù)應(yīng)用

CMOS資料下載

ESD技術(shù)應(yīng)用

ESD資料下載

- 美信ESD保護(hù)之路

- ESD保護(hù)電路的設(shè)計(jì)

- iCoupler隔離產(chǎn)品的ESD_閂鎖考慮因素

- MAX14780E ESD保護(hù),失效保護(hù),熱插拔,RS485_RS422收發(fā)器

- 雷電與ESD防護(hù)及EMC設(shè)計(jì)-陶顯芳老師講座

- 靜電防護(hù)和多層壓敏電阻

- ESD靜電防護(hù)對(duì)策

- AN2764C 改善基于微控制器的應(yīng)用的瞬態(tài)免疫性能

- CSPESD304 pdf datasheet(4-Channel ESD Array in CSP)

- ESD輻射場(chǎng)測(cè)試研究