DMA Write和Master DMA Read全雙工數(shù)據(jù)傳輸5. PCI Express驅動支持Windows 32/64位、Linux等操作系統(tǒng),如Windriver6. 即插即用,支持熱插拔

2014-08-23 13:15:30

PCI Express有哪幾個版本?它們分別有什么特點?PCI Express在嵌入式系統(tǒng)中有哪些應用?

2021-04-26 06:39:24

還將就PC 總線技術的演變歷程、PCI Express 的物理層和軟件層、PCI Express 所能帶來的益處和競爭優(yōu)勢以及此項嶄新技術在測量自動化系統(tǒng)領域里預示的令人振奮的深遠意義,做個整體技術性

2019-05-10 07:00:07

各位大神,我想請問嵌入式系統(tǒng)開發(fā)還要學習信號系統(tǒng),DSP嗎?

2012-06-18 17:53:40

我是電子專業(yè)學生,最近剛剛接觸了嵌入式系統(tǒng),很有興趣學習,但對其不太了解,有哪位有很好的適合初學者的嵌入式教程或書籍可以分享一下,謝謝了。

2013-09-26 13:25:32

嵌入式系統(tǒng)EMC(Electro Magnetic Compatibility)即嵌入式系統(tǒng)電磁兼容性,指嵌入式系統(tǒng)在復雜電磁環(huán)境中抵抗其他系統(tǒng)所產(chǎn)生的電磁干擾同時本身產(chǎn)生的電磁干擾又不影響其他系統(tǒng)

2019-08-20 08:08:59

一篇講透嵌入式系統(tǒng)內存分配方式

2021-12-17 07:40:53

、設備驅動接口、通信協(xié)議、圖形界面、標準化瀏覽器等。嵌入式操作系統(tǒng)負責嵌入式系統(tǒng)的全部軟、硬件資源的分配、任務調度,控制、協(xié)調并發(fā)活動。它必須體現(xiàn)其所在系統(tǒng)的特征,能夠通過裝卸某些模塊來達到系統(tǒng)所要

2020-06-23 11:02:33

山東科技大學 張煒韓進引 言隨著嵌入式系統(tǒng)應用的迅速發(fā)展,PDA和移動電話等便攜式裝置深入到生產(chǎn)生活的各個角落,嵌入式系統(tǒng)市場有迅速增長趨勢。嵌入式系統(tǒng)一般是由電池來供給電能的,而且大多數(shù)嵌入式設備

2019-07-19 06:17:21

創(chuàng)客學院嵌入式培訓講師:嵌入式它的定義實在是太廣泛了.從字面意義理解起來甚至容易讓人糊涂,現(xiàn)在嵌入式系統(tǒng)的概念也有被濫用的嫌疑。在一般的文獻中嵌入式系統(tǒng)是這樣定義的:嵌入式系統(tǒng)是以應用為中心,以

2017-06-29 15:55:43

什么是嵌入式系統(tǒng)?嵌入式微處理器有哪些特點?與通用型計算機系統(tǒng)相比,嵌入式計算機系統(tǒng)具有哪些特點?

2021-04-26 07:21:48

什么是嵌入式系統(tǒng)?怎樣去搭建一種嵌入式開發(fā)環(huán)境呢?

2021-10-19 07:46:35

什么是嵌入式系統(tǒng)?嵌入式系統(tǒng)是由哪些部分組成的?

2021-10-29 06:50:41

嵌入式系統(tǒng)是由哪些部分組成的?實時嵌入式系統(tǒng)特征有哪些?嵌入式移動數(shù)據(jù)庫管理系統(tǒng)的數(shù)據(jù)同步機制特點是什么?

2021-12-23 09:27:25

中間人攻擊、黑客攻擊、間諜和篡改、內存數(shù)據(jù)錯誤——嵌入式系統(tǒng)面臨各種威脅。儒卓力GDPR專家團隊主管兼嵌入式和無線部門營銷總監(jiān)Bertron Hantsche提供了六個安全技巧,以便增強在嵌入式系統(tǒng)中傳輸、保存和處理數(shù)據(jù)的安全性。

2019-10-18 06:28:46

嵌入式系統(tǒng)的特點有哪些呢?嵌入式系統(tǒng)有哪些應用呢?

2021-11-09 07:49:38

隨著后PC時代以及網(wǎng)絡、通信技術時代的到來,大量的計算機專業(yè)人員進入了嵌入式應用領域;然而,有大量的嵌入式系統(tǒng)應用是以單片機的形式,應用在傳統(tǒng)的電子技術領域中。因此,以計算機領域人員為主體的,遠離

2019-09-05 07:36:09

摘要:嵌入式系統(tǒng)誕生于微型機時代,經(jīng)歷了漫長的獨立發(fā)展的單片機道路。給嵌入式系統(tǒng)尋求科學的定義,必須了解嵌入式系統(tǒng)的發(fā)展歷史,按照歷史性、本質性、普遍通用性來定義嵌入式系統(tǒng),并把定義與特點相區(qū)分

2019-06-18 06:53:07

隨著電子產(chǎn)品的發(fā)展,嵌入式系統(tǒng)已經(jīng)廣泛地應用我們的生活的各個領域,例如:計算機、汽車、航天飛機等等。提到嵌入式系統(tǒng)首先聯(lián)想到單片機,是的,MCU是最基礎和常用的嵌入式系統(tǒng)。嵌入式系統(tǒng)與模擬電路或其他

2020-03-18 08:17:50

嵌入式系統(tǒng)基礎知識總結

2021-01-22 07:30:14

什么是電子系統(tǒng)的實時性三類電子應用系統(tǒng)的實時性嵌入式系統(tǒng)的實時性分析嵌入式應用系統(tǒng)的實時性設計

2021-04-22 07:12:27

時間管理要提供高精度且應用可設置的系統(tǒng)時鐘,該時鐘是嵌入式系統(tǒng)的時基,實時系統(tǒng)的時鐘精度一般要求10MS以下,最好是微秒級的,賢時間清空要提供日歷時間,負責與時間相關的任務管理工作,如任務對資源有限

2021-12-21 08:11:57

嵌入式系統(tǒng)的知識體系嵌入式系統(tǒng)的學習誤區(qū)嵌入式系統(tǒng)基礎階段的學習建議

2021-02-19 07:06:43

嵌入式系統(tǒng)和組件技術嵌入式系統(tǒng)組件的設計原則面向嵌入式組件的系統(tǒng)開發(fā)過程

2021-04-23 06:08:06

時,bit0為“0”,而當其映射到I/O地址空間時,bit0為“1”。 在驅動PCI設備時,首先是PCI設備的查找。嵌入式操作系統(tǒng)一般都提供有相應的API函數(shù)查找。而在VxWorks操作系統(tǒng)中,通過

2011-05-27 10:21:26

嵌入式系統(tǒng)近來年是當前最熱門最有發(fā)展前途的IT應用領域之一。嵌入式系統(tǒng)用在一些特定專用設備上,通常這些設備的硬件資源(如處理器、存儲器等)非常有限,并且對成本很敏感,有時對實時響應要求很高

2020-06-22 09:20:58

嵌入式設備由于具有硬件可在線配置,實現(xiàn)靈活等特點,使得其應用越來越廣泛。尤其在基于FPGA的硬件系統(tǒng)中應用較多,目前在許多產(chǎn)品中實現(xiàn)了嵌入式網(wǎng)口、嵌入式PCI/PCI-E、嵌入式USB等各種模塊

2020-03-09 06:54:45

近年來,隨著信息家電、手持設備、無線設備的迅速發(fā)展,人們對嵌入式系統(tǒng)的需求逐漸增多,要求也越來越高。這使為嵌入式系統(tǒng)提供一個友好方便、穩(wěn)定可靠的G UI系統(tǒng)成為非常緊迫要求[5]。嵌入式技術是當前

2019-08-14 07:52:37

隨著通用處理器和嵌入式技術的迅猛發(fā)展,越來越多的電子設備需要由處理器控制。目前大多數(shù)CPU和外部設備都會提供PCI總線的接口,PCI總線已成為計算機系統(tǒng)中一種應用廣泛、通用的總線標準[1

2011-10-08 09:44:30

本文創(chuàng)客學院嵌入式開發(fā)培訓講師為讀者介紹嵌入式基礎教程之嵌入式系統(tǒng)組成,嵌入式系統(tǒng)通常由嵌入式處理器、外圍設備接口、嵌入式操作系統(tǒng)、應用軟件的嵌入式計算機系統(tǒng)和執(zhí)行裝置(被控對象)組成

2017-06-28 13:59:20

從系統(tǒng)的觀點來看,嵌入式實時系統(tǒng)也是系統(tǒng),特別是硬件技術的快速發(fā)展,嵌入式實時軟件也有快速適應硬件型號升級問題,也有業(yè)務快速變更要求以及可伸縮、可修改、可復用等方面的問題。但面向對象技術對于實時性、可靠性的描述并不適合,在嵌入式實時應用中依然不是主流設計方法,從而引入了模式的概念。

2019-10-08 11:35:54

在嵌入式領域中,嵌入式實時操作系統(tǒng)(RTOS)正得到越來越廣泛的應用。采用嵌入式實時操作系統(tǒng)可以更合理、更有效地利用CPU的資源,簡化應用軟件的設計,縮短系統(tǒng)開發(fā)時間,更好地保證系統(tǒng)的實時性和可靠性。內存資源作為嵌入式系統(tǒng)中極為重要的資源之一,其管理機制歷來是嵌入式系統(tǒng)設計的重點和難點。

2020-11-25 06:48:44

嵌入式操作系統(tǒng)是ARM CPU的軟件基礎,從8位/16位單片機發(fā)展到以arm CPU核為代表的32位嵌入式處理器,嵌入式操作系統(tǒng)將替代傳統(tǒng)的由手工編制的監(jiān)控程序或調度程序,成為重要的基礎組件。更重

2020-04-07 07:13:19

隨著嵌入式相關技術的迅速發(fā)展,嵌入式系統(tǒng)的功能越來越強大,應用接口更加豐富,根據(jù)實際應用的需要設計出特定的嵌入式最小系統(tǒng)和應用系統(tǒng),是嵌入式系統(tǒng)設計的關鍵。

2020-04-01 06:11:24

嵌入式邊界掃描是什么?嵌入式邊界掃描系統(tǒng)主要有哪些結構?怎樣去實現(xiàn)嵌入式邊界掃描系統(tǒng)?

2021-04-15 07:01:49

隨著嵌入式相關技術的迅速發(fā)展,嵌入式系統(tǒng)的功能越來越強大,應用接口更加豐富,根據(jù)實際應用的需要設計出特定的嵌入式最小系統(tǒng)和應用系統(tǒng),是嵌入式系統(tǒng)設計的關鍵。目前在嵌入式系統(tǒng)開發(fā)的過程中,開發(fā)者往往把

2019-10-31 07:30:41

你好,我目前正在研究Kintex 7 KC705開發(fā)板上的項目。我需要做的是通過使用電路板的PCI Express功能從Linux操作系統(tǒng)訪問電路板上的系統(tǒng)(基于AXI)。但是,有一個混亂,因為我

2020-07-20 14:44:49

嵌入式系統(tǒng)設計方法變化的背景嵌入式系統(tǒng)設計方法的變化嵌入式系統(tǒng)設計的3個層次

2021-04-26 06:10:29

Linux作為嵌入式操作系統(tǒng)的優(yōu)勢是什么如何建立嵌入式Linux?當前流行的幾種嵌入式Linux系統(tǒng)

2021-04-27 06:34:40

工作方式,該方式將嵌入式系統(tǒng)設計成板卡形式,并通過主機的PCI接口進行數(shù)據(jù)傳輸。這種方式具有一定的獨立性,可承擔某項特定的任務,從而可使主機CPU的開銷大大減少。常用的視頻壓縮卡、工業(yè)數(shù)據(jù)采集卡等都屬此種

2021-05-12 07:00:00

作者:張仁杰、蔡柏玨,凌華科技工業(yè)計算機產(chǎn)品事業(yè)部在嵌入式計算機產(chǎn)業(yè)中,將主板與外圍板卡通過背板相連接的這種基本構造,已經(jīng)廣泛地被業(yè)界所接受。此類規(guī)格的最早標準就是PICMG 1.0規(guī)范,支持通過

2019-07-19 08:18:21

Express Pi是什么?Express Pi嵌入式開發(fā)板有哪些功能配置?Express Pi嵌入式開發(fā)板有哪些特點呢?

2021-12-27 06:33:31

嵌入式系統(tǒng)的概念有多種不同的說法,常見的一種說法是:嵌入式系統(tǒng)是以應用為中心,以計算機技術為基礎,軟硬件可裁剪,對功能、可靠性、成本、體積和功耗有嚴格要求的專用計算機系統(tǒng)。還有一種說法:嵌入式系統(tǒng)

2019-09-23 15:57:38

什么是嵌入式系統(tǒng)中的外設嵌入式系統(tǒng)的各種常見外設總結

2021-04-02 07:06:08

經(jīng)過近幾年的快速發(fā)展,嵌入式系統(tǒng)(EmbeddedSystem)已經(jīng)成為電子信息產(chǎn)業(yè)中最具增長力的一個分支。隨著手機、PDA,GPS、機頂盒等新興產(chǎn)品的大量應用,嵌入式系統(tǒng)的市場正在以每年30%的速度遞增(IDC預測),嵌入式系統(tǒng)的設計也成為軟硬件工程師越來越關心的話題。

2019-10-29 06:38:46

嵌入式系統(tǒng)中對內存分配有哪些要求呢?

2019-10-29 08:32:07

目錄一、什么是嵌入式系統(tǒng)1、嵌入式系統(tǒng)的特點:2、嵌入式系統(tǒng)的軟件組成:軟件(含驅動、OS、應用層) + 硬件3、嵌入式系統(tǒng)硬件組成3.1、嵌入式處理器(CPU):嵌入式系統(tǒng)的核心部分,分為:3.2、外圍設備:...

2021-12-22 07:32:30

什么是嵌入式系統(tǒng)?嵌入式處理器可分為哪幾類?嵌入式操作系統(tǒng)有哪幾類?

2021-04-25 06:35:32

物聯(lián)網(wǎng)中“事物”的定義差異很大。我們將事務定義為通過網(wǎng)絡發(fā)送和接收信息的嵌入式計算設備(或嵌入式系統(tǒng))。什么是嵌入式系統(tǒng)?嵌入式系統(tǒng)基于微控制器(MCU),并運行占用內存少的軟件。某些基于Linux

2021-12-21 06:48:10

什么是嵌入式操作系統(tǒng)?常見的嵌入式操作系統(tǒng)有哪幾種?嵌入式操作系統(tǒng)有何功能?

2021-12-24 07:07:38

嵌入式系統(tǒng)的主要作用是什么嵌入式組態(tài)軟件包的組態(tài)環(huán)境包括什么MCGS嵌入式組態(tài)軟件提供什么功能?

2021-04-22 07:09:42

什么是嵌入式?嵌入式系統(tǒng)是由哪些部分組成的?嵌入式系統(tǒng)的評價方法有哪幾種呢?

2021-11-04 06:21:10

嵌入式系統(tǒng)中對內存分配有什么要求?靜態(tài)分配與動態(tài)分配有何不同?一次分配多次使用的內存分配方案有什么特點?

2021-04-27 06:01:50

基于PCI Express的數(shù)據(jù)采集卡PCIe數(shù)據(jù)采集卡PCI Express數(shù)據(jù)采集卡本人在北京工作6年以上,從事FPGA外圍接口設計,非常熟悉PCI Express協(xié)議,設計調試了多個基于PCI

2014-03-20 22:58:55

1嵌入式軟PLC的總體結構 嵌入式軟PLC與嵌入式系統(tǒng)共享一個CPU,PLC和嵌入式系統(tǒng)之間沒有多余的導線連接,增加了系統(tǒng)的可靠性,易于實現(xiàn)許多高級功能。PLC中的信息也能通過嵌入式系統(tǒng)的顯示屏顯示,通過嵌入式系統(tǒng)的編輯鍵可方便地對PLC進行編輯操作。

2019-06-19 06:20:54

基于嵌入式WEB技術的網(wǎng)絡視頻監(jiān)控系統(tǒng)特征及原理是什么?基于嵌入式WEB技術的網(wǎng)絡視頻監(jiān)控系統(tǒng)硬件設計基于嵌入式WEB技術的網(wǎng)絡視頻監(jiān)控系統(tǒng)軟件設計

2021-06-02 07:15:51

基于DSP的Bluetooth嵌入式系統(tǒng)應用是什么?

2021-05-27 07:02:56

顧名思義,嵌入式系統(tǒng)指的是嵌入到系統(tǒng)內部的計算機系統(tǒng),是面向特定應用設計的專用計算機系統(tǒng)。早期的嵌入式系統(tǒng)一般是以通用處理器或單片機為核心,在外圍電路中加入存儲器、功率驅動器、通信接口、顯示接口

2019-06-28 06:18:21

都說嵌入式很難,即使去嵌入式培訓機構做系統(tǒng)訓練,其實只是沒有掌握正確的學習嵌入式的方法,學習講究的是一個循序漸進的過程,誰也不能一口吃出一個大胖子,從基礎到專業(yè),從簡單到高深,下面達內講解一下系統(tǒng)學習嵌入式培訓的基本步驟:

2021-03-09 06:23:10

嵌入式---內存分配管理嵌入式的內存一般都非常的小,最進在學習LWIP協(xié)議棧的移植,在正點原子的學習資料中找到了許多關于怎么移植協(xié)議棧的東西,其中使用到了內存的分配管理技術,能夠高效的管理和使用內存

2021-12-17 06:41:46

嵌入式系統(tǒng)簡單介紹(入門)嵌入式操作系統(tǒng)是一種運行在嵌入式相關產(chǎn)品中的操作系統(tǒng),它的主要作用是負責任務的調度,內存的分配以及數(shù)據(jù)的存儲等。常見的嵌入式產(chǎn)品有手機,平板,自助取款機,收銀臺結算機等等

2021-12-17 07:31:39

如何去設計嵌入式SMP的硬件系統(tǒng)?如何去設計嵌入式SMP的軟件系統(tǒng)?

2021-04-27 06:56:14

如何快速學習嵌入式?常見的嵌入式系統(tǒng)有哪些?什么是嵌入式操作系統(tǒng)?

2021-04-19 07:01:55

實時嵌入式系統(tǒng)與網(wǎng)絡的結合以及高可信覆蓋網(wǎng)絡的發(fā)展使得嵌入式實時操作系統(tǒng)的安全性問題日益突出。提高實時嵌入式系統(tǒng)的安全性和可靠性是未來實時嵌入式系統(tǒng)發(fā)展的重要方向之一。

2019-10-30 06:03:36

Linux操作系統(tǒng)成為嵌入式操作系統(tǒng)的首選是什么原因?如何構造嵌入式Linux系統(tǒng)?

2021-04-26 06:31:42

嵌入式程序開發(fā)基本概念如何滿足嵌入式系統(tǒng)的靈活需求開發(fā)高效程序的技巧是什么

2021-04-28 06:07:27

在嵌入式系統(tǒng)設計過程中,系統(tǒng)的掉電保護越來越受到重視。如何設計嵌入式系統(tǒng)掉電保護方案?這個問題急需解決。

2019-08-09 07:48:28

嵌入式設備由于具有硬件可在線配置,實現(xiàn)靈活等特點,使得其應用越來越廣泛。尤其在基于FPGA的硬件系統(tǒng)中應用較多,目前在許多產(chǎn)品中實現(xiàn)了嵌入式網(wǎng)口、嵌入式PCI/PCI-E、嵌入式USB等各種模塊

2019-08-08 07:03:56

隨著通用處理器和嵌入式技術的迅猛發(fā)展,越來越多的電子設備需要由處理器控制。目前大多數(shù)CPU和外部設備都會提供PCI總線的接口,PCI總線已成為計算機系統(tǒng)中一種應用廣泛、通用的總線標準[1

2019-08-13 07:49:42

PCI Express (PCIe)是嵌入式和其它系統(tǒng)類型的背板間通信的一個非常理想的協(xié)議。然而,在嵌入式環(huán)境中,背板連接器引腳通常很昂貴。因此,采用點對點連接的星型結構的PCIe時鐘分配方案就變得

2019-09-26 07:56:41

PCI Express (PCIe)是嵌入式和其它系統(tǒng)類型的背板間通信的一個非常理想的協(xié)議。然而,在嵌入式環(huán)境中,背板連接器引腳通常很昂貴。因此,采用點對點連接的星型結構的PCIe時鐘分配方案就變得

2019-08-30 06:54:47

系列文章:一篇講透嵌入式操作系統(tǒng)任務調度從需求反推設計方案,假如讓你設計嵌入式系統(tǒng)的內存管理,你怎么設計?最簡單的,用一個雙鏈表控制,所有已分配和未分配的內存用兩個雙鏈表標識:...

2021-12-17 06:54:55

嵌入式系統(tǒng)是如何定義的?可從哪幾方面來理解嵌入式系統(tǒng)呢?

2021-10-18 06:54:52

為什么要設計一種嵌入式演示系統(tǒng)?怎樣去設計嵌入式演示系統(tǒng)?嵌入式演示系統(tǒng)目前還存在哪些問題?

2021-04-22 06:13:30

汽車嵌入式系統(tǒng)發(fā)展歷程怎樣去設計汽車嵌入式SoC系統(tǒng)?SoC系統(tǒng)有哪些典型應用?

2021-05-12 07:18:32

什么是嵌入式系統(tǒng)?嵌入式處理器的體系架構可分為哪幾種形式?嵌入式操作系統(tǒng)具備哪些特點?嵌入式系統(tǒng)主要有哪些應用領域?

2021-08-06 07:01:50

嵌入式系統(tǒng)是泛計算領域的重要組成部分,是嵌入式對象宿主體系中完成某種特定功能的專用計算機系統(tǒng)。嵌入式系統(tǒng)有體積小、低功耗、集成度高、子系統(tǒng)間能通信融合的優(yōu)點。隨著汽車技術的發(fā)展以及微處理器技術

2019-08-02 07:35:56

控制,一種是嵌入式控制。今天我們就來聊聊在測試系中遠程控制器和嵌入式控制器有什么區(qū)別。遠程控制器 對于PXI系統(tǒng)來說,如何來實現(xiàn)對儀器的遠程控制呢?用戶可以使用PC或筆記本電腦通過一個軟件透明的鏈接控制PXI系統(tǒng),這其中還包括電腦中的一個PCI/PCI Express板卡...

2021-12-21 08:12:55

UML引入到嵌入式系統(tǒng)中的可行性一種改進的通用嵌入式系統(tǒng)UML方案如何使用UML來設計嵌入式系統(tǒng)?

2021-04-23 06:12:34

如何去編寫嵌入式系統(tǒng)啟動程序?設計嵌入式系統(tǒng)啟動程序的步驟流程有哪些?設計嵌入式系統(tǒng)啟動程序有哪些技術難點?

2021-04-25 09:18:23

嵌入式系統(tǒng)是以應用為中心,以計算機技術為基礎,并且軟硬件可裁剪,適用于應用系統(tǒng)對功能、可靠性、成本、體積、功耗有嚴格要求的專用計算機系統(tǒng)。它一般由嵌入式微處理器、外圍硬件設備、嵌入式操作系統(tǒng)以及用戶

2020-04-03 06:21:26

PCI Express 至PCI 橋設計原理及應用

功能一般功能• PCI Express 至 PCI 橋• 透明、非透明及不透明模式• 有效的排隊及緩沖,實現(xiàn)

2010-03-06 11:16:26 35

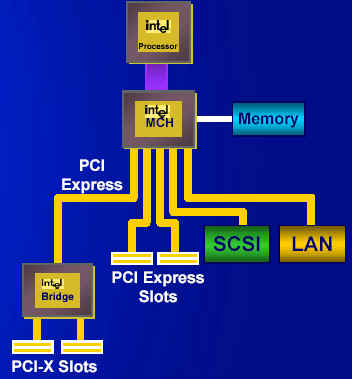

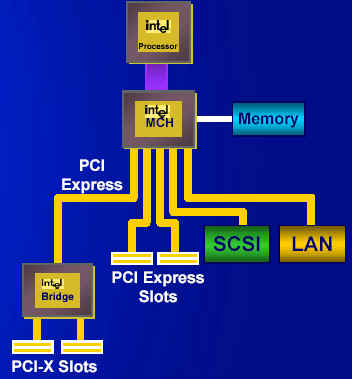

35 PCI-Express*概覽

Intel® Developer Network for PCI Express* Architectur

2006-12-25 15:10:22 1621

1621

PCI Express是新一代能夠提供大量帶寬和豐富功能以實現(xiàn)令人激動的新式圖形應用的全新架構。PCI Express可以為帶寬渴求型應用分配相應的帶寬,大幅提高中央處理器(CPU)和圖形處

2006-12-25 15:16:56 2640

2640 PCI Express插槽,什么是PCI Express插槽,PCI Express插槽外形圖

PCI-Express是最新的總線和接口標準,它原來的名稱為“3GIO”,是由英特爾提出的,很明顯英特

2009-04-26 18:19:16 4915

4915 什么是PCI Express接口 PCI Express(以下簡稱PCI

2009-12-25 10:32:47 2505

2505 PCI Express總線

其實,PCI Express是一個計算機系統(tǒng)總線的名稱,不過大家聽得最多的還是“接口”這個詞,也沒錯,PCI Express的確是下一

2010-01-22 11:21:51 627

627 中國,北京-2014年10月9日-高性能模擬與混合信號IC領導廠商Silicon Labs(芯科實驗室有限公司, NASDAQ:SLAB)今天宣布針對消費電子和嵌入式應用推出業(yè)界最小尺寸的符合PCI Express(PCIe)標準的時鐘發(fā)生器芯片,在這些應用中可靠性、板面積、器件數(shù)量和功耗通常是其關鍵設計要素。

2014-10-09 14:16:51 1445

1445

本視頻介紹了在使用AXI Bridge for PCI Express Gen3子系統(tǒng)時創(chuàng)建使用Tandem with Field Updates流程的PCI Express解決方案的過程。

2018-11-29 06:12:00 2730

2730 設計的帶嵌入式收發(fā)器的Gen1×1硬核IP的 PCI Express IP編譯器(基于嵌入式開發(fā)游戲項目)-在Cyclone IV GX收發(fā)器入門套件上,設計帶嵌入式收發(fā)器的Gen1×1硬核IP的 PCI Express IP編譯器。.rar

2021-07-30 16:48:41 9

9

正在加载...

電子發(fā)燒友App

電子發(fā)燒友App

評論