本文介紹一個FPGA常用模塊:SRIO(Serial RapidIO)。SRIO協議是一種高速串行通信協議,在我參與的項目中主要是用于FPGA和DSP之間的高速通信。有關SRIO協議的詳細介紹網上有很多,本文主要簡單介紹一下SRIO IP核的使用和本工程的源代碼結構。

2023-12-12 09:19:08 855

855

名為XMM8060,兩款5G基帶芯片將用于2019年上半年問市的5G智能手機。 在5G標準凍結后,華為率先在巴塞羅那世界移動通信大會(MWC)發布首款5G商用芯片--巴龍5G01(Balong 5G01),成為全球第三家發布5G商用基帶芯片廠.

2018-02-27 07:06:46 2642

2642 6657的SRIO設計要注意哪些?

2016-10-10 23:18:10

Keystone_SRIO_Init(&srio_cfg);之后,接收即終止了,之后也沒辦法繼續接收FPGA傳輸的數據。而此時DSP可以正常向FPGA傳輸數據。

??????? 不知道是不是因為沒有添加

2018-06-21 13:16:48

; FPGA

? ? ? ? 1、STK中的external line loopback工作方式好像滿足我的需求,但似乎前提是連接雙方必須在SRIO協議基礎上建立物理層的連接才可以進行測試。由于FPGA端

2018-06-21 06:25:29

各位大佬,你們好。我現在使用TI官方的6678 bootloader源碼,改造后實現以下功能:1.通過以太網加載程序;2.能夠boot成功;3.以太網功能正常。但是我遇到一個比較棘手的問題,就是當

2021-09-23 09:16:48

各位專家好!請問:我現在想通過6678的SRIO接收來自FPGA的數據,DSP作為從屬。用的是論壇給的KI_STK_V1.1的SRIO例程,在test between 2 DSPs的程序段里修改

2019-01-11 07:33:39

IP CORE SRIO 2.1 ENDPOINT ECP3

2023-03-30 12:02:57

SITE LICENSE SRIO 2.1 ECP3

2023-03-30 12:03:00

各位好!

? ? ? ?參考Ti給的例程,發現SRIO中斷是直接配置寄存器,然后再SRIO_vector.asm文件中完成中斷服務函數入口的映射,而主機PC和DSP的交互是通過利用CSL庫函數來完成中斷配置,我想問一下:兩種中斷配置方式能同時寫在同一個函數里面嗎?

謝謝!

2018-06-21 08:43:37

的,uicompletioncode是LSU_STAT中的。這句程序是函數Keystone_SRIO_wait_LSU_completion的。謝謝。。。

2018-06-21 06:46:55

C6678和C6455使用SRIO通信,1x4p模式,3.125G,其中C6678使用TI的PDK中SRIO LLD

發現C6455發送過快時候C6678的接收緩存不夠,觸發StarvationQ

2018-06-21 09:01:47

專家好: 調試接口時經常會出現重新load程序的情況,發現如果SRIO雙方已經進行數據通信,重新加載程序進行SRIO初始化后,srio鏈路不通了,需要重新斷電重連,這樣調試起來比較浪費時間,請問有什么好的方法,可以節省調試時間

2019-01-07 11:15:23

現在,我在ISE13.1軟件中使用srio_v5_6 Ip內核。我使用CORE生成器為X6VLX240T-1156-1設備生成一個srio_v5_6 IP內核。然后我用ISE13.1軟件打開

2018-10-08 11:10:47

1.我使用的是c6670的例子工程SRIO_LoopbackDioIsrexampleproject,在evm板子上跑了一下,從運行完畢打印出來的log中發現只有核0執行了dio,而核1沒有運行

2018-06-21 14:01:07

請教SRIO通信問題,6672和FPGA的SRIO通信,2個lane連接,現象如下:

?(1)兩端都配置成2x,3.125G,FPGA顯示port initial成功,link initial失敗。

(2)把6672配置成2個1x,FPGA顯示初始化成功,但無法進行數據通信。

請教是什么問題,謝謝。

2018-06-21 13:52:27

請問,6678SRIO自帶的loopback例程怎么把內循環改為外循環?除了要把loopback模式設為normal模式外還要怎么改?

2018-06-21 17:47:11

1、SRIO門鈴中斷的相關寄存器DOORBELL[0-3]_ICSR/ICCR/ICRR,其中的0-3是不是與port對應?

2、通過ICRR配置doorbell到INTDST的映射時,發現

2018-06-21 02:35:54

徑:D:\ti\pdk_C6678_1_1_2_5\packages\ti\csl\docs\doxygen\html\csl__srio_aux_8h.html查看相關函數定義和功能鏈接速率配置

2020-09-23 11:08:36

徑:D:\ti\pdk_C6678_1_1_2_5\packages\ti\csl\docs\doxygen\html\csl__srio_aux_8h.html查看相關函數定義和功能鏈接速率配置

2020-09-08 10:36:41

我們有一塊帶有 MPC8640D PowerPC 架構處理器的定制板。一個 sRIO 開關連接到這個處理器。在加載我們的自定義 Linux 映像時,我們無法初始化 sRIO,并且出現分段錯誤。 附上日志文件供您參考。請找到突出顯示的 sRIO init 失敗部分請幫我解決這個問題

2023-04-18 07:00:39

保存在資料盤中的Demo\\DSP\\XQ_SRIO_x4LANE_5Gbps文件夾下。1.1.2功能簡介實現DSP與ZYNQ之間SRIO接口傳輸功能。DSP與ZYNQ之間SRIO通道寬度為4,每個

2023-02-21 14:51:50

在資料盤中的Demo\DSP\XQ_SRIO_x4LANE_5Gbps文件夾下。1.1.2 功能簡介實現DSP與ZYNQ之間SRIO接口傳輸功能。DSP與ZYNQ之間SRIO通道寬度為4,每個SRIO

2023-02-02 21:43:20

我想把c6455 srio配置為1P4X的模式,是不是這種模式下只使用一個port,那么我在設置寄存器SERDES_CFGRXn_CNTL和SERDES_CFGTXn_CNTL的時候,只使能

2019-01-21 15:42:20

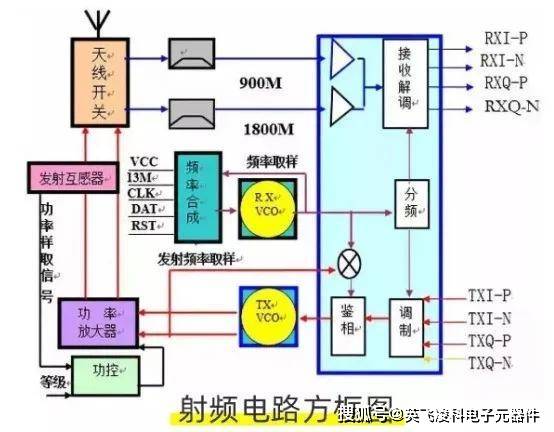

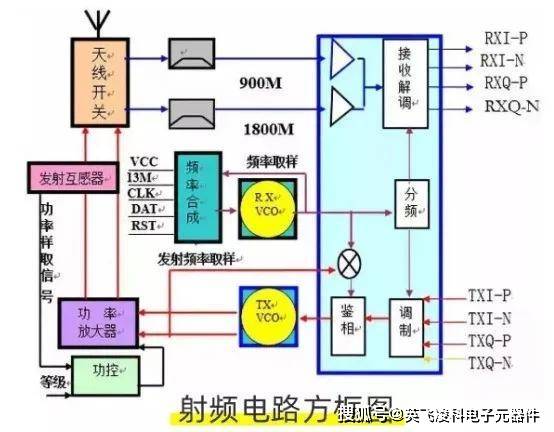

的系帶信號,或對接收到的系帶信號進行解碼.發射時,將音頻信號編譯成基帶碼,發射基帶碼;接收時,將收到的基帶碼進行解碼,轉換為音頻信號,即電話通話功能.同時也負責地址信息(手機號,網站地址),文字信息(短信,網站文字),圖片信息的編解...

2021-07-28 06:42:24

您好,我對“基帶”的定義有一些疑問。我現在通過從設計指南中選擇設計,在ADS2011中使用負載牽引仿真。在一個音調和兩個音源/負載牽引仿真中,參數“Z_Src_Baseband”或

2019-08-06 14:46:43

物理層標準IEEE 802.11a為實例,研究如何在FPGA上實現一個OFDM通信系統的基帶收發機。《基于XILINX FPGA的OFDM通信系統基帶設計》在系統地給出了收發機模塊劃分的基礎上,對每個

2012-11-02 11:09:37

電路功能與優勢該電路是靈活的頻率捷變中頻至基帶接收機。中頻和基帶上的可變增益用于調整信號電平。 ADRF6510 基帶ADC驅動器還包括可編程低通濾波器,可消除通道外阻塞和噪聲。 此濾波器的帶寬

2019-07-05 07:27:55

Spartan6 SRIO,clk pad是浮動的,有沒有辦法使用SRIO

2019-08-01 08:59:05

挑戰。這些收發器可為模擬RF信號鏈提供數字接口,允許輕松集成到ASIC或FPGA,進行基帶處理。基帶處理器(BBP)允許在終端應用和收發器設備之間的數字域中處理用戶數據。

2019-09-19 06:20:59

你好,我想請教一個問題,就是我用6474 SRIO,每次發送完一個4Kbyte包后,我需要SRIO響應一個中斷。而不是像例程這樣:/* Wait for the completion

2018-06-21 14:20:09

您好!

? ? ? 兩塊6678DSP通過SRIO建立連接,對于SRIO來說:

? ? ?1.這兩塊DSP的地址是怎樣映射的?

? ? ? 2.映射是怎樣建立的?

? ? ?3. 雙方的設備ID有沒有參與到映射中來?

? ? ?4.選擇的輸出端口號決定了什么?

2018-06-21 09:37:38

目前在調試多片6678與fpga通過cps1848交換芯片通信,使用的是論壇中keystone_srio例程調試過程中有幾個問題。1.dap向dpga發數時而成功時而失敗,失敗時查看error

2019-06-04 11:03:34

現在使用的是官方提供的:K1_STK_v1.1下SRIO驅動,用于測試SRIO通信。對原代碼SRIO_Loopback_Mode loopback_mode= SRIO_NO_LOOPBACK;流程

2018-08-03 06:19:00

你好!我現在嘗試實現FPGA通過SRIO接口向DSP TMS320C6670發送數據,代碼基于CCS5.0下的SRIO_Loopbacktestproject,但發現在sriodevice_init

2018-08-06 06:38:43

基于IQ解調器,具有中頻和基帶可變增益以及可編程基帶濾波功能的中頻至基帶接收機。

2021-05-24 07:00:30

建立標準模板的目的是什么呢?單片機標準模板建立的操作步驟有哪些?

2022-01-21 07:50:42

如何建立一個基于STM32標準庫的工程模板?

2021-11-26 06:28:02

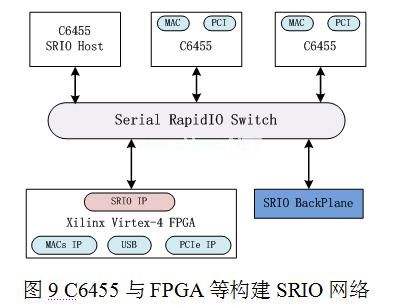

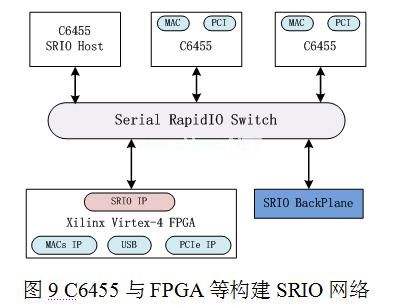

C6455特性是什么?SRIO標準有哪些?如何去實現C6455間的SRIO通信?

2021-06-02 07:12:34

您好,我最近在看C6474的SRIO。

目前手頭只有TI官方的C6474的SRIO的資料《TMS320C6474 DSP?Serial RapidIO (SRIO)?User's Guide》。但是發現該文檔讀不懂。

請問學習SRIO有哪些好的資料?有視頻資料或者中文資料嗎?非常感謝您的指導

2018-06-21 02:35:00

集成了音頻功率放大器。 此外,展訊通信MAX3232EUE+T還為三星GALAXY S III、GALAXY Note和GALAXY Note II提供基帶芯片,支持TD-SCDMA 3G標準。以上

2012-11-09 15:43:30

嗨,我正在使用帶有AWGN注入的Agilent N5182A MXG信號發生器,由matlab通過lan連接控制。我想使用C / N噪聲模式。因為我使用多個基帶發生器同步功能,我無法使用觸發類型為

2019-03-22 07:31:28

本文將從幾種無線通信系統對終端基帶芯片的需求開始討論,介紹一種由簡約納電子公司設計完成的適用于2G/3G/4G的軟件無線終端基帶芯片平臺。

2021-04-19 08:07:18

您好!我在看論壇下載的K2_STK_DSP_v1.1.zip中的SRIO部分的代碼,其中 SRIO_Interrupts.c中的函數 interrupt void SRIO

2018-08-03 06:27:02

本帖最后由 一只耳朵怪 于 2018-6-19 15:13 編輯

最近發現論壇上好多SRIO的帖子,剛好應客戶需求我總結了一些SRIO的東西,在這里也分享出來,作為拋磚引玉吧。首先坦白來說我

2018-06-19 04:30:00

本帖最后由 一只耳朵怪 于 2018-6-19 15:39 編輯

因為項目需求,一片C6670需要連接到兩片FPGA,但是又覺得沒必要使用SRIO SWITCH。所以我的問題是:C6670

2018-06-19 00:53:24

?SRIO_2DSP_Test()中的Keystone_SRIO_match_ACK_ID()是用來檢測相應port的鏈路是否建立成功,函數參數DSP1_SRIO

2018-06-19 00:53:06

你好我對DSP和SRIO之間的通信感興趣。有人知道virtex-6 FPGA是否有srio引腳,以及如何配置?

2020-06-14 14:22:51

本帖最后由 一只耳朵怪 于 2018-6-19 15:35 編輯

不管用CCS 提供的PDK例子,還是論壇上提供的SRIO例子,得出的結果相同:SRIO external loopback

2018-06-19 06:26:42

本帖最后由 一只耳朵怪 于 2018-6-20 11:00 編輯

在K1_STK_v1.1開發包的srio工程內函數SRIO_PktDM_init內對srio內的PKTDMA

2018-06-20 05:21:38

本帖最后由 一只耳朵怪 于 2018-6-19 10:45 編輯

我用的硬件是TMDSEVM6678LE評估版,CCS5.2,pdk_C6678_1_1_2_5。我想將測試SRIO內環的工程

2018-06-19 04:22:50

Hi,Ti guys,我在使用自己板上的c6678,利用論壇上keystone_srio程序調試dsp和fpga端的通信。同事從fpga(v6,srio核)看來收發地址都是34衛的,但我調DSP互聯

2018-12-28 11:08:14

可編程基帶濾波器用于軟件定義的 UHF RFID 閱讀器

2019-08-01 12:35:31

基于TMS320C6455的高速SRIO接口設計

引 言

數字信號處理技術已廣泛應用于通信、雷達、聲納、遙感、圖形圖像處理和語音處理等領

2010-02-24 16:58:35 1641

1641

基帶傳輸,基帶傳輸是什么意思

數字信號可以直接采用基帶傳輸,所謂基帶就是指基本頻帶。基帶傳輸就是在線路中直接傳送數字信號的電脈沖,這是

2010-03-18 14:36:00 10901

10901 基帶網 | ~窄帶網),基帶網(窄帶網)是什么意思

網絡從信息傳輸帶寬或傳輸介質來分:基帶網、寬帶網。

2010-03-20 13:58:19 1300

1300 基帶網絡,基帶網絡是什么意思

計算機網絡按照信號頻帶占用的方式可分為基帶網和寬帶網。

未經調制的原

2010-03-20 14:02:21 3798

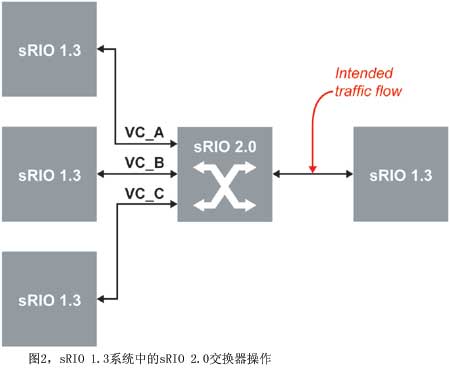

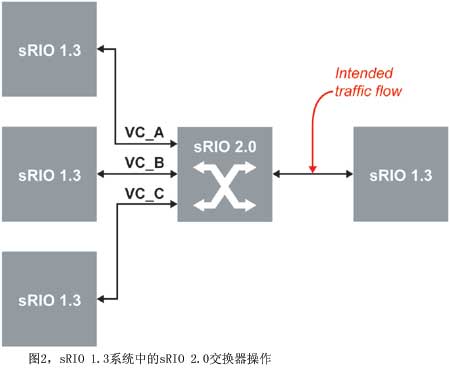

3798 sRIO 2.0中虛擬通道的優勢和加速其采用的技術

Serial RapidIO(sRIO)是一種高性能、基于包的技術,可以用于越來越多的應用,包括無線基礎設施、存儲、醫學

2010-01-12 10:20:26 1525

1525

CEVA公司宣布,中國合肥東芯通信股份有限公司(Xincomm Communications,簡稱東芯通信)已獲授權使用CEVA-X DSP內核用于其下一代TDD/FDD-LTE UE基帶SoC產品設計

2011-03-25 09:20:45 795

795 本文介紹了這種基于SRIO互聯技術的高速實時數據處理硬件平臺,并在該平臺上研究了多DSP之間、DSP與FPGA之間的SRIO通信技術。

2012-01-10 15:07:55 3561

3561

本內容介紹了手機基帶相關內容,手機基帶是什么,手機基帶版本等

2012-05-24 14:48:32 5527

5527 電路功能與優勢 該電路是靈活的頻率捷變中頻至基帶接收機。中頻和基帶上的可變增益用于調整信號電平。 ADRF6510 基帶ADC驅動器還包括可編程低通濾波器,可消除通道外阻塞和噪聲。 此濾波器的帶寬

2017-11-24 10:48:14 561

561

為了滿足2ynq-7000系列芯片的SRIO數據傳輸要求,提出了一種基于FPGA控制DMA傳輸進行SRIO通信的設計方案,并完成了ARM與FPGA核間高吞吐率的數據交互操作。系統的FPGA部分主要

2017-12-21 11:37:03 30

30 本文件描述串行RapidIO?(srio)the on the tms320c6474外圍設備。

2018-04-16 16:49:07 10

10 SRIO是面向嵌入式系統開發提出的高可靠、高性能、基于包交換的新一代高速互聯技術,已于2004年被國際標準化組織(ISO)和國際電工協會(IEC)批準為ISO/IECDIS 18372標準。SRIO則是面向串行背板、DSP和相關串行數據平面連接應用的串行RapidIO接口。

2020-06-17 11:48:12 2555

2555 本文為您分享基于C66x+FPGA的SRIO開發視頻教程,適用于創龍TMS320C6678、TMS320C665x、Kintex-7、Artix-7平臺。

2020-07-01 10:47:39 1760

1760 CN0320:基于IQ解調器,具有中頻和基帶可變增益以及可編程基帶濾波功能的中頻至基帶接收機

2021-03-18 23:25:41 0

0 對SRIO網絡中的節點進行枚舉并建立網絡拓撲信息,以路由跳數定義路由的成本,根據改進 Floyd- Marshal算法計算并保存交換節點間的K最短路徑。給岀預期負載的概念和鏈路上的路由路徑數量來定義鏈路的負載,采用負載均衡算法從K最短路徑中進行選路,建

2021-05-11 14:47:51 9

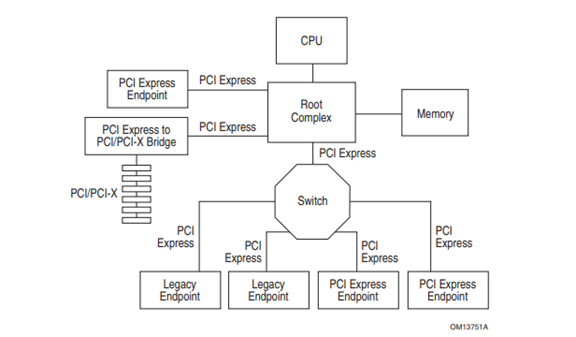

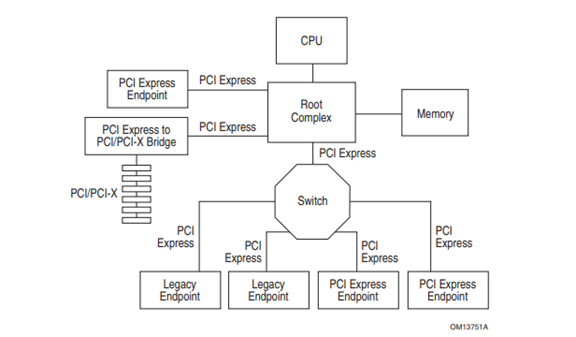

9 隨著PCIe接口、以太網接口的飛速發展,以及SOC芯片的層出不窮,芯片間的數據交互帶寬大大提升并且正在向片內交互轉變;SRIO接口的應用市場在縮小,但是由于DSP和PowerPC中集成了SRIO接口,因此在使用DSP/Power PC + FPGA的使用場景中仍然占有一席之地。

2022-08-02 10:00:26 3111

3111

基帶單元 (BBU) 是電信網絡中處理基帶信號的設備。BBU 充當基站的集中“樞紐”,處理上行鏈路和下行鏈路數據流量,并通過光纖控制 RRU(遠程無線電單元)功能。

2022-09-01 18:13:48 10683

10683 目前具備SRIO接口的硬件不多,推薦廣州星嵌電子科技有限公司開發的DSP+FPGA+RAM開發板XQ6657Z35-EVM。

2022-11-08 17:22:21 742

742

使用于STM32(符合IEC 61508標準)的X-CUBE-STL功能安全包適應其他安全標準

2022-11-21 17:06:43 2

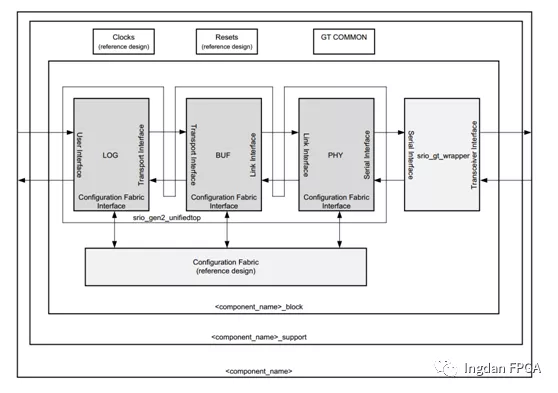

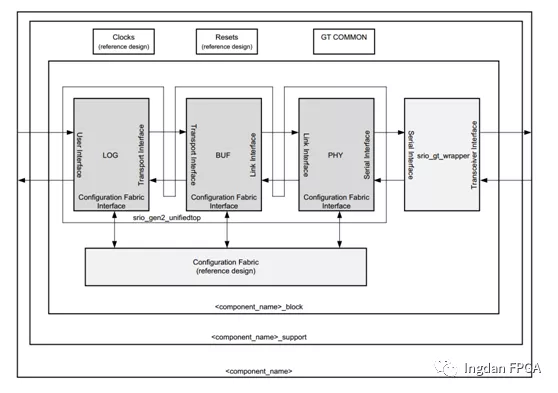

2 數據從遠程設備(假設為DSP的SRIO端)傳輸過來,FPGA端(假設我們這端為FPGA的SRIO端口)通過RX接收到串行數據,先到達物理層進行時鐘恢復,串并轉換,之后進行8b/10b解碼操作、CRC校驗,這一系列的操作都在物理層完成,之后進入傳輸層

2023-03-03 10:19:53 725

725 摘要: 現代 信號 處理系統通常需要在不同處理器之間實現高速數據 通信 ,SRIO協議由于高效率、低延時的特性被廣泛使用。本文研究了在 FPGA 和 DSP 兩種處理器之間實現SRIO協議的方法

2023-03-20 15:00:01 1324

1324 SRIO這種高速串口復雜就復雜在它的協議上,三層協議:邏輯層,傳輸層以及物理層。

數據手冊會說這三層協議是干什么的呢?也就是分工(【FPGA】SRIO IP核系統總覽以及端口介紹(一)(User Interfaces 之 I/O Port))

2023-04-25 11:20:55 1176

1176

本文介紹一個FPGA常用模塊:SRIO(Serial RapidIO)。SRIO協議是一種高速串行通信協議,在我參與的項目中主要是用于FPGA和DSP之間的高速通信。有關SRIO協議的詳細介紹網上有很多,本文主要簡單介紹一下SRIO IP核的使用和本工程的源代碼結構。

2023-09-04 18:19:18 683

683

電子發燒友網站提供《奈奎斯特準則如何運用于基帶采樣、欠采樣和過采樣應用.pdf》資料免費下載

2023-11-28 09:25:33 0

0 在于定義、功能的不同。射頻芯片是指用于實現無線通訊收發功能的芯片。它可以將模擬信號轉換成數字信號,并進行調制、解調等操作,在無線通訊中發揮著非常重要的作用。基帶芯片是指完成基礎處理功能的芯片,比如數字信號處理、調制解調等功能,但不包含射頻信號的處理。

2024-01-06 16:16:17 1506

1506

SRIO(Serial RapidIO)交換芯片是一種高性能的通信芯片,專門設計用于實現基于SRIO協議的數據交換和傳輸。SRIO是一種點對點串行通信協議,廣泛應用于嵌入式系統、高性能計算、網絡通信

2024-03-16 16:40:42 1567

1567 SRIO(Serial RapidIO)交換芯片是一種基于RapidIO(快速輸入輸出)技術的高速網絡通信芯片。RapidIO是一種高性能、低延遲的網絡通信標準,專為嵌入式系統設計,廣泛應用于通信基礎設施、軍事和航空、工業自動化以及汽車等領域。

2024-03-21 16:30:37 72

72 SRIO交換芯片屬于高速網絡通信芯片的一種,具體來說,它們是基于RapidIO(快速輸入輸出)技術的串行通信芯片。RapidIO是一種用于高性能嵌入式系統的互連技術,它支持多種通信協議和拓撲結構,適用于需要高速、低延遲通信的應用場景。

2024-03-21 16:33:20 98

98

電子發燒友App

電子發燒友App

評論