??? 關(guān)鍵詞:嵌入式系統(tǒng),MPC850,硬件開發(fā)平臺

1 MPC850簡介

Motorola公司的MPC850通信控制器芯片基于PowerPC內(nèi)核,以精簡指令集計算RISC的體系結(jié)構(gòu)為基礎(chǔ),集成了32位微處理器和多種外設(shè)接口,具有強大的通信和網(wǎng)絡(luò)協(xié)議處理能力,可廣泛應(yīng)用于各種通信和網(wǎng)絡(luò)產(chǎn)品,如ADSL modem、SOHO路由器、低速ISDN、T1/E1終端、ATM線卡控制、局端交換、無線接入等。

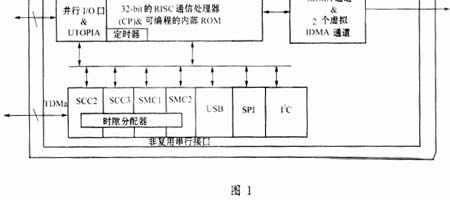

MPC850的功能結(jié)構(gòu)主要包括:嵌入式PowerPC內(nèi)核,系統(tǒng)接口單元(System InterfaceUnit,SIU)和通信處理器模塊(Communications Processor Module,CPM)。其體系結(jié)構(gòu)的框圖如圖1所示。

從圖中可以看出,通信處理器模塊CPM支持7個串行信道,包括:2個串行通信控制器SCC,2個串行管理控制器SMC,1個USB接口,1個I2C和1個串行外設(shè)接口SPI。因此,MPC850通過靈活的編程方式可實現(xiàn)對Ethernet、USB、T1/E1等的支持,以及對IEEE802.3/Ethern-et、UART(同步/異步)、HDLC、Transparent、App-leTalk、IrDA等多種通信模式/協(xié)議的支持。

另外,MPC850還具有增強型在片仿真調(diào)試功能,功能齊全的接口單元,可進行優(yōu)先級編程的中斷控制等特征。本系統(tǒng)正是基于MPC850的這些特點來進行通信開發(fā)平臺的硬件設(shè)計的。

2 系統(tǒng)硬件總體設(shè)計

設(shè)計MPC850多功能通信開發(fā)平臺的底層,在硬件方面需要提供全面的通信接口、足夠的內(nèi)存容量、調(diào)試功能以及測試顯示功能。根據(jù)設(shè)計,本系統(tǒng)主要由CPU、存儲器、通信接口、調(diào)試以及測試顯示等幾部分組成。

CPU部分的設(shè)計包括了系統(tǒng)的硬件啟動與復(fù)位、MPC850總線信號分配與定義等。存儲器部分包括SDRAM、FLASH ROM和E2PROM。通信接口部分提供了2個Ethernet接口、2個RS232接口、1個RS485接口、1個USB接口、ISDN用戶開發(fā)板接口以及ATM UTOPIA接口。另外,還提供了MPC850 BDM調(diào)試口以及測試口、LED顯示等。

3 系統(tǒng)的硬件啟動與復(fù)位

MPC850的復(fù)位方式包括:上電復(fù)位、外部/內(nèi)部Hard Reset、外部/內(nèi)部Soft Reset、調(diào)試口的Hard Reset等。這些方式都由Reset控制器處理。本系統(tǒng)采用了上電復(fù)位和外部Hard Reset的方式。

上電復(fù)位的過程由芯片內(nèi)部完成,MPC850需要確認

MPC850在從數(shù)據(jù)總線上采樣硬件復(fù)位配置字信息的過程中,

4 存儲器設(shè)計

MPC850中存儲器管理器負責控制管理GPCM和UPMs兩種存儲器控制機制,針對不同的存儲器提供靈活的時序支持和無縫連接。其中,GPCM提供了一種簡單的、不支持突發(fā)方式的低層次的存儲器資源和內(nèi)存映射接口,因此,GPCM控制的內(nèi)存槽主要用于系統(tǒng)的啟動和不支持突發(fā)方式的數(shù)據(jù)存取。而UPM方式支持突發(fā)方式,同時包括外部總線的地址復(fù)用、周期定時以及DRAM器件可編程的行列地址選通信號的產(chǎn)生,因此,UPM多用于支持高性能的實時存儲器。

在本系統(tǒng)的存儲器設(shè)計中,采用了1片Intel公司的FLASH ROM 28F320J5,2片SAMSUNG公司的SDRAM K4S281632B。其中,BANK0用于FLASH ROM,對應(yīng)于

FLASH ROM的容量設(shè)計為32Mbit,用來存放實時操作系統(tǒng)和用戶應(yīng)用程序。對BYTE#(ByteEnable)管腳的設(shè)置,可以使28F320J5工作在×8或×16模式。

SDRAM的讀寫以及突發(fā)模式的時序控制通過對MPC850

MPC850

5 各種通信接口的硬件設(shè)計

CPM通過以下途徑減少core的計算任務(wù),包括:減少中斷產(chǎn)生率;執(zhí)行一些OSI第2層處理;支持多緩存存儲器數(shù)據(jù)結(jié)構(gòu)等。

在CPM功能基礎(chǔ)上,外圍通信電路只需提供物理層收發(fā)器和驅(qū)動器。在本系統(tǒng)的設(shè)計中,Ethernet收發(fā)器采用Intel Level One公司的LXT905,RS232與RS485收發(fā)器分別采用MAXIM公司的MAX232與MAX488,USB收發(fā)器采用Philips公司的PDIUSBP11A。其中,2個Ethernet收發(fā)器分別使用與MPC850的SCC2、SCC3兩個串行通信控制器接口,2個RS232收發(fā)器分別使用與MPC850的SMC1、SMC2兩個串行管理控制器接口,RS485復(fù)用了SMC2接口,USB收發(fā)器使用與MPC850的USB接口。

由于LXT905本身提供了與MPC850的無縫接口能力,于是通過RJ45實現(xiàn)與外界的通信主要集中在協(xié)議的實現(xiàn)和數(shù)據(jù)收發(fā)的控制上。其數(shù)據(jù)接口信號包括:

·RCLK與TCLK:接收與發(fā)送時鐘信號。由LXT905提供,連接到MPC850的時鐘信號CLKx。

????? ·RXD與TXD:接收與發(fā)送數(shù)據(jù)信號。由MPC850提供,連接到LXT905的RXD與TXD。

·TEN:發(fā)送使能信號,同時啟動LXT905看門狗定時器。

·CD:載波監(jiān)聽信號,監(jiān)聽LAN是否正在使用。

·COL:沖突監(jiān)測信號,驅(qū)動控制器的沖突監(jiān)測輸入。

??? 本系統(tǒng)設(shè)計的ISDN端口總線使用了MPC850串行接口TDMa和SPI接口,用戶可以在此基礎(chǔ)上設(shè)計開發(fā)自己的ISDN接入系統(tǒng)。其中,SPI接口提供了SPII/O數(shù)據(jù)信號SPIMOSI與SPIMISO、SPI時鐘信號SPICLK、SPI從設(shè)備選擇信號;TDMa接口提供的信號包括收發(fā)數(shù)據(jù)、時鐘、同步等。

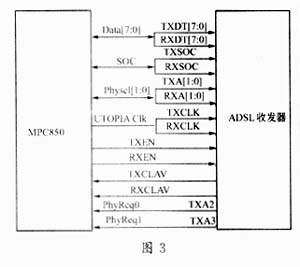

MPC850的ATM控制器支持兩種接口模式:UTOPIA接口和串行ATM接口。本系統(tǒng)以支持ADSL收發(fā)器為目的,采用了目前ADSL收發(fā)器通常使用的ATM UTOPIA LEVEL1/LEVEL2接口。這種接口允許不同速率和性能的傳輸媒質(zhì)以一種統(tǒng)一的物理層接口到ATM子系統(tǒng)中,并且有利于向支持多用戶的ADSL局端設(shè)備擴展。

一個UTOPIA接口包括收發(fā)數(shù)據(jù)端口、控制信號和地址信號。UTOPIALEVEL1和LEVEL2主要在地址信號的定義上有所不同。其中LEVEL1未定義地址信號,主要針對single-PHY的情況;LEVEL2針對multi-PHY的情況,比LEVEL1多了兩組地址信號。MPC850的UTOPIA接口支持LEVEL 1標準,加上外部控制邏輯即可實現(xiàn)LEVEL2的multi-PHY接口(最多支持4個物理層設(shè)備),因此,本系統(tǒng)的設(shè)計實現(xiàn)了兼容UTOPIALEVEL1/LEVEL2的接口電路,如圖3所示。關(guān)于調(diào)試與測試部分的敘述這里從略。

MPC850的多功能通信開發(fā)平臺在底層設(shè)計的基礎(chǔ)上,選擇相應(yīng)的嵌入式操作系統(tǒng),再進行相關(guān)驅(qū)動程序和上層應(yīng)用程序的開發(fā),通過所需接口與用戶各自的開發(fā)系統(tǒng)相連,最終可設(shè)計實現(xiàn)各種通信與網(wǎng)絡(luò)產(chǎn)品。

參考文獻

2 Wayne Wolf.嵌入式計算機系統(tǒng)設(shè)計原理.北京:機械工業(yè)出版社,2002,2

電子發(fā)燒友App

電子發(fā)燒友App

評論