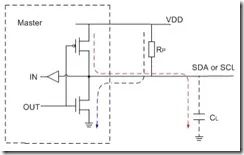

器件都有一個唯一的識別地址,而且都可以作為一個發送器或接收器。當連接在I2C總線上的多個主機器件同時傳輸數據時,通過仲裁來避免沖突。SDA和SCL都是雙向線路,通過一個電流源或上拉電阻連接到電源。器件輸出級必須是漏極開路或集電極開路,當總線空閑時,兩條線路處于高電平,執行線與的功能。

2019-08-05 06:33:00

接口可編程時鐘來實現傳輸速率的調整,同時也跟所接的上拉電阻的阻值有關。 I2C總線上的主設備與從設備之間以字節(8位)為單位進行雙向的數據傳輸。3I2C總線協議 I2C協議規定,總線上數據的傳輸必須以一

2019-08-01 16:12:45

本帖最后由 eehome 于 2013-1-5 09:56 編輯

現在設計有兩個設備,主設備和從設備,通過I2C接口控制連接,由于距離可能距離較遠50cm左右,請問這距離有問題嗎?還有沒有對I2C中繼一下?(這接口總體已經定死了,就用I2C接口通信)謝謝了!

2012-11-08 09:34:28

我發誓我再也不能忍受了。我就是不能讓I2C工作!真是幾個月了我不是故意說PIC的壞話,因為我喜歡他們,但AVR和PSOC只是工作。我試過代碼配置器,我嘗試過互聯網上可以嘗試的每一段代碼。我試著編寫我

2019-09-29 07:34:13

、I2C設計數學:電容和電阻了解I 2 C及其隨之而來的一些設計挑戰,包括邏輯閾值,影響電容的因素以及最小和最大上拉電阻。本文介紹了哪些變量會影響總線的電容。它還考察了用于確定上拉電阻器尺寸并確定電路

2020-09-22 09:31:41

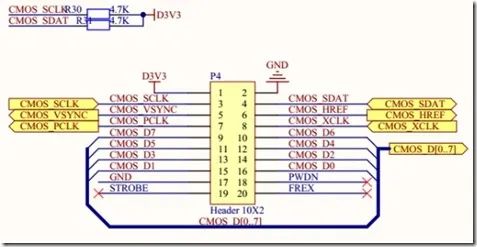

如圖,像這種IIC的電路為什么要加這些4.7kΩ、100Ω的上拉電阻?

2019-02-15 09:58:53

I2C信號一般需要外接上拉電阻,如果主控內部有上拉電阻,是否可以省略外部上拉?這個是否需要上拉根據什么來決定?是根據從器件的輸入電流來決定的嗎?芯片的輸入電流參數(Ii 即input current)怎么理解,設計電路時針對這個參數需要注意什么?

2018-06-07 10:01:00

。I2C的兩根線SDA(串行數據線)和SCL(串行時鐘線)都是雙向I/O線,接口電路為開漏輸出,需通過上拉電阻

2022-01-20 08:04:17

在設計時對產品進行靜電干擾測試時,出現I2C的CLK被異常拉低,接上位機讀取I2C狀態寄存器,發現寄存器值有變化,這種問題如何解?

2020-02-07 15:23:49

上周翻了下AT24CM02芯片的數據手冊,里面提到了I2C上拉電阻的設計要點,只有兩個公式就簡潔地把上拉電阻阻值范圍確定了,非常實用,詳細見圖1。實際上,以前我從來沒有注意過I2C上拉電阻設計,總是

2022-11-29 08:00:00

NXP的母公司)在80年代開發,用于主板、嵌入式系統連接周邊低速設備。I2C由兩條雙向開漏線組成,這是一個很大的優勢,接線簡單。兩條線利用上拉電阻將電位上拉。典型電位為+3.3V或+5V。標準傳輸速率為

2020-08-25 11:16:05

SDA,另外一根時鐘線SCL,接上拉電阻,總線空閑為高電平。只要有低電平,總線就會被拉低電平。主機通過I2C總線來傳輸數據給掛載的器件。通過總線仲裁,來判斷哪一臺主機來控制。SCL...

2022-01-18 07:36:05

數據線,為OD門,與其它任意數量的OD與OC門成\線與\關系。I2C總線通過上拉電阻接正電源。當總線空閑時,兩根線均為高電平(SDL=1;SCL=1)。連到總線上的任一器件輸出的低電平,都將使總線的信號變低,即各器件的SDA及SCL都是線“與”關系。二、協議1.空閑狀態 I2C總線總線的SDA和SCL

2022-01-19 08:05:15

1、I2C總線簡介I2C是兩線式串行總線,用于連接微控制器及其外圍設備。I2C總線最主要的優點是其簡單性和有效性。由于接口直接在組件之上,因此I2C總線占用的空間非常小,減少了電路板的空間和芯片管腳

2021-08-20 08:25:23

要,這樣你在選擇組件或接口時就可以做出明智的決定。本文是關于I 2 C的,它通常用于位于同一PCB上的各個集成電路之間的通信。同樣適用于此通用類別的另外兩個常見協議是UART(通用異步接收器/發送器

2020-09-06 10:16:10

在硬件上,I2C 總線是由時鐘總線 SCL 和數據總線 SDA 兩條線構成,連接到總線上的所有器件的 SCL 都連到一起,所有 SDA 都連到一起。I2C 總線是開漏引腳并聯的結構,因此我們外部要

2022-01-07 06:03:45

慢于從高到低的過渡,從而產生經典的I2C“鋸齒”波形:這兩個示波器捕獲顯示了具有1kΩ上拉電阻和最小電容(總線上只有兩個器件,且PCB走線短)的I2C時鐘信號的從低到高和從高到低的跳變。上拉電阻的尺寸

2020-09-20 08:37:42

系列索引:《嵌入式系統原理與應用》 | 嵌入式系統 重點知識梳理目錄I2C的物理層接口(電平特性)及互聯I2C、SPI及UART三者之間的對比I2C中的主從機、收發器的概念I2C中的起始條件、停止

2021-12-20 07:38:09

的外部收發設備,現在被廣泛地使用在系統內多個集成電路(IC)間的通訊。I2C是半雙工通信I2C只有兩根雙向通信線: 一根是時鐘線SCL, 一根是數據線SDAI2C總線通過上拉電阻接電源,當總線空閑的時候,兩根線均為高電平。各器件之間的SCL與SDA 都是 “線與” 關系二、I2C的時序1、數

2021-08-20 06:58:20

一.I2C 簡介I2C(內部集成電路)總線接口用作微控制器和 I2C 串行總線之間的接口。它提供多主模式功能,可以控制所有 I2C 總線特定的序列、協議、仲裁和時序。它支持標準和快速模式。它還

2021-08-10 08:10:24

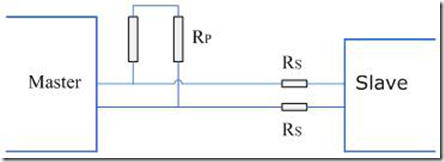

................................................................... 3016.1 標準模式I2C 總線器件電阻Rp 和RS 的最大和最小值

2009-04-09 18:34:35

V和V 邏輯高 = 1.2 V 的任意值,并假設總線電容為150 pF,我們具有以下幾點:摘要I2C上拉電阻的值必須足夠大以減少不必要的電流消耗,并且必須足夠小以產生可接受的上升時間。本文介紹的計算

2020-09-21 09:00:00

的設備都有一個獨立的地址,主機利用地址進行不同設備的訪問多個主機同時使用總線時,為防止數據沖突會通過仲裁的方式決定哪個設備占用總線具有三種傳輸模式:標準模式(100k/s)、快速模式(400k/s)、高速模式(3.4M/s)總線通過上拉電阻接到電源,當I2C設備空閑時輸出高阻態,當所有設備都空閑

2022-01-13 07:20:43

我的I2C通信需要被拉到3.3V,但是我不知道我應該使用什么尺寸的上拉電阻。我讀過的其他論壇的帖子,建議2.7k歐姆或4.7K歐姆,但這似乎只是讓高可以在3.3V和是在3.0V低。這是正常的嗎?我用

2019-04-03 15:13:49

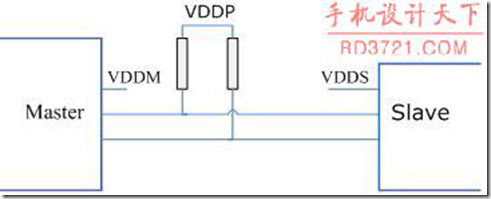

一 、I2C物理層I2C 通訊設備之間的常用連接方式見圖:有以下特點:(參考數據手冊:上拉電阻一般4.7k~10k ,一般4.7k)(1)由兩條總線控制:一條雙向串行數據線(SDA) ,一條串行

2021-08-03 07:43:57

是FPGA生成的數據信號在約束.ucf文件中,無論我將sda位設置為i2c還是上拉它,都沒有變化。在硬件設備中,i2c總線直接連接到FPGA的引腳。根據傳感器數據表,SDATA通過1.5kΩ電阻上拉至VDD

2019-07-01 09:15:23

................................................................... 3016.1 標準模式I2C 總線器件電阻Rp 和RS 的最大和最小值

2008-08-13 17:16:42

.有的不可以設罝.有的是內置.有的需要外接.I/O端口的輸出類似與一個三極管的C,當C接通過一個電阻和電源連接在一起的時候,該 電阻成為上C拉電阻,也就是說,如果該端口正常時為高電平,C通過一個電阻

2017-08-28 09:27:18

罝.有的不可以設罝.有的是內置.有的需要外接.I/O端口的輸出類似與一個三極管的C,當C接通過一個電阻和電源連接在一起的時候,該 電阻成為上C拉電阻,也就是說,如果該端口正常時為高電平,C通過一個電阻

2017-11-16 17:14:38

上拉電阻:1、當TTL電路驅動COMS電路時,如果TTL電路輸出的高電平低于COMS電路的最低高電平(一般為3.5V),這時就需要在TTL的輸出端接上拉電阻,以提高輸出高電平的值。2、OC門電路必須

2008-05-22 08:46:35

接口的輸出端是漏極開路或集電極開路,所以必須在接口外接上拉。上拉電阻的取值和I2C總線的頻率有關,工作在standard mode時,其典型值為10K。在FAST mode時,為減少時鐘上升時間,滿足

2018-10-19 16:30:19

,有的是內置,有的是需要外接,I/O端口的輸出類似與一個三極管的C,當C接通過一個電阻和電源連接在一起的時候,該電阻成為上C拉電阻,也就是說,如果該端口正常時為高電平,C通過一個電阻和地連接在一起的時候

2019-06-27 05:55:08

,考慮到這個項目是帶模擬電視芯片的,以前就出現過模擬電視芯片的I2C地址沒有去配,導致出現漏電情況,遂立馬去看是不是這個問題,結果是遺憾的,配了!那再仔細檢查了基帶的GPIO口和其他的I2C,發現都配

2011-12-15 18:34:39

而定! * 一般說的是I/O端口,有的可以設置,有的不可以設置,有的是內置,有的是需要外接,I/O端口的輸出類似與一個三極管的C,當C接通過一個電阻和電源連接在一起的時候,該電阻成為上C拉電阻

2014-05-12 08:24:37

! -------一般說的是I/O端口,有的可以設置,有的不可以設置,有的是內置,有的是需要外接,I/O端口的輸出類似與一個三極管的C,當C接通過一個電阻和電源連接在一起的時候,該電阻成為上C拉電阻

2018-06-28 06:21:54

買了一套ADP1048 interleaving PFC演示實驗板。不小心將高壓引到USB I2C接口模塊上,可以看到模塊里面電路板上C302糊了。用表測量USB 5V對地電阻只有11歐姆。有沒有修復的可能?謝謝!

2024-01-08 08:31:27

大家好,我想在ARDUINO UNO和PSoC 5LP(CY8CITK-059)之間提供一個I2C接口。我在YouTube上完成了I2C課程,我成功地設置了PSoC和橋接控制面板之間的通信。然后,我

2018-08-19 04:51:39

展示I2C接口的完整使用流程。本例擬對Hi3516DV300某開發板上TouchPad設備進行簡單的寄存器讀寫訪問,基本硬件信息如下:SOC:hi3516dv300Touch IC:I2C地址為0x38

2020-09-16 18:54:10

如題!最近設計I2C的時候,考慮上拉電阻的位置有這個疑問

2019-02-19 15:39:49

極開路(Open Drain)并利用電阻將電位上拉,同一個I2C總線上可以掛載多個I2C設備,如下圖所示。圖1 I2C掛載設備示意圖 圖2 I2C時序圖 I2C總線是電平有效,在SCL信號為高電平

2017-10-20 13:20:07

親愛的大家, 我在我的電路板上使用LSM330DLC陀螺儀,我忘記了SPI / I2C選擇引腳上的上拉電阻。但它工作正常。我的問題是我可以在沒有這些上拉電阻的情況下開發我的項目嗎?在數據表中提

2019-05-16 13:50:24

LTC4311 I2C邏輯緩沖器的典型低壓應用電路。利用LTC4311低壓I2C / SMBus加速器,利用低功耗總線加速器提高I2C或SMBU數據速率并降低功耗,LTC4311的強上拉電流允許用戶選擇更大的總線上拉電阻值以降低VOL

2019-06-05 09:06:39

,上拉電阻器的值為4.7k?,不過這個值的范圍可以在少于1k?到10k?之間,取決于所使用的從器件。要獲得正確的上拉電阻值,請參考器件數據表。多個從器件可以共用一條I2C總線,單個上拉電阻器I2C軟件

2018-08-30 15:39:15

大家好。我設計的電路測試/編程設備生產并考慮連接SWD接口和I2C。DUT(測試設備)使用I2C進行所有通信。所以我需要使用I2C從測試主機(PC使用Python)執行測試命令。由于

2018-08-29 14:19:51

正常,I2C寄存器配置如下:IAM有點丟失。我已經嘗試了其他上拉值(1K2,10K,12K)。任何線索!謝謝!! 以上來自于百度翻譯 以下為原文 regards, Iam trying

2019-05-14 11:56:35

我想用STM32F103VET6控制 I2C接口的數字電位器 X9119 。不知道怎么控制,誰可以幫我下。主要是時序我都知道,我也看了野火的I2C的E2PROM的DEMO,我想用DEMO改下 來控制

2014-06-06 21:01:52

我想用STM32F103VET6控制 I2C接口的數字電位器 X9119 。不知道怎么控制,誰可以幫我下。主要是時序我都知道,我也看了野火的I2C的E2PROM的DEMO,我想用DEMO改下 來控制

2014-06-06 21:05:02

;strong>USB總線轉I2C總線接口芯片</strong><br/>USB2I2C是一個USB總線的轉I2C總線的專用接口芯片

2009-12-16 10:39:56

pyboard上面有I2C類庫可以供我們調用,根據邵版主的原話,I2C類庫所掛載的I2C接口是STM32F405RG的硬件I2C接口,非GPIO模擬的I2C接口。硬件連線,DS3231連接

2018-08-17 16:53:24

最近在用stm32f401re做一款熱成像設備需要用到I2C,這里總結一下遇到的坑。一開始調試我用的是開發板飛線接傳感器,SCL SDA加4.7k上拉電阻。使用硬件I2C時讀寫大量數據時經常會遇到

2020-03-05 19:02:15

地址查找從機I2C通常用于連接微控制器及其外圍設備,是微電子通信控制領域廣泛采用的一種總線標準。很多外圍器件采用I2C通訊接口訪問。STM32I2C基礎內容1、STM32 I2C連線它只需2根線連接

2021-06-18 09:27:37

查找從機。因為I2C 通信IO口輸出結構都是配置為漏極開路或集電極開路輸出。所以時鐘線和數據線必須外部都接上拉電阻,當一對多輸出的時候,很多GPIO口會連接在同一根線上,可能會存在某個GPIO輸出高電平

2021-09-07 14:22:56

,快速模式下可達400kbit/s,高速模式下可達3.4Mbit/s。一般通過I2C總線接口可編程時鐘來實現傳輸速率的調整,同時也跟所接的上拉電阻的阻值有關。I2C總線上的主設備與從設備之間以字節(8

2017-07-20 22:29:02

1、I2C上電過程故障,復位后即正常,有可能是什么原因?問:如題:I2C1總線上掛有一片24C02(Addr:0xA0)和另一個I2C總線器件(Addr:0xAC),上電后配置完畢I2C1(庫操作

2014-03-14 09:45:14

導言:最近在使用多個i2c設備時,讀寫出現沖突,我決定使用多個i2c接口,我把攝像頭關閉后,使用3B+上的兩個i2c同時進行讀寫操作,兩個i2c同時讀寫。一、raspi-config配置1.配置

2022-01-05 06:54:16

它輸出高電平時,它就斷路,什么也不輸出,由外接電平決定這個引腳的電平)。如果芯片內部帶有上拉電阻(比如BBB的芯片就自帶上拉電阻),那不外接上拉也可以。BBB系統自帶了一個Linux下的I2C工具

2014-10-22 13:52:44

I2C分為哪幾種模式?I2C的上拉電阻取值是什么?上拉電阻的上限如何確定呢?關于I2C有什么問題嗎?那么一般如何解決呢?

2021-06-27 06:59:35

各位大俠大姐們,下午好!小弟剛接觸I2C方面的知識,想用LABVIEW 來編寫VI來控制I2C工作,有外圍IC(RELAY CARD 之類的)通信的,如何實現,請大俠大姐幫幫忙,如果現成的VI,可以給我一個嗎!!!謝謝拉!!!

2012-03-31 13:17:41

我在設計中使用LSM6DS3組件。我過去曾經使用過這個組件(并且總是喜歡它),但從來沒有使用過這個組件。我正在使用I2C與10k上拉電阻進行通信,并且使用與我的微控制器相比的獨立電源總線來打開/關閉

2019-03-07 15:42:24

。I2C協議實際上設計用于在單個總線上支持多個設備,而如串行外設接口(SPI)的其他協議的設計用于點對點單設備支持。雙線I2C接口還可以幫助簡化對四線SPI接口的布線,并減少通用輸入/輸出(GPIO

2019-07-23 04:45:06

單片機 I2C 時序介紹在硬件上,I2C 總線是由時鐘總線 SCL 和數據總線 SDA 兩條線構成,連接到總線上的所有器件的 SCL 都連到一起,所有 SDA 都連到一起。I2C 總線是開漏引腳并聯

2022-01-07 06:19:47

I2C總線由兩條雙向信號線構成,分別為數據線(SDA)以及時鐘線(SCL),分別用電阻進行上拉,以實現高低電平之間的切換,進行設備之間的數據交交換。I2C允許的工作電壓范圍較為寬泛,典型電壓基準為

2019-03-08 06:45:04

1、硬件I2C&軟件I2C驅動0.91OLED 并行總線至 I2C 總線協議的轉換及接口; 同一接口既可實現主機功能又可實現從機功能; 主從機之間的雙向數據傳輸; 支持 7 位

2022-12-14 16:42:17

摘要本應用筆記以驅動 I2C 接口的 6 軸傳感器 MPU6050 為例,說明了如何使用 I2C 設備驅動接口開發應用程序,并詳細講解了 RT-Thread I2C 設備驅動框架及相關函數。本文

2022-08-18 10:54:29

I2C上拉電阻 在一些PCB的layout中,大家往往會看到在I2C通信的接口處,往往會接入一個4.7K的電阻,有的datasheet上面明確有要求,需要接入,有的則沒有要求。 I2C接口 對于

2022-01-14 07:22:21

CYSTART();I2CysCLSSEDRIVEVMODED(I2CYSCLIL DMYRESIUP);/ /使用內部上拉I2C電阻器I2CysSDAsStudioDrimeMod(I2CsSdAydMyRESIUP);因此,問題是如何在4100系列中做到

2019-10-08 07:43:07

ST2 和 ST4 跳線? 焊接R116和R117上拉電阻? 移除SPI焊橋(R205)? 放置I2C 焊橋(R204) 2) 軟件設置? 在預處理器中設置 RFAL_USE_I2C? 將

2022-12-05 07:13:56

想這在其他地方都有介紹,但我還沒有找到。

可能最簡單的事情是加載一個 I2C 掃描程序,以查看 ESP8266 看到的 OLED 地址。確保 I2C 引腳上有上拉電阻。還要將引腳更改為您的設置。在此

2023-04-26 08:12:24

漏應用來說,時序常數比較大會對I2C總線產生負面影響,從而使其串行數據線(SDA)和串行時鐘線(SCL)達到所需的波特率。從數學上講以下是計算電阻值的方法:Rp(min)為可接受的最小電阻值,由下面

2018-11-30 09:12:02

,上拉電阻器的值為4.7k?,不過這個值的范圍可以在少于1k?到10k?之間,取決于所使用的從器件。要獲得正確的上拉電阻值,請參考器件數據表。多個從器件可以共用一條I2C總線,單個上拉電阻器I2C軟件

2018-06-04 10:43:02

向來實現這一點:如果我們將管腳配置成輸入,那么實際上在管腳輸出上會出現高電平的輸出,因為我們有定義為上拉電阻器的上拉電阻。根據I2c規范,如果我們想把引腳設置為低輸出,我們可以把引腳設置為輸出,寫0,這是

2019-07-26 14:29:14

大家好,我們用i2c來加速這個配置:*分開VDD和VDDIO(這個連接到CS)。* SDA和SCL安裝有10K的外部上拉電阻。* SDO / SA0未連接(應該有內部上拉)。是否有任何上電順序以確保

2019-03-04 11:37:27

開發板I2C連接到RTC(RX8010)芯片,I2C總線上沒有接上拉電阻,LS1012A手冊上說它的I2C是open drain輸出的,為什么沒有上拉電阻? 哪位能幫助解釋一下,謝謝

2022-01-05 06:28:48

使用STM32的GPIO模擬I2C總線時序,GPIO設置為開漏模式,SDA和SCK外部必須使用上拉電阻,一般是4.7K。開漏模式的好處是,可以同時讀取輸入電平,而無需切換輸入/輸出模式。注意事項:在

2022-02-22 06:48:21

成為上拉電阻,也就是說,該端口正常時為高電平;C通過一個電阻和地連接在一起的時候,該電阻稱為下拉電阻。上拉電阻是用來解決總線驅動能力不足時提供電流的問題的。一般說法是上拉增大電流,下拉電阻是用來吸收

2021-08-12 13:35:38

你好,我嘗試用I2C接口與一個傳感器通信,我使用PSoC創建者2中的I2C主控(UDB)組件。復位連接到“0”和SDA,SCL連接到傳感器(從屬)上的上拉電阻。在I2C接口之前,我使用了很多

2019-01-18 12:29:40

SPI是什么?SPI總線有哪些優缺點?I2C接口包括哪些?I2C接口有哪些優缺點?

2021-10-15 09:31:17

一個上拉電阻接到正電源,因此在不使用的時候扔保持高電平。使用 I2C 總線進行通信的設備驅動這兩根線變為低電平,在不使用的時候就讓它們保持高電平。每個連到 I2C 的設備都有一個唯一地址,這個設備可以

2018-11-30 11:50:53

使用的從器件。要獲得正確的上拉電阻值,請參考器件數據表。多個從器件可以共用一條I2C總線,單個上拉電阻器 I2C軟件協議 不論何種應用,每個支持I2C器件都需要遵守針對全部I2C器件所定義的共同

2020-12-14 14:17:25

。但是,I2C總線拓撲要依賴于阻值合適的上拉電阻才能實現穩定可靠的通信。電阻值選擇錯誤不僅會造成電能浪費,還可能導致總線狀態和傳輸過程由于噪聲、溫度變化、工作電壓變化以及器件間的制造差異而出

2012-12-17 11:52:52

請問用TMS320C5515的GPIO口模擬I2C是否需要加上拉電阻?

2018-07-31 07:48:20

換個說法,如何將28335的GPIO設置成開漏輸出呢?之前使用硬件I2C接口,工作正常,但是因為I2C外設管腳和另外一個外設管腳重復了,只能將I2C接口轉移到其它GPIO上,使用軟件模擬。使用軟件

2018-10-08 17:10:19

stm32f051的i2c需要外接上拉電阻嗎,直接用內部上拉行不行,還有庫中的I2C_Init函數中有這么一句/* Enable I2Cx Peripheral */I2Cx->CR1 |= I2C_CR1_PE;為什么初始化有些i2c寄存器需要使能i2c。最后附上波形,希望哪位大哥幫幫忙,看看是什么問題。

2019-03-12 07:14:31

請問為什么有時在I2C中將SDA和SCL 上加各加個上拉電阻呢?

2023-05-08 18:01:37

],上拉 4.7k,3.3V

I2C SCL:P3 [5],上拉 4.7k,3.3V VDD:3.3V

2024-01-22 06:14:17

請問用TMS320C5515的GPIO口模擬I2C總線需要接外部上拉電阻嗎?需要的話阻值為多少比較合適呢?

2019-10-28 09:37:43

軟件I/O模擬I2C總線時序和直接連接CPU固有的I2C接口,在使用上有什么區別,直接用固有的接口,還需要模擬時序嗎?[/mw_shl_code]

2020-06-02 04:35:08

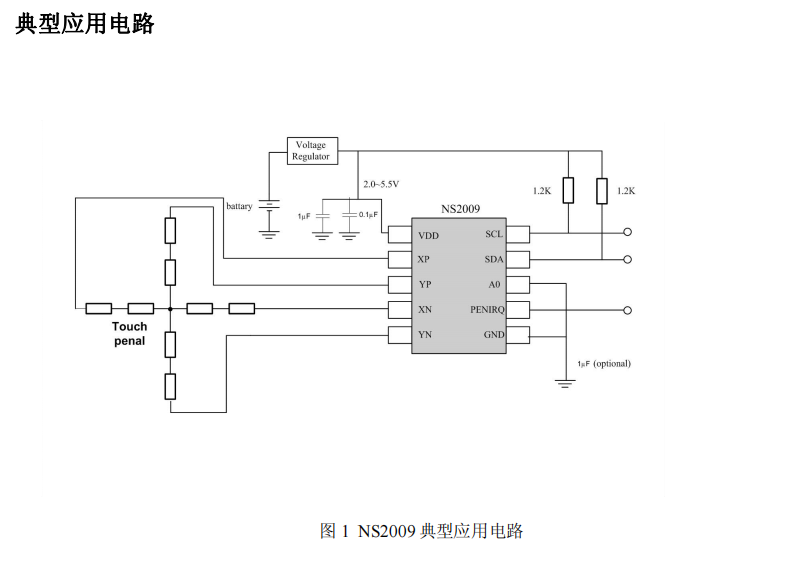

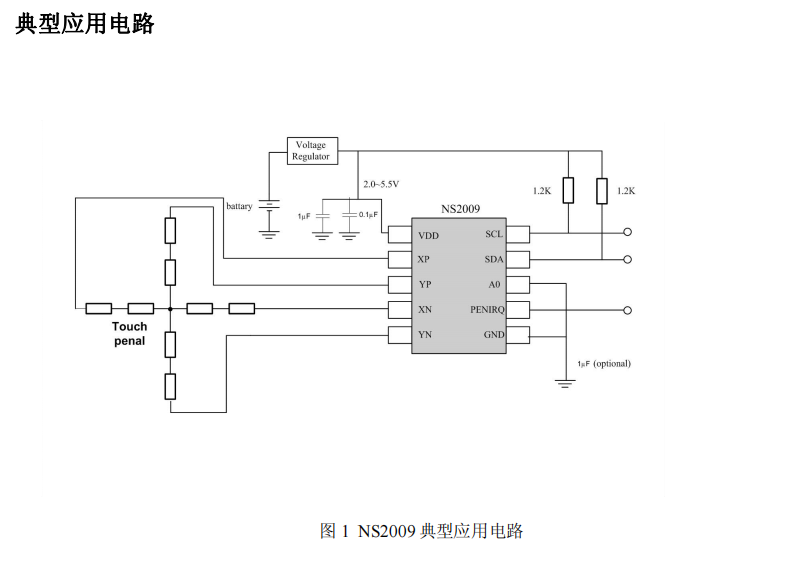

NS2009是一款帶I2C接口的4線制電阻式觸摸屏控制電路,內含12位分辨率A/D轉換器。NS2009能通過執行兩次A/D轉換查出被按的屏幕位置, 除此之外,還可以測量加在觸摸屏上的壓力。在2.7V的典型工作狀態下,功耗可小于0.75mW。

2022-07-08 14:01:28 5440

5440

電子發燒友App

電子發燒友App

評論