0電阻 上拉電阻 下拉電阻

2012-08-06 13:38:12

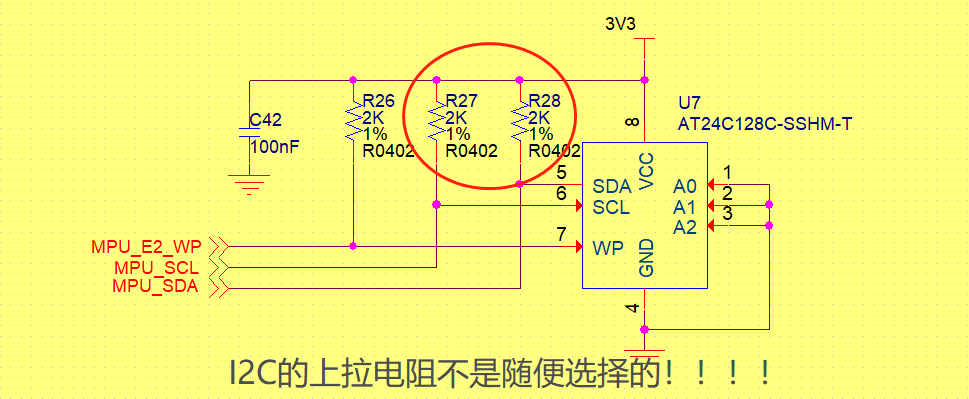

如圖,像這種IIC的電路為什么要加這些4.7kΩ、100Ω的上拉電阻?

2019-02-15 09:58:53

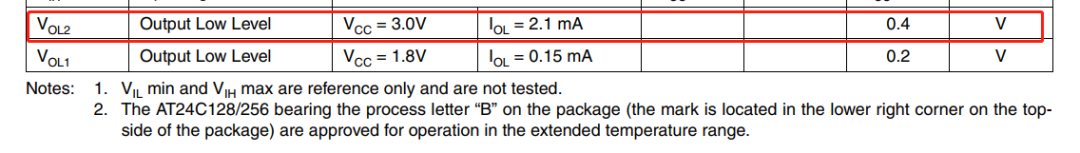

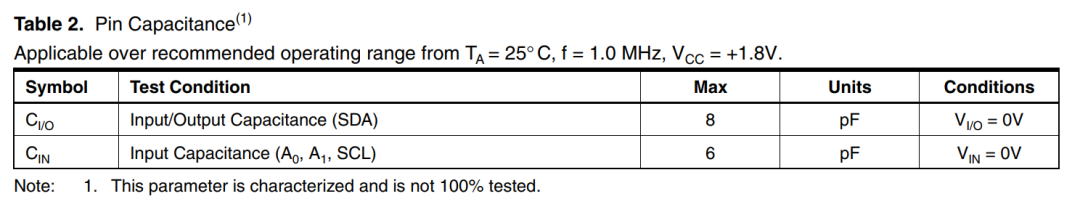

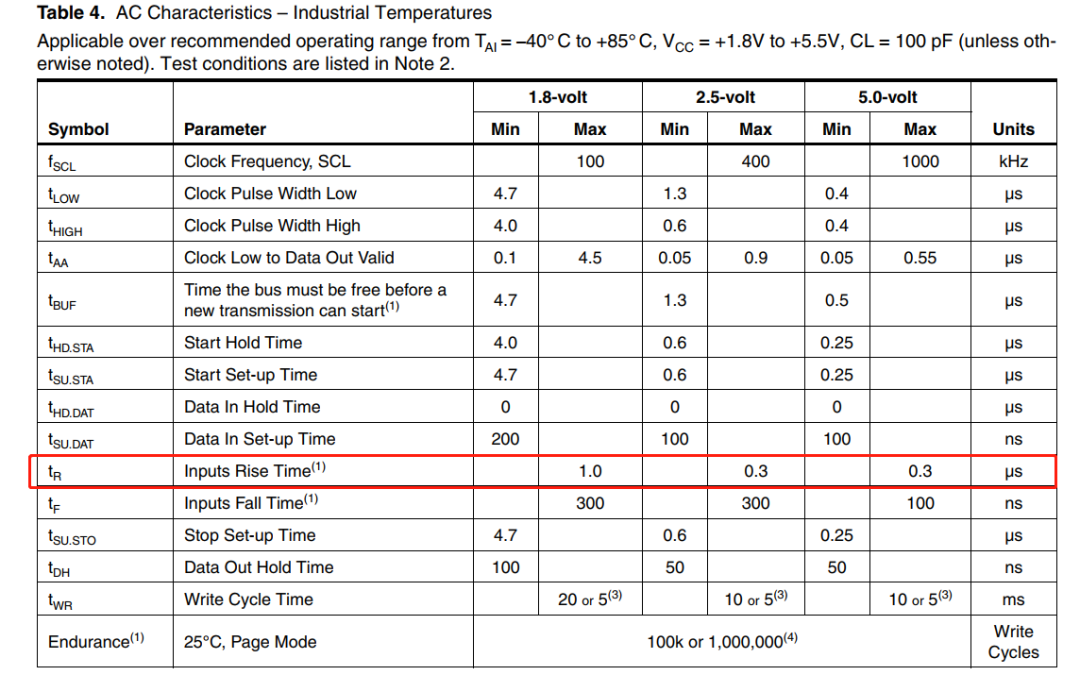

I2C信號一般需要外接上拉電阻,如果主控內部有上拉電阻,是否可以省略外部上拉?這個是否需要上拉根據什么來決定?是根據從器件的輸入電流來決定的嗎?芯片的輸入電流參數(Ii 即input current)怎么理解,設計電路時針對這個參數需要注意什么?

2018-06-07 10:01:00

的,因為電路板會有寄生效應如寄生電容,它和上拉電阻正好形成了串聯RC電路,會有時間延遲,而這個延遲必須要小于電平低有效到高有效的時間,否則芯片讀到的電平是錯誤的。從圖2中I2C硬件架構可以知道,芯片從0到

2022-11-29 08:00:00

我的I2C通信需要被拉到3.3V,但是我不知道我應該使用什么尺寸的上拉電阻。我讀過的其他論壇的帖子,建議2.7k歐姆或4.7K歐姆,但這似乎只是讓高可以在3.3V和是在3.0V低。這是正常的嗎?我用

2019-04-03 15:13:49

我在使用xilinx芯片的許多電路板上遇到了一些奇怪的問題。在我們的3個I / O引腳上,我連接了施密特逆變器,驅動了一些LED。這一直有效,如果沒有加載xilinx程序,這些LED將保持開啟狀態

2019-05-16 14:05:51

上拉的作用是將不確定的信號通過一個電阻嵌位在高電平!雖然在電路設計里經常用,但原理上我還有點不明白,假設圖1,輸出端OUT輸出一個2V的電平,假設這個信號在高低電平之間是個不確定信號,加上上拉后,它

2023-05-15 10:59:25

采用這種方法,以保證正確的電路狀態, 以免發生意外,比如,在電機控制中,逆變橋上下橋臂不能直通,如果它們都用同—個單片機 來馳動,必須設置初始狀。.防止直通!2、 定義:上拉就是將不確定的信號通過一個

2017-08-28 09:27:18

采用這種方法,以保證正確的電路狀態, 以免發生意外,比如,在電機控制中,逆變橋上下橋臂不能直通,如果它們都用同—個單片機 來馳動,必須設置初始狀。.防止直通!2、 定義:上拉就是將不確定的信號通過一個

2017-11-16 17:14:38

的電路狀態,以免發生意外,比如,在電機控制中,逆變橋上下橋臂不能直通,如果它們都用同一個單片機來驅動,必須設置初始狀態.防止直通! 2、定義: l 上拉就是將不確定的信號通過一個電阻嵌位在高電平!電阻

2011-09-19 08:55:51

在低電平。上拉電阻與下拉電阻用在什么場合?答:用在數字電路中,存在高低電平的場合。上拉電阻與下拉電阻怎么接線?答:上拉電阻:電阻一端接VCC,一端接邏輯電平接入引腳(如單片機引腳)下拉電阻:電阻...

2022-01-14 08:44:01

上拉電阻與下拉電阻上拉(Pull Up )或下拉(Pull Down)電阻(兩者統稱為“拉電阻”)最基本的作用是:將狀態不確定的信號線通過一個電阻將其箝位至高電平(上拉)或低電平(下拉),無論它

2021-12-13 07:08:22

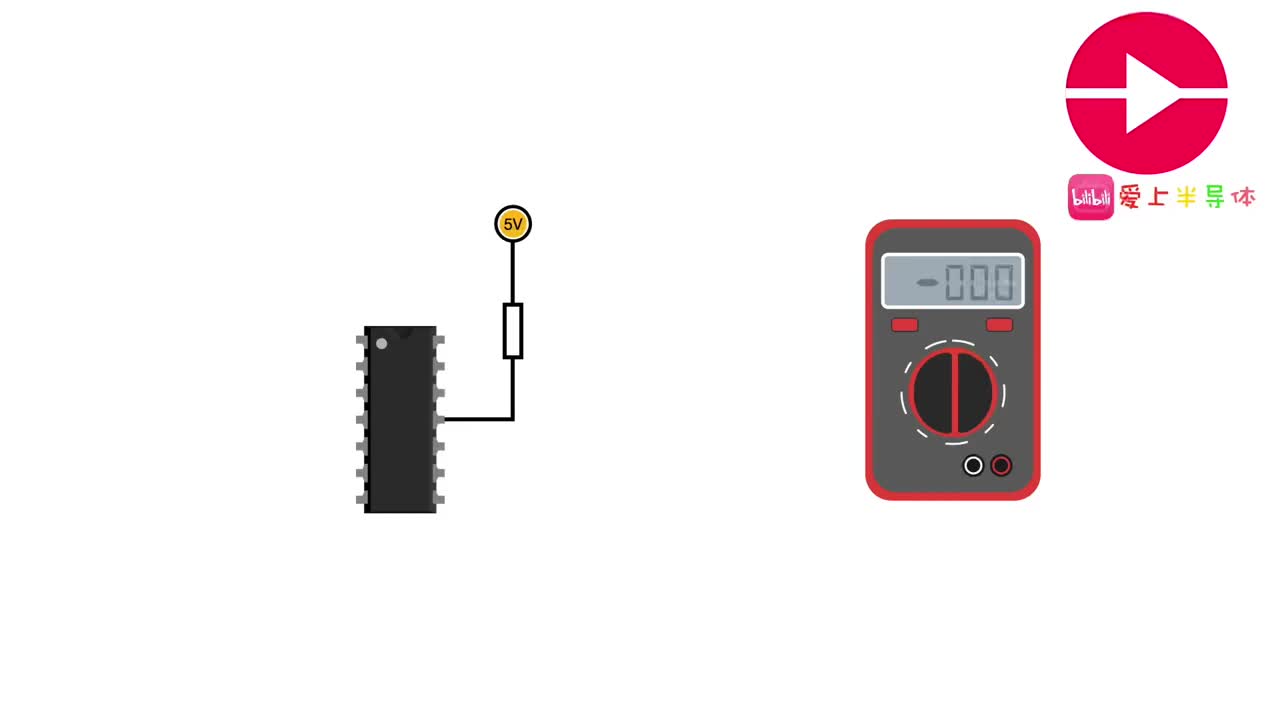

上拉電阻與下拉電阻用在什么場合? 答:用在數字電路中,存在高低電平的場合。 上拉電阻與下拉電阻怎么接線? 上拉電阻:電阻一端接VCC,一端接邏輯電平接入引腳(如單片機引腳) 下拉電阻:電阻一端接GND,一端接邏輯電平接入引腳(如單片機引腳)

2019-05-20 13:48:41

:一般說法是上拉增大電流,下拉電阻是用來吸收電流。1、當 TTL 電路驅動 CMOS 電路時,如果電路輸出的高電平低于 CMOS 電路的最低高電平 (一般為 3.5V), 這時就需要在 TTL 的輸出端接上拉電阻,以提高輸出高電平的值。2、OC 門電路必須使用上拉電阻,以提高輸出的高電平值。

2021-12-13 06:05:27

上拉電阻與下拉電阻是如何定義的?拉電阻的作用有哪些?上拉電阻的應用原則有哪些?

2021-10-14 07:20:37

硬件電路中的上拉電阻為什么能上拉?

2021-01-28 07:50:20

上拉電阻到底是咋完成上拉的啊

2023-10-31 06:52:32

上拉電阻就是把不確空的信號通過一個電阻箝位在高電平,此電阻還起到限流的作用。同理下拉電阻是把不確定的信號箝位在低電平。上拉電阻是指器件的輸入電流,而下拉電阻指的是輸出電流。

2018-09-10 17:43:34

經常看到芯片設計手冊時,芯片外圍會有上拉或者下拉電阻還有一些無源器件。如何選擇正確值的上拉電阻和下拉電阻?上拉電阻和下拉電阻是如何確定?還是在選擇此類電阻的時候,有個特定的范圍?對上拉電阻和下拉電阻

2021-11-12 07:28:55

上拉電阻和下拉電阻的區別及案列分析上拉電阻在一個信號未過來之前、默認(保證)該電位的電平信號是高電平,在信號過來后如果是高電平、那么保持高電平。如果過來低電平信號、那么輸出的信號就會變成低電平。改圖

2022-01-14 06:30:35

上拉電阻和下拉電阻上拉電阻(Pull-Up)所謂上拉電阻就是用一個電阻將VCC和單片機的IO口直接連接起來,目的是當IO在沒有輸出一個確定信號時將IO的電位鉗在一個高電平上。上拉電阻作用如下:1.當

2022-01-25 07:23:49

去控制把上拉電阻的電流拉下來成為低電平。反之, l 尤其用在接口電路中,為了得到確定的電平,一般采用這種方法,以保證正確的電路狀態,以免發生意外,比如,在電機控制中,逆變橋上下橋臂不能直通,如果它們

2008-05-22 08:46:35

端接上拉電阻,以提高輸出高電平的值。2、OC門電路“必須加上拉電阻,才能使用”。3、為加大輸出引腳的驅動能力,有的單片機管腳上也常使用上拉電阻。4、在COMS芯片上,為了防止靜電造成損壞,不用的管腳不能

2015-06-24 11:24:37

接口的輸出端是漏極開路或集電極開路,所以必須在接口外接上拉。上拉電阻的取值和I2C總線的頻率有關,工作在standard mode時,其典型值為10K。在FAST mode時,為減少時鐘上升時間,滿足

2018-10-19 16:30:19

高電平的值。 2、OC門電路必須加上拉電阻,才能使用。 3、為加大輸出引腳的驅動能力,有的單片機管腳上也常使用上拉電阻。 4、在COMS芯片上,為了防止靜電造成損壞,不用的管腳不能懸空,一般接上拉

2019-06-27 05:55:08

上拉電阻: 1、當TTL電路驅動COMS電路時,如果TTL電路輸出的高電平低于COMS電路的最低高電平(一般為3.5V),這時就需要在TTL的輸出端接上拉電阻,以提高輸出高電平的值。 2、OC

2021-12-07 08:27:59

,TTL)或OD(漏極開路,CMOS)輸出,那么不用上拉電阻是不能工作的, 這個很容易理解,管子沒有電源就不能輸出高電平了。2、如果輸出電流比較大,輸出的電平就會降低(電路中已經有了一個上拉電阻,但是

2021-12-01 11:15:35

上拉電阻有什么作用?如何去計算上拉電阻的阻值?51型單片機IO口有什么特點?AVR單片機IO口的輸入狀態有哪幾種?

2021-07-07 07:29:25

,考慮到這個項目是帶模擬電視芯片的,以前就出現過模擬電視芯片的I2C地址沒有去配,導致出現漏電情況,遂立馬去看是不是這個問題,結果是遺憾的,配了!那再仔細檢查了基帶的GPIO口和其他的I2C,發現都配

2011-12-15 18:34:39

上拉電阻的作用

2021-01-29 07:18:20

1、介紹使用微控制器(MCUs) 或任何數字邏輯設備時,上拉電阻器非常常見。本教程將解釋何時何地使用上拉電阻器,然后我們將做一個簡單的計算,以顯示為什么上拉很重要。2、上拉電阻是什么?假...

2022-02-09 06:35:16

stc89c52單片機除了p0口其他io口都沒有集成上拉電阻。上拉電阻的作用:單片機內部控制io口高低電平是通過類似場效應管或三極管的裝置進行控制的,以三極管為例,三極管的集電極連接電源負極集電極

2022-01-14 07:14:42

。2、OC 門電路必須加上拉電阻,以提高輸出的搞電平值。3、為加大輸出引腳的驅動能力,有的單片機管腳上也常使用上拉電阻。4、在COMS 芯片上,為了防止靜電造成損壞,不用的管腳不能懸空,一般接上拉...

2021-07-27 06:52:51

。2、OC門電路必須加上拉電阻,才能使用。3、為加大輸出引腳的驅動能力,有的單片機管腳上也常使用上拉電阻。4、在COMS芯片上,為了防止靜電造成損壞,不用的管腳不能懸空,一般接上拉電阻產生降低輸入阻抗

2014-05-12 08:24:37

上拉、下拉電阻的作用

2012-08-20 14:53:59

什么是上拉和下拉電路?上拉與下拉電路的實際作用是什么?上/下拉電阻阻值的選擇原則是什么?

2021-09-29 07:14:38

波干擾。 8、在數字電路中不用的輸入腳都要接固定電平,通過1k電阻接高電平或接地。 四、上拉電阻阻值選擇原則 1、從節約功耗及芯片的灌電流能力考慮應當足夠大;電阻大,電流小。 2、從確保足夠

2020-12-14 17:21:30

論壇$ |+ @( I8 o& g1 Y2、從確保足夠的驅動電流考慮應當足夠小;電阻小,電流大。對于高速電路,過大的上拉電阻可能邊沿變平緩。EDA365- K) l% _7 b5 T+ J-

2014-11-17 10:24:15

的輸出接口就不要接東西了。 舉例: 圖中上下兩個電阻分別為下拉電阻和上拉電阻,上拉就是將A點的電位拉高,下拉就是將A點的電位拉低,圖中的12k有些是沒有畫出來的,或者是沒有的. 他們的作用就是在電路驅動器關閉時,給該節點一個固定的電平

2018-06-28 06:21:54

),輸入用。為低電平信號輸入作了優化,省去外部上拉電阻,例如按鍵輸入,低電平中斷觸發信號輸入3 推挽強輸出狀態,驅動能力特強(>20mA),可直接推動LED,而且高低驅動能力對稱.在實際應用中,我

2011-11-15 14:10:42

(不知道是低電平還是高電平),那么這個狀態就是開漏狀態,所以此時要向外圍電路輸出一個高電平是不可能的,如果想輸出一個高電平,則必須在NPN的集電極上面來一個上拉電阻。這時又體現出上拉的一個作用:就是將不

2020-06-12 07:52:09

GPIO上有上拉電阻嗎?

如果不是,那么當您釋放按鈕時,GPIO 基本上只是浮動的,可以是任何值。

要么從 GPIO 上拉 10K 到 3.3V,要么將 pinMode 更改為 INPUT_PULLUP。后者將使用大約 36K 的內部上拉電阻,只要到按鈕的引線相當短就可以了

2023-05-22 06:54:06

如題!最近設計I2C的時候,考慮上拉電阻的位置有這個疑問

2019-02-19 15:39:49

Quartus II 中管腳上拉電阻(弱上拉)的設置方法Quartus II 中管腳上拉電阻(弱上拉)的設置方法在使用 Altera 的 FPGA 時候,根據系統設計需要在管腳的內部加上上拉電阻

2012-08-12 16:10:09

按下時,由于干擾,可能高也可能是低信號輸入。根據實際需要,為保證WK_UP不被按下時,STM32能夠確定檢測到IO口是低電平,所以設置接入下拉電阻。2、上拉電阻和下拉電阻上拉電阻...

2021-08-18 06:27:20

ds18b20電路中的上拉電阻R3是什么作用?

2016-04-10 20:48:58

下拉電阻使電阻匹配,能有效的抑制反射波干擾。5、預設空間狀態/默認電位在一些CMOS輸入端接上拉或下拉電阻是為了預設默認電位。當不用這些引腳時,這些輸入端下拉接低電平或上拉接高電平。在I2C等總線

2019-10-08 07:00:00

上拉下拉電阻的定義以及用法為什么要使用拉電阻上拉電阻阻值的選擇原則

2021-04-06 06:06:42

上拉、下拉以及對應上拉電阻和下拉電阻的作用原理一、什么是上拉和下拉電路上拉(Pull Up )或下拉(Pull Down)電阻兩者統稱為拉電阻上拉就是單片機的IO口串聯一個電阻到VDD;下拉就是

2021-07-26 06:46:17

CMOS 輸入端接上或下拉電阻是為了預設缺省電位。當你不用這些引腳的時候,這些輸入端下拉接 0 或上拉接 1。在I2C總線等總線上,空閑時的狀態是由上下拉電阻獲得。

6. 提高芯片輸入信號的噪聲容限

2023-05-18 17:30:56

仿真電路如圖,感覺上拉電阻沒起作用,試著刪除上拉電阻發現對的仿真還是這個結果,說明這上拉電阻根本沒用啊。上拉電阻難道不是這么連的嗎,而且為什么只有P1口的數碼管成功驅動了?大神們快來幫幫我吧!

2016-06-30 11:15:11

上拉電阻那它的端口在默認值為高電平,你要控制它必須用低電平才能控制如三態門電路三極管的集電極,或二極管正極去控制把上拉電阻的電流拉下來成為低電平。反之,C、尤其用在接口電路中,為了得到確定的電平,一般

2018-11-30 11:55:14

上拉電阻在單片機電路中的作用主要有以下幾點:

限制電流的流動:在單片機電路中,電阻的作用之一是限制電流的流動。電阻的阻值越大,通過電阻的電流就越小,反之亦然。通過選擇不同阻值的電阻,可以控制電路中

2023-09-05 16:45:53

上拉電阻: 1、當TTL電路驅動COMS電路時,如果TTL電路輸出的高電平低于COMS電路的最低高電平(一般為3.5V),這時就需要在TTL的輸出端接上拉電阻,以提高輸出高電平的值。 2

2019-09-06 15:19:36

在 NPN 的集電極上面來一個上拉電阻。這時又體現出上拉的一個作用:就是將不確定的信號通過一個電阻嵌位(保持)在一個高電平上,下拉同理。這里對于 OC 門還有一個應用,可以控制高電位的電路,如果外圍電路

2020-10-12 09:37:23

上拉電阻的主要作用,是在電路的運行過程中與上接電阻進行配合,在電路驅動器關閉時保證電路的固定電平。可見下拉電阻在電路中的主要作用就是保持電路的正常運行,維持電路的正常運行。那么在對上拉電阻進行

2016-01-20 10:39:09

I2C上拉電阻 在一些PCB的layout中,大家往往會看到在I2C通信的接口處,往往會接入一個4.7K的電阻,有的datasheet上面明確有要求,需要接入,有的則沒有要求。 I2C接口 對于

2022-01-14 07:22:21

/show-1821.htm 在數字邏輯電路中,我們經常使用上拉或下拉電阻,用多了也比較隨意, 10K.5.6K.4.7K.1K都能看到,那么到底用多少了?如何量化呢?先來看看我的一個設計教 訓:在一塊應用板中,應用環境比較

2017-11-16 17:16:04

一塊電路板,需要在工業或者強干擾場合應用,如何提高抗干擾能力呢?我結合實際經驗教訓來探討一下,首先來說說上拉電阻。http://www.gooxian.com/ 在數字邏輯電路中,我們經常使用上拉或

2017-08-28 09:29:41

),這會產生大量的熱,如果系統采用的是電池供電,那么電池電量很快就會被耗盡。除了避免微控制器懸空I/O管腳的相關問題,在使用開漏拓撲電路時,上拉電阻也是必要的。我們在一篇演講文章中詳細討論了開漏電路設計。圖

2018-11-30 09:12:02

上拉就是將不確定的信號通過一個電阻鉗位在高電平,電阻同時起限流作用。下拉同理,也是將不確定的信號通過一個電阻鉗位在低電平。

2020-08-14 06:35:49

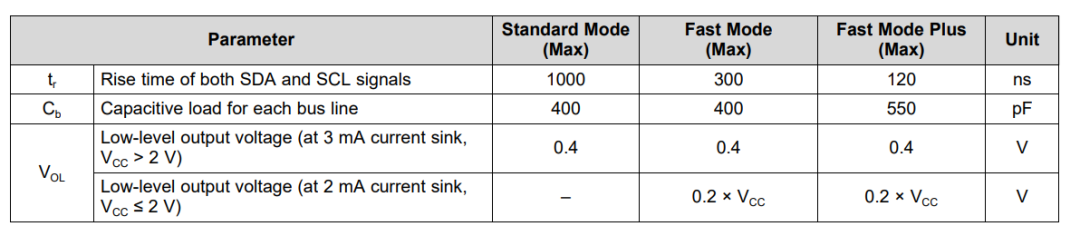

引起的功耗同樣適用于輸出拉電阻,因此拉電阻不宜太小,但在輸出信號速度比較快的電路下,拉電阻也不宜太大,如下圖所示為I2C總線上拉電阻的參考最大值(來自ST存儲芯片 AT24C02數據手冊)。在總線上總會有

2020-08-19 09:00:00

效的抑制反射波干擾。5、預設空間狀態/默認電位在一些CMOS輸入端接上拉或下拉電阻是為了預設默認電位。當不用這些引腳時,這些輸入端下拉接低電平或上拉接高電平。在I2C等總線上空閑時的狀態是由上下拉電阻

2019-10-11 08:30:00

開發板I2C連接到RTC(RX8010)芯片,I2C總線上沒有接上拉電阻,LS1012A手冊上說它的I2C是open drain輸出的,為什么沒有上拉電阻? 哪位能幫助解釋一下,謝謝

2022-01-05 06:28:48

引腳的輸出時,一個具有上拉功能,而沒有上拉的只是在PWM引腳的輸出上顯示零伏。上拉導致PIC復位,即使我沒有在配置位(即MCLR復位選項-在一些PIC中出現)中“告訴”它這樣做。請參閱下面的配置位。我

2020-05-06 13:23:48

為400pF。之后需要I 2 C緩沖芯片。這通常發生在用于7位可尋址I 2 C實現的112個器件的理論尋址限制之前。現在,根據實際的經驗法則,這里是您應該考慮在電路中測試的電阻值,看看您是否獲得了所需的性能

2018-11-09 09:14:56

什么是上拉電阻?上拉就是將不確定的信號通過一個電阻鉗位在高電平,電阻同時起限流作用。下拉同理,也是將不確定的信號通過一個電阻鉗位在低電平。為什么需要上拉電阻?一般作單鍵觸發使用時,如果IC本身沒有內

2021-08-12 13:35:38

二極管正極去控制把上拉電阻的電流拉下來成為低電平。尤其用在接口電路中,為了得到確定的電平,一般采用這種方法,以保證正確的電路狀態,以免發生意外,比如,在電機控制中,逆變橋上下橋臂不能直通,如果它們都用

2014-08-21 09:56:08

的抑制反射波干擾。上拉電阻阻值的選擇原則包括:1、從節約功耗及芯片的灌電流能力考慮應當足夠大;電阻大,電流小。2、從確保足夠的驅動電流考慮應當足夠小;電阻小,電流大。3、對于高速電路,過大的上拉電阻

2011-06-02 16:03:48

的抑制反射波干擾。上拉電阻阻值的選擇原則包括:1、從節約功耗及芯片的灌電流能力考慮應當足夠大;電阻大,電流小。2、從確保足夠的驅動電流考慮應當足夠小;電阻小,電流大。3、對于高速電路,過大的上拉電阻可能

2012-06-10 21:25:15

前言:在一張原理圖中無論時上拉還是下拉都是非常普遍的,轉載此文章,可以很快的理解上拉電阻與下拉電阻的原理與作用。如果還沒有理解,可以參考上拉與下拉的原理與應用2者共同的作用是:避免電壓的“懸浮

2022-01-14 08:28:26

電阻是指器件的輸入電流,而下拉電阻指的是輸出電流。 那么在什么時候用上、下拉電阻呢?1.當TTL電路的最低高電平(一般為3.5V),這時就需要在TTL的輸出端接上拉電阻,以提高輸出高電平的值。2

2017-05-22 18:49:54

夠,就需要加上拉電阻。B、如果有上拉電阻那它的端口在默認值為高電平,你要控制它必須用低電平才能控制如三態門電路三極管的集電極,或二極管正極去控制把上拉電阻的電流拉下來成為低電平。反之,C、尤其用在接口電路

2015-06-26 14:26:17

電路:一、普通IO口1、基級(②位置)為低電平時,PNP導通,此時單片機IO口輸出的是低電平,當基級(②位置)為高電平時,PNP導通,此時單片機IO口輸出的是高電平。2、這里注意,④位置上是一個上拉電阻

2020-07-30 08:30:00

請問用TMS320C5515的GPIO口模擬I2C是否需要加上拉電阻?

2018-07-31 07:48:20

為了避免出現任何不受控制的I/O電平,STM32F10xxx在JTAG輸入引腳內部嵌入了上拉和下拉電阻: ●JNTRST:內部上拉 ●JTDI:內部上拉 ●JTMS/SWDIO:內部上拉 ●TCK

2019-04-23 19:01:31

stm32f051的i2c需要外接上拉電阻嗎,直接用內部上拉行不行,還有庫中的I2C_Init函數中有這么一句/* Enable I2Cx Peripheral */I2Cx->CR1 |= I2C_CR1_PE;為什么初始化有些i2c寄存器需要使能i2c。最后附上波形,希望哪位大哥幫幫忙,看看是什么問題。

2019-03-12 07:14:31

請問為什么有時在I2C中將SDA和SCL 上加各加個上拉電阻呢?

2023-05-08 18:01:37

請問用TMS320C5515的GPIO口模擬I2C總線需要接外部上拉電阻嗎?需要的話阻值為多少比較合適呢?

2019-10-28 09:37:43

輸出端的電位。示例:51單片機中除了P0口有兩個場效應管,其余三個端口P1,P2,P3都有上拉電阻。如下圖所示:作用除此之外,上拉電阻作用還有很多。比如CMOS芯片上輸入的電阻一般很大,為了防止靜電造成損壞,不用的管腳不能懸空,一般會接上拉電阻來保護內部電路;加上拉電阻還能提高輸出端的電流

2022-01-25 06:28:33

電子發燒友App

電子發燒友App

評論