最近調試芯片遇到一個選擇題,需要決定數據接口的接口標準,是選用LVDS差分接口還是CMOS單端接口。說實話,之前接觸多的還是CMOS單端接口,只是看到過很多資料介紹過LVDS差分接口。

官方說法里,它的主要優點有:

抗干擾能力強,具有更高的數據傳輸速率

更好的信號完整性

降低了電平幅度和電路功耗

既然有這么多優點,這次我們就選用LVDS差分接口,看看我們能不能感受到LVDS的優勢。

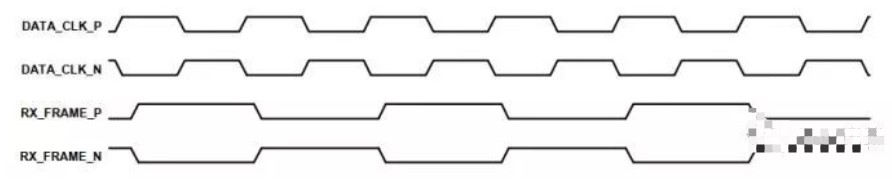

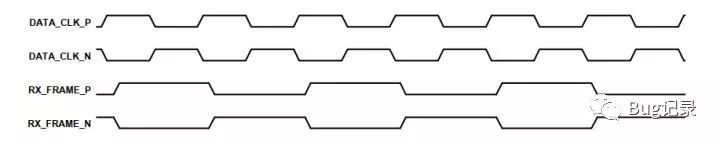

每對LVDS信號是一個差分信號對,一個信號用兩個相反的p,n信號線表示,通過差值 |Vp - Vn|傳輸數據,這樣可以有效減小共模噪聲的干擾,信號線傳輸如下圖:

圖中含有DATA_CLK, RX_FRAME兩個LVDS信號對

而FPGA內部處理信號肯定還是需要使用單端信號,這時就需要經過一個差分轉單端的“工具”,將差分信號轉換為FPGA更方便處理的單端信號。

在Xilinx中,我們可以用IBUFDS原語,可以在Language Template中找到這個原語的示例,經過修改一番后,可以將差分的data_clk轉換為單端的data_clk, 原語如下:

IBUFDS #(

.DIFF_TERM("FALSE"), // Differential Termination

.IBUF_LOW_PWR("TRUE"), // Low power="TRUE", Highest performance="FALSE"

.IOSTANDARD("DEFAULT") // Specify the input I/O standard

) IBUFDS_inst (

.O(data_clk_tmp), // Buffer output

.I(data_clk_p), // Diff_p buffer input (connect directly to top-level port)

.IB(data_clk_n) // Diff_n buffer input (connect directly to top-level port)

);

將需要轉換的data_clk P端和N端接入IBUFDS的I和IB端口,就可以在O端口得到轉換的單端信號。

除了CLK時鐘信號,其他信號的輸入轉換基本結束了;而CLK時鐘信號還需要接入BUFG,因為CLK時鐘只有接入BUFG才能接入全局時鐘網絡,這對于減小時序問題有幫助。

同樣在Language Template中找到這個原語的示例,修改后如下:

BUFG BUFG_i0 (

.O(data_clk), // 1-bit output: Clock output, 36MHz.

.I(data_clk_tmp) // 1-bit input: Clock input, 36MHz.

);

一個輸入一個輸出,非常簡單的原語調用!

另一邊,有輸入就會有輸出,輸出的問題也好解決,同樣使用一個OBUFDS原語實現單端轉差分,在Language Template中找到原語,修改后如下:

OBUFDS #(

.IOSTANDARD("LVDS18"), // Specify the output I/O standard

.SLEW("SLOW") // Specify the output slew rate

) OBUFDS_inst (

.O(tx_frame_p), // Diff_p output (connect directly to top-level port)

.OB(tx_frame_n), // Diff_n output (connect directly to top-level port)

.I(tx_frame) // Buffer input

);

設置好相應的參數之后,將單端信號接入OBUFDS的I端口,O端口輸出差分信號的P端,OB端口輸出差分信號的N端。

最后一個小問題就是在XDC設置中,因為一個信號對有兩個管腳,比單端信號多了一倍的管腳綁定工作量;但其實我們可以只需要綁定P端的管腳,軟件會自動幫我們綁定N端的管腳。

在設置輸入輸出端口的“IOSTANDARD”中,遇到了些許問題,這里寫出來記錄一下,也讓后面遇到這個問題的人有個參考;最初設置差分信號的“IOSTANDARD”時,我想當然的使用了“LVDS”,“LVDS18”等參數,但是這些參數都不能最終生成比特流;

在查了一些資料以及Vivado本身的I/O Port界面里參數后發現,差分信號的IOSTANDARD需要這樣設置:

set_property IOSTANDARD DIFF_HSTL_II_18 [get_ports tx_frame_p]

因為我的IO電壓是1.8V,所以最終使用了“DIFF_HSTL_II_18”,如果有更好的方案,可以一起探討探討。

總結:

輸入信號需要用到IBUFDS實現差分轉單端,輸入時鐘還需要加BUFG

輸出信號使用OBUFDS實現單端轉差分

差分信號只需要綁P端管腳,“IOSTANDARD”設置需要注意

輸入輸出端口的簡單處理之后,這些信號為了提高傳輸數據的效率,還使用了DDR(Double Data Rate)技術傳輸數據,如何解決DDR問題,下一篇文章再來探討。

審核編輯:劉清

LVDS差分接口信號輸入輸出的處理簡析

- FPGA(591965)

- CMOS(233055)

- lvds接口(17204)

- 差分接口(11281)

相關推薦

LVDS發送芯片之輸入與輸出信號

這種接口電路中,采用單路方式傳輸,每個基色信號采用6位數據,共18位RGB數據,因此,也稱18位或18bit LVDS接口。此,也稱18位或18bit LVDS接口。

2023-03-28 11:46:23 2931

2931

2931

2931LVDS接口標準

使得信號能在差分PCB線對或平衡電纜上以幾百Mbps的速率傳輸,其低壓幅和低電流驅動輸出實現了低噪聲和低功耗。幾十年來,5V供電的使用簡化了不同技術和廠商邏輯電路之間的接口。然而,隨著集成電路的發展

2011-02-23 09:55:17

LVDS低電壓差分信號

LVDS:Low-Voltage Differential Signaling 低電壓差分信號。一種信號傳輸模式,是一種電平標準,LVDS接口又稱RS-644總線接口,是一種數據傳輸和接口

2016-04-15 16:13:33

輸入為數字QPSK信號,輸出為模擬差分QPSK信號,選擇哪款DAC?

輸入為數字QPSK信號(I和Q兩路數字信號,或者,IP IN QP QN四路數字信號),輸出為模擬差分QPSK信號(IP IN QP QN四路模擬信號),該選擇哪款DAC芯片?如果沒有單一芯片可以滿足要求,應該用什么方案?

2023-12-12 07:14:59

輸入輸出電壓差

本帖最后由 洌洌的水 于 2015-5-8 22:27 編輯

請問開關型降壓變換器輸入輸出電壓差是什么意思,是輸出達到額定值時,輸入端與輸出端的最小壓降嗎?是的話,這個值隨輸出電流變化嗎?就像圖里面的輸入——輸出電壓差(V),這是LM2576的資料圖

2015-05-08 22:18:20

A/D差分輸入信號簡單介紹

文章目錄A/D 差分輸入信號A/D 差分輸入信號在前面的文章已經提到過,控制字的第4位和第5位是用于控制 PCF8591 的模擬輸入引腳是單端輸入還是差分輸入。差分輸入是模擬電路常用的一個技巧,這里

2021-12-02 06:32:49

AD7760評估板的差分輸入信號如何產生?

買的AD7760的開發板,上面只提供差分輸入信號接口,而信號發生器只能產生單端信號,難道我自己要去做一個單端轉差分的電路,產生差分信號,那這樣開發板的意義又何在?

2023-12-07 08:04:51

FPGA | LVDS屏幕接口的應用

;4) PCB 板盡可能鋪設大面積的 GND ;

5) LVDS 輸出差分信號走線設計成 100Ω差分匹配,走線盡可能保持等長;6) LVDS 輸出差分信號正負通道間隔 S1 盡可能

2023-06-05 17:31:08

FPGA編程LVDS信號圖像處理技術

各位大神,小弟這邊先謝過了,真的很急!目前我需要使用FPGA技術來處理一款1對時鐘LVDS信號和8對數據LVDS信號攝像頭模組,我這邊只能對并口信號和MIPI信號輸出的攝像頭模組進行測試調焦,對于LVDS信號的模組沒有相關技術,請大神幫忙啊!!!非常感謝!!!可付報酬!!!

2014-07-17 16:40:58

GPIO通用輸入輸出接口

I/O接口:GPIO、IIC、SPI、UART、USB、HDMI(1)GPIO通用輸入輸出接口,General Purpose Input Output, GPIO。 輸出引腳的兩個上下拉二極管具有

2021-12-16 07:20:11

Input接口信號的比較

,提高數據的傳輸速度,發展了低壓差分信號LVDS接口技術。LVDS是一種低擺幅的差分信號技術,它使得信號能在差分PCB線對或平衡電纜上以幾百Mbps的速率傳輸,其低壓幅和低電流驅動輸出實現了低噪聲

2019-09-23 09:05:05

LDO輸入輸出電壓差

輸入輸出電壓差輸入輸出電壓差是低壓差線性穩壓器最重要的參數。在保證輸出電壓穩定的前提下,該電壓差越低,線性穩壓器的性能越好。比如,5.0V的低壓差線性穩壓器,只要輸入5.5V,就能使輸出電壓穩定在5.0V。

2011-06-16 16:15:33

LabVIEW偽差分輸入

LabVIEW偽差分輸入什么是偽差分輸入? ?編輯添加圖片注釋,不超過 140 字(可選)偽差分信號連接可以降低噪聲并抑制共模電壓,從而使輸入信號能夠在儀表放大器的共模極限范圍內浮動。對于偽差分輸入

2022-04-13 20:43:52

OpenHarmony智慧設備開發-芯片模組簡析RK3568

處理器采用22nm工藝,主頻高達2.0GHz;支持藍牙、Wi-Fi、音頻、視頻和攝像頭等功能,擁有豐富的擴展接口,支持多種視頻輸入輸出接口,配置雙千兆自適應RJ45以太網口,可滿足NVR、工業網關等多網口

2023-05-16 14:56:42

OpenHarmony智慧設備開發-芯片模組簡析T507

(RGB/2*LVDS/HDMI/CVBS OUT)、多路視頻輸入接口(MIPI CSI/BT656/BT1120),支持4K@60fps H.265解碼,4K@25fps H.264解碼,DI,3D

2023-05-11 16:34:42

為什么變壓器輸入輸出端的差分信號要一一對應(即P端和P端 對應,N端和N端對應)

PHY和RJ45之間的網絡變壓器輸入輸出端的相位關系是什么,為什么變壓器輸入輸出端的差分信號要一一對應(即P端和P端 對應,N端和N端對應)?

2019-07-26 11:05:03

人機交互接口技術簡析

期末復習提綱,考試范圍,第二章模擬量輸入輸出通道接口技術第三章人機交互接口技術第四章常用控制程序設計第六章總線接口技術第七章過程控制數據處理方法第八章PID算法第十一章微機控制系統抗干擾設計,試題

2021-09-10 07:44:59

低功耗差分接口的基本約束

之間傳輸差分電流。接下來如果有要求,在使用一個單獨的互感級實現電流電壓轉換前增大差分電流。如果容性負載沒有足夠大到影響電壓信號,在芯片內部要進行低阻抗到高阻抗的變換。低輸入阻抗對于電流處理來說非常

2019-04-16 07:00:03

在差分輸入或者輸出的另外一個端口用一個電容接地來實現是否合理

最近一直在調試放大器方面的芯片,突然有個關于“差分信號”單端輸入輸出的疑問,寫出來討論一下! 對于差分輸入輸出的好處我就不再多說了,相信大家都有一定的了解!我的疑問就是,我們實驗室使用的幾款放大器

2018-11-29 09:17:14

怎么實現一種基于FPGA高速數據采集系統中的輸入輸出接口?

本文給出了基于FPGA高速數據采集系統中的輸入輸出接口的實現,介紹了高速傳輸系統中RocketIO設計以及LVDS接口、LVPECL接口電路結構及連接方式,并在我們設計的高速數傳系統中得到應用。

2021-04-29 06:04:42

時鐘分配輸入74.25的差分或單端,輸出至少2路74.25M的差分LVDS,請問有哪些芯片通達到功能

您好,我需要一個時鐘分配器,輸入74.25的差分或單端,輸出至少2路74.25M的差分LVDS,有哪些芯片通達 到功能,謝謝

2018-12-17 09:33:40

有沒有人有使用差分HSTL與LVDS接口的經驗?

我正在使用Artix 7 fpga。我沒有2.5V IO庫,所以我不能使用LVDS輸出。有沒有人有使用差分HSTL與LVDS接口的經驗? TI建議為接口提供交流耦合終端,有何評論?見附件。

2020-07-30 10:49:04

液晶屏MIPI接口與LVDS接口區別(總結)

是RGB666或者RGB888還有行場同步和時鐘;LVDS接口信號類型是LVDS信號(低電壓差分對),信號的內容是RGB數據還有行場同步和時鐘;MIPI DSI接口信號類型是LVDS信號,信號的內容是視頻流數據

2016-06-13 20:18:24

簡易USB與LVDS接口轉換器

協議的數據轉換成10位并行輸入FPGA進行協議數據轉換后,再將8位并行數據與USB3300_B進行數據交互,最后以USB協議的差分信號輸出,從而實現LVDS接口到USB接口的轉換。 3 系統硬件

2018-11-22 11:24:30

能否推薦一款差分輸入差分輸出的運算放大器,要求高精度低噪聲能夠對10kHz左右的信號進行正常處理?

AD的技術專家們,能否推薦一款差分輸入,差分輸出的運算放大器,要求高精度,低噪聲,性能較好,能夠對10kHz左右的信號進行正常處理?

2018-10-25 16:04:00

請問 nRESETIN_OUT 復位信號輸入輸出是可以同時使用的嗎?如果不是輸入輸出模式應該如何配置?

本帖最后由 一只耳朵怪 于 2018-6-5 14:31 編輯

Hi,大家好 請問 nRESETIN_OUT 復位信號 :輸入輸出是可以同時使用的嗎?如果不是,輸入輸出模式應該如何配置?謝謝

2018-06-04 15:04:50

請問AD9371模擬輸入輸出端的阻抗控制多少是正確的?

AD的數據手冊中要求模擬輸入輸出控制阻抗為差分100Ω,但應用開發板ADRV9371-WPCBZ的原理圖中模擬輸入輸出使用的變壓器匝數比卻是1:1的,請問差分阻抗控制多少是正確的,謝謝

2023-12-01 07:05:11

請問AD9516的差分參考輸入和外部時鐘輸入能否為LVDS

請教AD9516的差分參考輸入(ref)和外部時鐘輸入(clk)能否為LVDS?還是必須為TTL?謝謝!

2018-11-05 09:24:01

請問USB輸出口的儀器怎么輸出串口信號?

USB是半雙工差分信號,UART-TTL/232/485/422都是串口,每種信號物理特征都不一樣,不可以直接連接輸入輸出,USB和串口通信要用CH340這類轉換芯片,如果是轉232/485還要加232/485驅動芯片。

2023-10-20 08:30:54

請問ad8331怎么配置差分輸入?

把ad8331配制成差分輸入差分輸出,還能根據數據手冊上的單端輸入的說明配置嗎?為什么單獨仿真ad8331的LNA差分輸出信號和輸入信號幅度差不多,沒有放大19dB。

2023-11-21 08:15:40

調試一個項目芯片的輸入信號要用到I/Q差分輸入信號,由于設備限制不能產生I/Q差分輸入信號

最近調試一個發射機項目芯片的輸入信號要用到I/Q差分輸入信號,由于設備限制現在不能產生I/Q差分輸入信號,所以實驗板的調試處于停滯狀態。 想請問一下,在ADI公司所生產的芯片里面有沒有直接能夠產生I

2018-11-28 09:26:07

適用于差分輸入到差分輸出的OPA4830

差分接口應用雙運算放大器和四運算放大器特別適用于差分輸入到差分輸出的應用。通常,這些運算放大器可分為ADC輸入接口或線路驅動器應用。差分I/O的兩種基本方法是無反轉或反轉配置。因為輸出是差分的,所以

2020-09-14 17:13:38

通過一個差分接口來延長SPI總線

本文將介紹如何通過一個差分接口來延長串行外設接口 (SPI) 總線,而這可以應用在支持遠程溫度或壓力傳感器的系統的設計。 在SPI應用中,主控器件和受控器件間的距離相對較近,而信號也通常不會傳遞到

2019-06-13 05:00:02

音頻的輸入輸出問題

手機的耳機插孔那塊是差分輸出的音頻還是單端的左右聲道的音頻信號?我現在使用的是tlv320aic31音頻編解碼芯片,需要差分音頻輸入,可以使用手機接口進行測試嗎??

2018-06-21 11:17:46

32路數字輸入輸出模塊(端子板)

XS-32DIO 32路多功能非隔離輸入輸出模塊(端子板),主要是配合DCS數字、模擬輸入輸出卡或PLC數字、模擬輸入輸出模塊使用。可用來對常規模擬信號、數字信號輸入進行連接或驅動小型

2011-04-01 11:25:58 62

62

62

62模擬量輸入輸出

這類接口板(卡)能使計算機具有輸入輸出模擬量信號的功能,將用模擬量表示的外部狀態轉換成數據(數字量信號),然后傳送到計算機;計算機也可以發送一個數據(數字量信號)

2011-04-04 14:45:01 124

124

124

124用Cyclone FPGA實現雙倍數據率輸入輸出接口

Cyclone 系列芯片是美國A ltera 公司推出的低價格、高容量現場可編程門陣列器件(FPGA ) , 本文概述了他的主要特點, 給出了其在與外部存儲器接口時用到的雙倍數據率輸入輸出接口的設計方

2011-06-27 16:27:41 45

45

45

45Inout雙向端口信號處理方法

Inout端口信號做輸入時,觀察例子中的輸出Data_out_t就應該是高阻態的,Inout在具體實現上一般用三態門來實現。三態門的第三個狀態就是高阻''Z''。當Inout端口不輸出時,將三態門置高阻

2011-11-11 10:24:47 3736

3736

3736

3736串行EEPROM共享輸入輸出配置在半導體上的應用

制備: 在半導體在半導體的家庭利用串行E2PROMs4通信接口信號;片選(CS)設備選擇,串行時鐘(SK或CLK)從設備和數據輸入同步串行數據(DI)向設備輸入串行數據和數據輸出(DO)從設備輸出

2017-03-31 11:18:32 12

12

12

12什么是輸入輸出模塊_輸入輸出模塊有什么作用

輸入輸出模塊也稱為控制模塊,在有控制要求時可以輸出信號,或者提供一個開關量信號,使被控設備動作,同時可以接收設備的反饋信號,以向主機報告,是火災報警聯動系統中重要的組成部分。市場上的輸入輸出

2018-05-21 10:28:16 117113

117113

117113

117113輸入輸出模塊,4 路開關量信號采集

量信號,支持閾值判別預警、狀態觸發報警等功能,4 路繼電器輸出通道,可用于外部設備的開關控制。眾山輸入輸出模塊-ZSR2184,提供一路 RS232 串口,用于參數配置;還提供一路 RS485接口

2019-01-14 09:29:39 4863

4863

4863

4863

開關量輸入輸出

MLK-6DI4DO 開關量輸入輸出模塊是脈聯公司針對設備狀態與控制監測的裝置。廣泛應用于電力、IDC機房、工業、智慧城市、樓宇等各個行業,被眾多系統集成商和自動化公司、研究機構采用

2020-05-11 15:21:49 2233

2233

2233

2233GPIO通用輸入輸出

GPIO通用輸入輸出一、GPIO的功能概述用途:GPIO是通用輸入輸出(General Purpose I/O)的簡稱,主要用于工業現場需要用到數字量輸入/輸出的場合。例如:輸出功能:繼電器、LED

2021-12-20 18:58:47 6

6

6

6龍迅HDMI接口信號轉換的應用案例

Lontium龍迅MIPI/LVDS接口信號轉換器有著多種接口格式,芯片功能包括Transmitter、Receiver、Switch、Splitter、Repeater、Matrix/Crosspoint、Converter

2022-06-14 17:00:55 2463

2463

2463

2463

plc帶模擬量輸入輸出和不帶模擬量輸入輸出有什么區別啊?

的PLC類型,它們之間有很大的差異。 PLC帶模擬量輸入輸出與PLC不帶模擬量輸入輸出的區別在于它們可以控制和處理的不同信號類型。模擬量輸入輸出和數字量輸入輸出都是一種用于控制系統的信號類型。 “數字量”信號是通過開關等離散的狀態表

2023-10-17 16:44:51 927

927

927

927鎖相環的輸入輸出相位一致嗎?

鎖相環是保證相位一致,還是相位差一致?鎖相環的輸入輸出相位一致嗎? 鎖相環(PLL)是一種回路控制系統,用于保持輸出信號的相位與參考信號的相位之間的恒定關系。簡單來說,鎖相環的目的是保證相位一致

2024-01-31 15:45:48 202

202

202

202 電子發燒友App

電子發燒友App

評論