,然后通過外部物理連接回環(huán)TX-->RX測試誤碼率來驗證鏈路的信號完整性,所以我想進行如下測試:

? ? ? ? 測試路徑: FPGA --> DSP SRIO SerDes ?-->

2018-06-21 06:25:29

做了電路設(shè)計有一段時間,發(fā)現(xiàn)信號完整性不僅需要工作經(jīng)驗,也需要很強的理論指導(dǎo),壇友能提供一些信號完整性的視頻資料么?非常感謝!

2019-02-14 14:43:52

在altium designer中想進行信號完整性的分析,可元件是自己造的,不知道仿真模型怎么建,哪些HC是啥意思也不知道

2012-11-01 21:43:04

在處理高速印刷電路板(PCB)時,必須理解信號完整性(SI)和電源完整性(PI)的基本原理。如今,速度是評估數(shù)字產(chǎn)品功能的主要因素之一。在幾種設(shè)計中,PCB布局對整體功能至關(guān)重要。對于高速設(shè)計,SI

2021-12-30 06:49:16

高速設(shè)計中的信號完整性和電源完整性分析

2021-04-06 07:10:59

原本放在頂層的走線信號傳輸或串擾性能。 對于電源完整性來說,增加電源與地之間的容性耦合可以濾除電源中的交流波動。在實際應(yīng)用中,往往采取加解耦電容的方法。電流密度的動態(tài)顯示可以幫助設(shè)計者直觀了解到電源網(wǎng)

2015-01-07 11:33:53

信號完整性與電源完整性的仿真分析與設(shè)計,不看肯定后悔

2021-05-12 06:40:35

其實電源完整性可做的事情有很多,今天就來了解了解吧。信號完整性與電源完整性分析信號完整性(SI)和電源完整性(PI)是兩種不同但領(lǐng)域相關(guān)的分析,涉及數(shù)字電路正確操作。在信號完整性中,重點是確保傳輸

2021-11-15 07:37:08

先說一下,信號完整性為什么寫電源完整性? SI 只是針對高速信號的部分,這樣的理解沒有問題。如果提高認知,將SI 以大類來看,SI&PI&EMI 三者的關(guān)系:所以,基礎(chǔ)知識系列里還是

2021-11-15 06:32:45

高速PCB設(shè)計有很多比較考究的點,包括常規(guī)的設(shè)計要求、信號完整性的要求、電源完整性的要求、EMC的要求、特殊設(shè)計要求等等。本文主要是針對高速電路信號總線做了一些比較常規(guī)的要求列舉了一些檢查要點,其實

2021-01-14 07:11:25

中國電子電器可靠性工程協(xié)會關(guān)于組織召開“信號完整性仿真應(yīng)用”高級研修班的邀請函各有關(guān)單位:為了幫助廣大從業(yè)人員詳細了解信號完整性(SI)和電源完整性(PI)的基本概念、分析方法和應(yīng)用實例,幫助電子

2009-11-25 10:13:20

信號完整性資料

2015-09-18 17:26:36

就變得重要了,通常將這種情況稱為高頻領(lǐng)域或高速領(lǐng)域。這些術(shù)語意味著在那些互連線對信號不再透明的產(chǎn)品或系統(tǒng)中,如果不小心就會出現(xiàn)一種或多種信號完整性問題。

從廣義上講,信號完整性指的是在高速產(chǎn)品中由互連線引起的所有問題。它主要研究互連線與數(shù)字償號的電壓電流波形相互作用時其電氣特性參數(shù)如何影響產(chǎn)品的性能。

2023-09-28 08:18:07

很不錯的一本信號完整性教材。其實EMC、EMI問題最終都是信號完整性問題。

2011-12-09 22:49:23

信號完整性分析與設(shè)計信號完整性設(shè)計背景???什什么是信號完整D??信信號完整性設(shè)計內(nèi)è??典典型信號完整性問題與對2現(xiàn)在數(shù)字電路發(fā)展的趨ê??速速率越來越???芯芯片集成度越來越高£P(guān)C板板越來越

2009-09-12 10:20:03

信號完整性的定義信號完整性包含哪些內(nèi)容

2021-03-04 06:09:35

信號完整性基礎(chǔ)

2013-11-14 22:26:42

://pan.baidu.com/s/1jG0JbjK信號完整性小結(jié)1、信號完整性問題關(guān)心的是用什么樣的物理互連線才能確保芯片輸出信號的原始質(zhì)量。2、信號完整性問題一般分為四種:單一網(wǎng)絡(luò)的信號質(zhì)量、相鄰網(wǎng)絡(luò)間的串

2015-12-12 10:30:56

本文主要介紹信號完整性是什么,信號完整性包括哪些內(nèi)容,什么時候需要注意信號完整性問題?

2021-01-25 06:51:11

印制板)和系統(tǒng)的核心技術(shù)就是微波背景下的互連設(shè)計與信號完整性分析。全世界高速高密度電路的發(fā)展表明:互連正在取代器件,躍升為高速電路設(shè)計的主角。信號完整性分析是高速互連設(shè)計的支撐與保障。要想精通高速

2010-05-29 13:29:11

高速信號的電源完整性分析在電路設(shè)計中,設(shè)計好一個高質(zhì)量的高速PCB板,應(yīng)該從信號完整性(SI——Signal Integrity)和電源完整性 (PI——Power Integrity )兩個方面來

2012-08-02 22:18:58

完整性分析。全世界高速高密度電路的發(fā)展表明:互連正在取代器件,躍升為高速電路設(shè)計的主角。信號完整性分析是高速互連設(shè)計的支撐與保障。要想精通高速電路設(shè)計,就要對信號完整性具有深入的理解與掌握。 2008

2010-11-09 14:21:09

決方案。對于那些處理高復(fù)雜度電路板和系統(tǒng)的工程師來說,Innoveda的XTK信號完整性校驗工具組和ePlanner信號完整性規(guī)劃環(huán)境提供了用于超高速信號完整性分析的先進算法和一些成熟的驗證功能,包括拓撲

2018-09-10 16:37:21

高速PCB設(shè)計的信號完整性問題 隨著器件工作頻率越來越高,高速PCB設(shè)計所面臨的信號完整性等問題成爲傳統(tǒng)設(shè)計的一個瓶頸,工程師在設(shè)計出完整的解決方案上面臨越來越大的挑戰(zhàn)。盡管有關(guān)的高速仿真工具

2012-10-17 15:59:48

高速pcb的信號完整性問題主要有哪些?應(yīng)如何消除?

2023-04-11 15:06:07

高速數(shù)字設(shè)計和信號完整性

2019-06-11 22:46:02

關(guān)于信號完整性與高速電路設(shè)計不可多得的好東西。

2015-04-16 19:19:52

高速電路信號完整性分析與設(shè)計—信號完整性仿真仿真中有兩類信號可稱之為高速信號:高頻率的信號(>=50M)上升時間tr很短的信號:信號上升沿從20%~80%VCC的時間,一般是ns級或

2009-09-12 10:31:31

高速電路信號完整性分析與設(shè)計—PCB設(shè)計多層印制板分層及堆疊中應(yīng)遵徇的基本原則;電源平面應(yīng)盡量靠近接地平面。布線層應(yīng)安排與映象平面層相鄰。重要信號線應(yīng)緊臨地層。[hide] [/hide][此貼子已經(jīng)被作者于2009-9-12 10:38:14編輯過]

2009-09-12 10:37:02

高速電路信號完整性分析與設(shè)計—串擾串擾是由電磁耦合引起的,布線距離過近,導(dǎo)致彼此的電磁場相互影響串擾只發(fā)生在電磁場變換的情況下(信號的上升沿與下降沿)[此貼子已經(jīng)被作者于2009-9-12 10:32:03編輯過]

2009-09-12 10:31:08

高速IC(芯片)、PCB(電路印制板)和系統(tǒng)的核心技術(shù)就是微波背景下的互連設(shè)計與信號完整性分析。全世界高速高密度電路的發(fā)展表明:互連正在取代器件,躍升為高速電路設(shè)計的主角。信號完整性分析是高速互連

2010-04-21 17:11:35

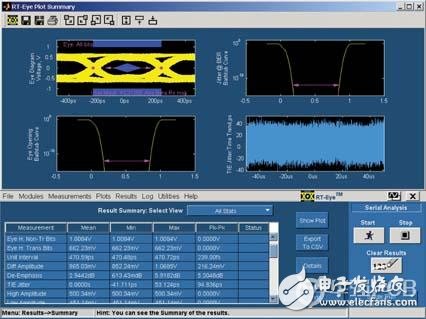

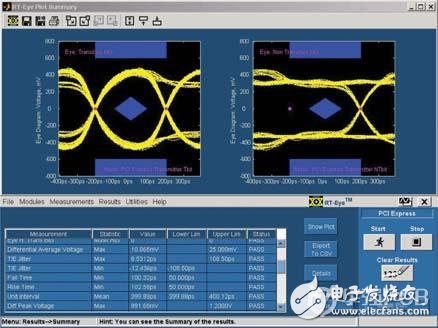

信號完整性設(shè)計在產(chǎn)品開發(fā)中越來越受到重視,而信號完整性的測試手段種類繁多,有頻域,也有時域的,還有一些綜合性的手段,比如誤碼測試。這些手段并非任何情況下都適合使用,都存在這樣那樣的局限性,合適選用,可以做到事半功倍,避免走彎路。

2019-08-26 06:32:33

在高速電路設(shè)計中信號完整性分析由于系統(tǒng)時鐘頻率和上升時間的增長,信號完整性設(shè)計變得越來越重要。不幸的是,絕大多數(shù)數(shù)字電路設(shè)計者并沒意識到信號完整性問題的重要性,或者是直到設(shè)計的最后階段才初步認識到

2009-10-14 09:32:02

高速數(shù)字硬件電路設(shè)計中信號完整性在通常設(shè)計的影響是什么?高速電路設(shè)計中信號完整性面臨的挑戰(zhàn)有哪些?怎么處理?

2021-04-22 06:26:55

本文分析了高速電路設(shè)計中的信號完整性問題,提出了改善信號完整性的一些措施,并結(jié)合一個VGA視頻分配器系統(tǒng)的設(shè)計過程,具體分析了改善信號完整性的方法。

2021-06-03 06:22:05

本文分析了高速電路設(shè)計中的信號完整性問題,提出了改善信號完整性的一些措施,并結(jié)合一個VGA視頻分配器系統(tǒng)的設(shè)計過程,具體分析了改善信號完整性的方法。

2021-06-04 06:16:07

Cadenc高速電路設(shè)計SI PI 信號完整性電源完整性仿真視頻教程下載鏈接地址:鏈接:http://pan.baidu.com/s/1pJiPpzl密碼:3yjv

2015-07-30 21:44:10

電阻的放置 高速PCB信號完整性仿真分析 信號完整性的電路板設(shè)計準則 基于信號完整性分析的高速數(shù)字PCB的設(shè)計方法 LVDS(低電壓差分信號)原理分析 阻抗匹配與史密斯(Smith)圓圖:基本原理

2008-12-25 09:49:59

確定該電路具有較好的信號完整性。反之,當信號不能正常響應(yīng)時,就出現(xiàn)了信號完整性問題。 高速PCB的信號完整性問題主要包括信號反射、串擾、信號延遲和時序錯誤。 · 反射:信號在傳輸線上傳輸時,當高速

2018-11-27 15:22:34

比較直接的結(jié)果是從信號完整性上表現(xiàn)出來的,但我們絕不能因此忽略了電源完整性設(shè)計。因為電源完整性直接影響最終PCB板的信號完整性。電源完整性和信號完整性二者是密切關(guān)聯(lián)的,而且很多情況下,影響信號畸變的主要...

2021-12-28 07:48:43

VNA是如何測量高速器件的信號完整性(SI)?

2021-05-11 06:49:40

高速數(shù)字系統(tǒng)中,Altium designer 進行信號完整性分析技巧,

2017-03-20 15:43:02

問題:[單選] 驗證消息完整性的方法是()A . 大嘴青蛙認證協(xié)議B . 數(shù)字簽名C . 基于公鑰的認證D . 消息摘要交通標線是主要的交通安全設(shè)施之一,其主要作用是管制和引導(dǎo)交通,下列設(shè)施屬于交通

2021-06-30 06:18:06

信號完整性領(lǐng)域,包括基本原理、測量技術(shù)和分析工具等方面舉辦過多期短期課程,目前為GigaTest實驗室首席技術(shù)主管。李玉山,西安電子科技大學(xué)教授,教育部“超高速電路設(shè)計與電磁兼容”重點實驗室學(xué)術(shù)委員會

2017-08-08 18:03:31

省部級獎勵10項。在IEEE Trans.上發(fā)表長文12篇;正式出版教材/專著/譯著12部。研究方向:高速電路設(shè)計與信號完整性分析,EDA技術(shù)及軟件研發(fā)。目錄第1章信號完整性分析概論 1.1信號完整性

2017-09-19 18:21:05

數(shù)字和模擬設(shè)計技術(shù),對數(shù)字電路設(shè)計人員提高設(shè)計技能、縮短其產(chǎn)品的開發(fā)周期、精通信號完整性技術(shù)等都大有裨益。《高速數(shù)字設(shè)計》將理論與實踐方法相結(jié)合,適合從事模擬和數(shù)字電路設(shè)計的相關(guān)人員使用,可作為大專院校

2017-09-20 18:30:27

,USB2.0傳輸速度為高速480Mb/s。 對于USB信號的傳輸,信號完整性是核心指標。USB總線應(yīng)用差分信號傳輸數(shù)據(jù),在傳輸過程采用NRZI編碼。在上位機與USB設(shè)備的交互中,根據(jù)數(shù)據(jù)傳輸雙工或

2019-07-12 06:00:00

、鉆孔數(shù)據(jù)文件。 后仿真驗證: 信號完整性(SI)后仿真,電源完整性(PI)后仿真,電磁兼容性(EMI)后仿真。 以下將逐個介紹如何在Cadence的高速設(shè)計流程中實現(xiàn)這些仿真條件,通過仿真分析,得到

2019-11-19 19:14:25

高速板還是低速板或多或少都會涉及信號完整性問題。仿真或者guideline的確可以解決部分問題,但無法覆蓋全部風(fēng)險點,對高危風(fēng)險點失去控制經(jīng)常導(dǎo)致設(shè)計失敗,保證設(shè)計成功需要系統(tǒng)化的設(shè)計方法。許多工程師

2016-05-05 14:26:26

首先我們定義下什么是電源和信號完整性?信號完整性 信號完整性(SI)分析集中在發(fā)射機、參考時鐘、信道和接收機在誤碼率(BER)方面的性能。電源完整性(PI)側(cè)重于電源分配網(wǎng)絡(luò) (PDN) 提供恒定

2021-12-30 06:33:36

何為信號完整性:信號完整性(Signal Integrity,簡稱SI)是指在信號線上的信號質(zhì)量。差的信號完整性不是由某一單一因素導(dǎo)致的,而是板級設(shè)計中多種因素共同引起的。當電路中信號能以要求的時序

2021-12-30 08:15:58

在高速設(shè)計中,如何解決信號的完整性問題?

2009-09-06 08:42:10

采取有效的控制措施,提高電路設(shè)計質(zhì)量,是必須考慮的問題。借助功能強大的Cadence公司SPEECTRAQuest仿真軟件,利用IBIS模型,對高速信號進行信號完整性仿真分析是一種高效可行的分析方法

2015-01-07 11:30:40

本文介紹了一種基于信號完整性計算機分析的高速數(shù)字信號PCB板的設(shè)計方法。在這種設(shè)計方法中,首先將對所有的高速數(shù)字信號建立起PCB板級的信號傳輸模型,然后通過對信號完整性的計算分析來尋找設(shè)計的解

2018-08-29 16:28:48

本文介紹了一種基于信號完整性計算機分析的高速數(shù)字信號PCB板的設(shè)計方法。在這種設(shè)計方法中,首先將對所有的高速數(shù)字信號建立起PCB板級的信號傳輸模型,然后通過對信號完整性的計算分析來尋找設(shè)計的解

2008-06-14 09:14:27

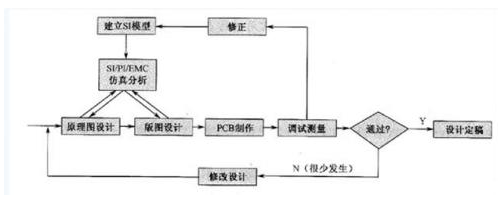

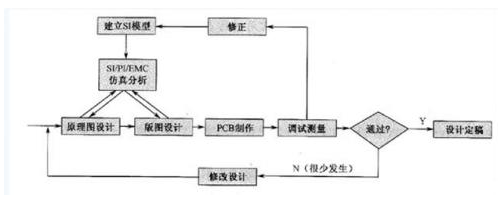

基于信號完整性分析的PCB設(shè)計流程如圖所示。 主要包含以下步驟: 圖 基于信號完整性分析的高速PCB設(shè)計流程 (1)因為整個設(shè)計流程是基于信號完整性分析的,所以在進行PCB設(shè)計之前,必須建立

2018-09-03 11:18:54

如何保證脈沖信號傳輸?shù)?b class="flag-6" style="color: red">完整性,減少信號在傳輸過程中產(chǎn)生的反射和失真,已成為當前高速電路設(shè)計中不可忽視的問題。

2021-04-07 06:53:25

本文從高速數(shù)字電路中信號線的實際電氣特性出發(fā),建立電氣特性模型,尋找影響信號完整性的主要原因及解決問題的方法,給出布線中應(yīng)該注意的問題和遵循的方法和技巧。

2021-04-26 06:45:29

常值得注意的問題。本文首先介紹了PCB信號完整性的問題,其次闡述了PCB信號完整性的步驟,最后介紹了如何確保PCB設(shè)計信號完整性的方法。PCB信號完整性的問題包括:PCB的信號完整性問題主要包括信號

2018-07-31 17:12:43

高速數(shù)字PCB設(shè)計信號完整性解決方法

2021-03-29 08:12:25

何為信號完整性?信號完整性包括哪些?干擾信號完整性的因素有哪些?如何去解決?

2021-05-06 07:00:23

今天跟大家分享下浙江大學(xué)原創(chuàng)的“高速設(shè)計講義”(如有侵權(quán)請告知),內(nèi)含設(shè)計方法、信號完整性、板級高速時序分析!{:19:}

2016-08-17 14:14:57

高速PCB頻發(fā)故障,使得信號完整性問題越來越受到工程師的重視。有關(guān)高速PCB信號完整性的相關(guān)內(nèi)容網(wǎng)絡(luò)上有很多,這方面的知識點很容易找到資源學(xué)習(xí),我本人也寫過一本拙作《信號完整性揭秘》。但是,學(xué)習(xí)理論

2017-06-23 11:52:11

完整性的旅程中,以上為大家系統(tǒng)地梳理了其在硬件設(shè)計中的核心地位。從總線協(xié)議到PCB設(shè)計,從材料選擇到高速互連器件的理解,每一個環(huán)節(jié)都彰顯著信號完整性的重要性。而測試測量與仿真軟件的應(yīng)用,更是為信號完整性

2024-03-05 17:16:39

完整性。 信號完整性影響著許多電子設(shè)計學(xué)科。直到幾年前,它對數(shù)字設(shè)計人員來說還不算大問題。設(shè)計人員可以依賴邏輯電路,像布爾電路一樣操作。當時有噪聲的、不確定的信號發(fā)生在高速電路中,RF設(shè)計人員還不用擔(dān)心

2016-03-02 14:57:52

信號完整性與電源完整性分析信號完整性(SI)和電源完整性(PI)是兩種不同但領(lǐng)域相關(guān)的分析,涉及數(shù)字電路正確操作。在信號完整性中,重點是確保傳輸?shù)?在接收器中看起來就像 1(對0同樣如此)。在電源

2021-11-15 06:31:24

如何快速解決高速系統(tǒng)的信號完整性問題?

2021-04-27 06:03:49

高速電路信號完整性分析之應(yīng)用篇

2006-05-28 01:00:47 0

0 本文介紹了一種基于信號完整性計算機分析的高速數(shù)字信號 PCB板的設(shè)計方法。在這種設(shè)計方法中,首先將對所有的高速數(shù)字信號建立起PCB板級的信號傳輸模型,然后通過對信號完

2009-04-25 16:49:13 37

37 高速電路信號完整性分析與設(shè)計—信號完整性仿真:仿真信號仿真中有兩類信號可稱之為高速信號:高頻率的信號(>=50M)上升時間tr很短的信號:信號上

2009-10-06 11:19:50 0

0 高速并行總線信號完整性測試技術(shù):隨著信號速度的顯著提高,信號完整性問題已經(jīng)成為高速數(shù)字設(shè)計中的關(guān)鍵。本文介紹了一種新的信號完整性分析技術(shù),通過集成邏輯分析儀和

2009-10-17 17:11:55 0

0 高速并行總線信號完整性測試技術(shù)張楷 泰克科技(中國)有限公司摘要:隨著信號速度的顯著提高,信號完整性問題已經(jīng)成為高速數(shù)字設(shè)計中的關(guān)鍵。本文介紹了一種新的信

2009-12-17 14:38:21 23

23 高速串行信號的信號完整性和物理層測量與分析-High Speed Design Testing Solutions

AgendaHigh-Speed Serial Test

2010-06-29 16:18:31 26

26 在高速設(shè)計中,如何解決信號的完整性問題?

信號完整性基本上是阻抗匹配的問題。而影響阻抗匹配的因素有信號源的架構(gòu)和輸出阻

2010-01-02 11:15:06 1097

1097

2.1 基本電磁理論 本書主要討論高速數(shù)字電路中信號完整性分析與高速電路設(shè)計的基本方法,而信號完整性分析是以電磁場理論作為基本理論,因此必須首先討論高速信號完整性所涉及

2012-05-25 16:26:07 102

102 2.1 基本電磁理論 本書主要討論高速數(shù)字電路中信號完整性分析與高速電路設(shè)計的基本方法,而信號完整性分析是以電磁場理論作為基本理論,因此必須首先討論高速信號完整性所涉及

2012-05-25 16:21:42 1639

1639 在電路設(shè)計中,設(shè)計好一個高質(zhì)量的高速PCB板,應(yīng)該從信號完整性(SISignal Integrity)和電源完整性 (PIPower Integrity )兩個方面來考慮。盡管從信號完整性上表現(xiàn)出來的結(jié)果較為直接,但是信

2012-05-29 13:51:26 2498

2498 高速信號完整性測試和驗證技術(shù)

2017-01-14 02:53:59 23

23 高速電路信號完整性分析與設(shè)計 超清書簽版

2017-09-19 09:11:25 0

0 描述了高速PCB電路板信號完整性設(shè)計方法。 介紹了信號完整性基本理論, 重點討論了如何采用高速PCB設(shè)計方法保證高速數(shù)采模塊的信號完整性

2017-11-08 16:55:13 0

0 在設(shè)計、驗證和故障排除等領(lǐng)域, 串行總線 技術(shù)對高性能示波器的性能提出了更高的標準。在這一系列更高的標準當中,高速數(shù)據(jù)速率只是一個起點,設(shè)計人員還需一套工具以支持關(guān)鍵 信號完整性 測量和眼圖分析。

2018-02-07 18:10:53 724

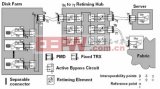

724 隨著第三代I/O技術(shù)的出現(xiàn),人們開始步入高速傳輸?shù)臅r代。在使用PCI Express、SATA等高速串行總線時,如何保持信號的完整性是一個挑戰(zhàn)。本文結(jié)合實例,介紹信號完整性驗證的基礎(chǔ)知識和方法。

2018-02-26 15:36:24 2173

2173

借助功能強大的Cadence公司SPEECTRAQuest仿真軟件,利用IBIS模型,對高速信號進行信號完整性仿真分析是一種高效可行的分析方法,可以發(fā)現(xiàn)信號完整性問題,根據(jù)仿真結(jié)果在信號完整性相關(guān)問題上做出優(yōu)化的設(shè)計,從而達到提高設(shè)計質(zhì)量,縮短設(shè)計周期的目的。

2019-05-20 15:25:37 1098

1098

(1)因為整個設(shè)計流程是基于信號完整性分析的,所以在進行PCB設(shè)計之前,必須建立或獲取高速數(shù)字信號傳輸系統(tǒng)各個環(huán)節(jié)的信號完整性模型。

(2)在設(shè)計原理圖過程中,利用信號完整性模型對關(guān)鍵網(wǎng)絡(luò)進行信號完整性預(yù)分析,依據(jù)分析結(jié)果來選擇合適的元器件參數(shù)和電路拓撲結(jié)構(gòu)等。

2019-10-11 14:52:33 2023

2023

高速電路信號完整性分析與設(shè)計—調(diào)試技巧

2022-02-10 13:56:45 6

6 高速電路信號完整性分析與設(shè)計—串擾

2022-02-10 17:23:04 0

0 高速電路信號完整性分析與設(shè)計—信號完整性仿真

2022-02-10 17:29:52 0

0 在高速設(shè)計中,如何解決信號的完整性問題? 在高速設(shè)計中,信號完整性問題是一個至關(guān)重要的考慮因素。它涉及信號在整個設(shè)計系統(tǒng)中的傳輸、接收和響應(yīng)過程中是否能夠維持其原始形態(tài)和性能指標。信號完整性問題可能

2023-11-24 14:32:28 227

227

電子發(fā)燒友App

電子發(fā)燒友App

評論