提高處理器主頻可以提高處理器的性能,但是到一定程度就不能再提高了,我們需要通過雙核,或者多核來提高處理器的性能。

2024-01-24 09:59:00 512

512

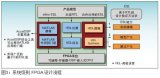

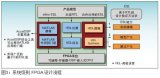

FPGA在高性能數字信號處理領域越來越受關注,如無線基站。在這些應用中, FPGAs通常被用來和DSP處理器并行工作。有更多的選擇當然是好的,但這也意味著系統設計師需要一個確切的FPGAs及高端DSP信號處理器性能參數圖。不幸的是,常用的參數圖在這種情況下都是不可靠的。

2019-09-25 08:17:27

(Intel-Integrated Circuit bus)。1998 年當推出 I2C 總線協議 2.0 版本時,I2C 協議實際上已經成為一個國際標準。在進行 FPGA 設計時,經常需要和外圍提供 I2C 接口的芯片通信

2018-09-29 09:37:11

的高性能采集、回放以及相關處理。通過扣接不同的數據接口FMC子卡的方式,可實現不同采樣頻率、不同量化位數、不同通道數、不同信號形式的采集、回放、處理的功能模塊。高性能VPX信號處理板主要包含大規模FPGA

2019-09-06 10:15:41

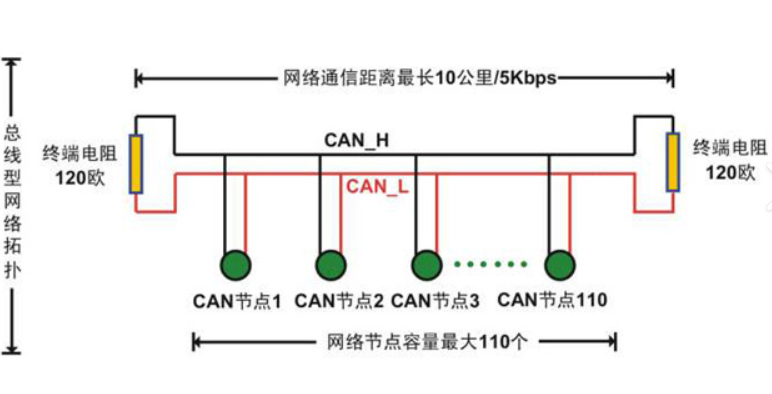

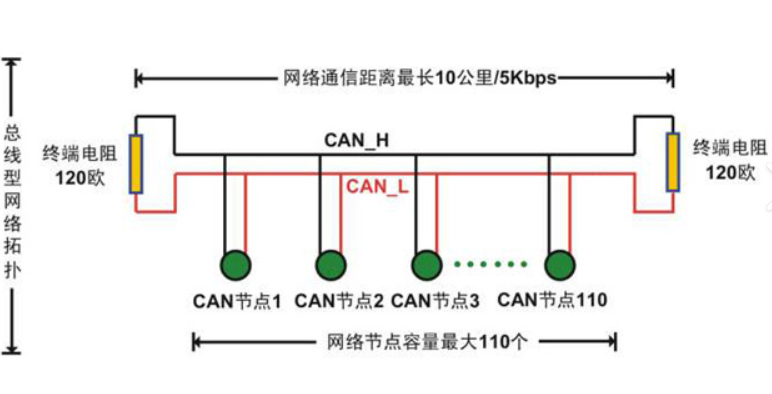

請教一下,CAN總線的問題,目前有個項目,總結點數大概在200個左右,一根總線的話總長度在400米左右。看了兩款CAN總線驅動器TJA1050T和MCP2551,最大節點數好像都只有110個左右

2015-07-18 16:23:23

常聽到一句話“汽車上都用CAN總線,那這個總線的穩定性應該是有所保障的”,而這種穩定性的保障,正是因為CAN總線直面了現場總線的復雜環境,做了相應的錯誤處理以及故障界定。工業現場總線的應用環境

2021-08-23 09:25:27

本人在北京工作7年以上,從事FPGA外圍接口設計,非常熟悉Serial RapidIO協議,設計調試了多個基于Serial RapidIO接口的DSP和PowerPC信號處理卡.本人非常

2014-08-23 13:27:47

定的綁定。由于有兩種 Rapidio 發射器類型(長跑和短跑),我們猜測將發射器配置為長跑可能會提高信號質量,但不幸的是我們沒有找到合適的寄存器,順便說一句,我們使用 MPC8569。我的問題:是否有配置 Rapidio 變送器類型的寄存器?或者是否有一些與硬件設計相關的問題可能會導致我們的問題?

2023-03-16 08:37:11

VARON是一款AXI性能分析工具。VARON幫助對AXI總線進行性能分析,該總線用于FPGA/ASIC設計的各個階段,如架構、RTL設計、原型濾波網絡等。 VARON捕獲AXI總線信號和可視化

2020-11-02 16:54:39

(Controller Area Network控制器局域網)以其高性能、高可靠性以及獨特的設計等優點,為分布式控制系統實現各節點之間實時、可靠的數據通信提供了強有力的支持。CAN總線突出的可靠性、實時性和靈活性顯示了它

2019-06-28 08:24:19

一、板卡概述

板卡基于6U VPX標準結構,北京太速科技板卡包含一個C6678 DSP芯片,一個XCVU9P 高性能FPGA,雙路HPC FMC。二、處理板技術指標

?DSP處理器采用TI 8核

2023-10-16 11:12:06

本文提出一種基于LPC2294微控制器,使用μCLinux作為操作系統的CAN主節點軟硬件設計方案。主節點通過擴展SRAM、FLASH提高了系統的性能,采用帶隔離功能的CAN收發器增強了CAN總線節點的抗干擾能力,外接以太網控制器實現了計算機遠程監控。

2021-05-25 06:59:34

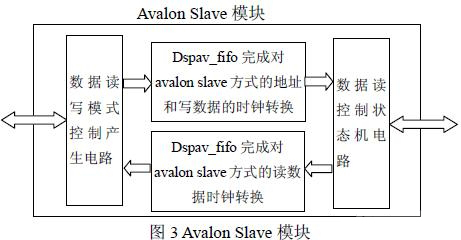

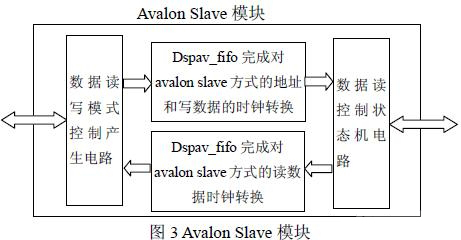

功能。基于FPGA的SOPC技術,軟件算法修改和硬件平臺結構調整都是在線可編程的,其靈活性和可靠性是其他單片微處理器無法比擬的。本文采用ALTERA公司提供的SOPC技術,研究傳感器的非線性軟件校正

2018-11-01 17:24:56

摘 要: 為了提高航空航天領域對信號處理、傳輸的實時性及可靠性,以CycloneIII系列EP3C40F324I7為核心處理器,設計了一種基于CPCI總線的多功能通信卡。結合高效的FPGA算法

2016-01-14 10:59:18

Andrei Cozma 和 Eric Cigan簡介電機在各種工業、汽車和商業領域應用廣泛。電機由驅動器控制,驅動器通過改變輸入功率來控制其轉矩、速度和位置。高性能電機驅動器可以提高效率,實現更快

2018-10-19 10:43:22

Andrei Cozma和Eric Cigan簡介電機在各種工業、汽車和商業領域應用廣泛。電機由驅動器控制,驅動器通過改變輸入功率來控制其轉矩、速度和位置。高性能電機驅動器可以提高效率,實現更快

2018-10-10 18:00:43

作者:Rob Taylor ,譯者:馬卓奇本文要點FPGA 能夠滿足全球范圍以指數式增長的人工智能和大數據的性能需求。FPGA 通過同時運行大量的進程和優化管理數據流來提高處理速度,并降低硬件成本

2019-07-24 07:29:03

的基于Nios軟CPU內核的FPGA非線性校正方案,具有集成度高、靈活性強、調試方便的優點,而且在DAB小功率實驗發射系統中進行了實測,信噪比提高了12dB,非線性補償效果較為理想。

2018-07-30 18:09:06

的獨立性,具有工作可靠性、性能穩定、測量精確、安裝調試方便、造價低廉等特點。圖1 分布式溫度測量節點結構框圖 2 溫度測量節點的硬件電路設計 CAN總線溫度測量節點主要任務是溫度采集與CAN通信,其硬件

2018-11-13 10:38:08

的PicoBlaze和MicroBlaze等,使得目前的許多系統的主要功能都可以由大容量的FPGA實現,而無需再使用比較昂貴的高性能微處理器。

2019-09-24 07:15:00

我們可以做什么測試線性(INL)的12位SAR ADC與正弦信號源,只有10位DAC?簡單地說,如何提高10位DAC源的線性性能?贊賞你的評論謝謝 以上來自于百度翻譯 以下為原文What can

2019-07-05 06:00:17

本文基于Viitex-5 LX110驗證平臺的設計,探索了高性能FPGA硬件系統設計的一般性方法及流程,以提高FPGA的系統性能。

2021-04-26 06:43:55

如何提高FATFS SD性能?

2022-02-11 06:28:46

如何提高VMMK器件的性能?

2021-05-21 06:35:39

無論您的系統是用于無線通信、雷達,還是 EMI/EMC 測試,系統的性能水平都是由其中的天線決定的。系統天線的性能決定了系統的整體質量,最終可能會影響整個程序或應用軟件的效率。本文介紹了 5 個旨在幫助您提高天線性能的關鍵要點。

2021-02-24 07:24:14

有什么方法可以提高無線系統中信號處理功能的性能呢?

2021-04-29 06:16:07

我正在使用 iMX8mmini 并嘗試提高 GPU 性能。使用下面的命令我發現當前 GPU 以 500 MHz 的頻率運行。根據數據表或設備樹節點,GPU 以 800 MHz 的標稱頻率運行(最大

2023-04-18 07:17:15

收發器系列,該系列包括業界尺寸最小和性能最強大的PROFIBUS收發器。本文還將展示如何保護隔離總線節點免受ESD、EFT和瞬間浪涌的影響。

2021-03-08 08:26:32

在項目的特殊環境要求下, CAN總線通信要求使用FPGA作為系統中的主控制器, 較之傳統設計使用的單片機, FPGA能夠在速度和體積上有更好的適應性。

2019-09-26 06:57:07

通過FPGA來構建一個低成本、高性能、開放架構的數據平面引擎可以為網絡安全設備提供性能提高的動力。隨著互聯網技術的飛速發展,性能成為制約網絡處理的一大瓶頸問題。FPGA作為一種高速可編程器件,為網絡安全流量處理提供了一條低成本、高性能的解決之道。

2019-08-12 08:13:53

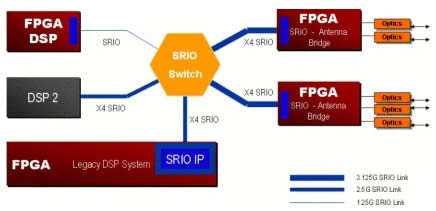

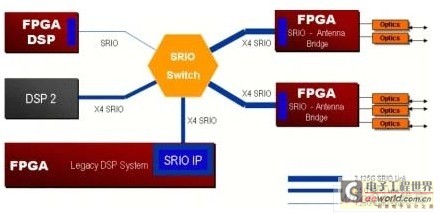

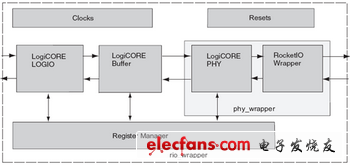

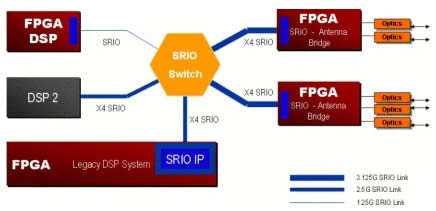

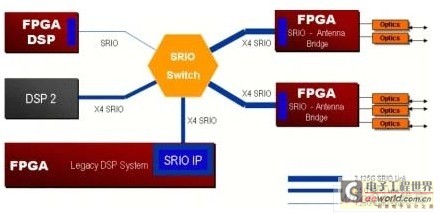

運算平臺之間是如何連接的?SRIO系統的應用實例有哪些?如何利用串行RapidIO去實現FPGA協處理?

2021-04-29 06:17:59

要跟上日益提高的性能需求,還得注意保持成本低廉有效利用基于串行RapidIO的FPGA作為DSP協處理器就能達到這些目的。那么,我們該怎么做呢?

2019-08-07 06:47:06

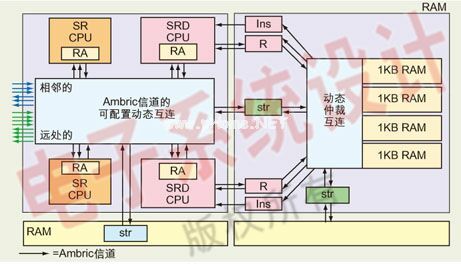

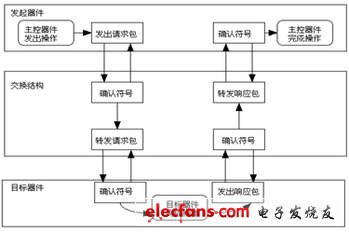

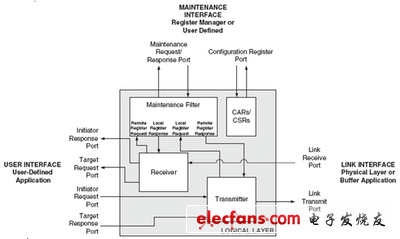

隨著通訊系統的數據處理量日益增大,過去總線形式的體系結構逐漸成為約束處理能力進一步提升的瓶頸。本文首先簡單介紹了嵌入式設計中總線結構的演化過程,從而引出新一代點對點串行交換結構RapidIO。

2019-11-01 06:05:21

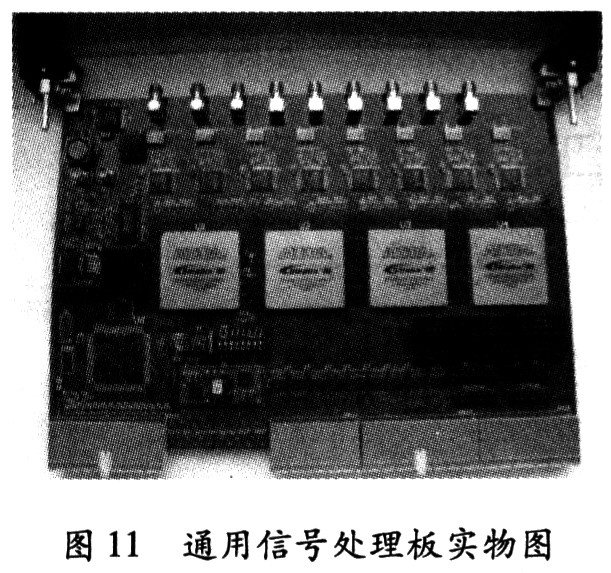

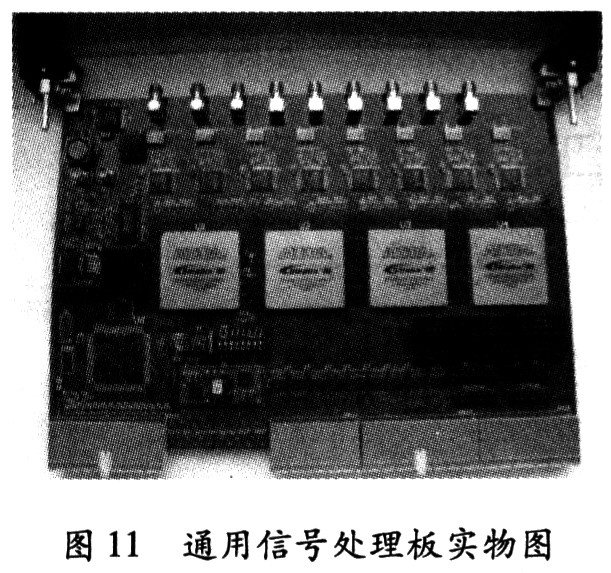

文中采用Ahera公司最新、具有最佳性能、最大密度和最低功耗的高端FPGA StratixⅢ設計了基于CPCI總線的通用FPGA信號處理板,并在某雷達系統中進行了實際應用。

2021-05-07 06:54:25

您可以顯著提高無線系統中信號處理功能的性能。怎樣提高呢?有效方法是利用FPGA結構的靈活性和目前受益于并行處理的FPGA架構中的嵌入式DSP模塊。

2019-10-23 07:04:22

您可以顯著提高無線系統中信號處理功能的性能。怎樣提高呢?有效方法是利用FPGA結構的靈活性和目前受益于并行處理的FPGA架構中的嵌入式DSP模塊。

2019-08-15 07:51:10

隨著通訊系統的數據處理量日益增大,過去總線形式的體系結構逐漸成為約束處理能力進一步提升的瓶頸。本文首先簡單介紹了嵌入式設計中總線結構的演化過程,從而引出新一代點對點串行交換結構RapidIO。

2019-09-02 07:10:22

本文討論了一種基于RapidIO的具有雙主機節點的嵌入式系統互聯設計,給出系統設計方案及驅動軟件設計,并在具體應用環境中對設計方案進行了系統驗證。

2021-05-24 06:24:37

高線性性能的評估和實現挑戰

2021-04-06 07:10:32

您可以顯著提高無線系統中信號處理功能的性能。怎樣提高呢?有效方法是利用FPGA結構的靈活性和目前受益于并行處理的FPGA架構中的嵌入式DSP模塊。

2019-09-19 07:50:50

隨著人們對于環境監測要求的不斷提高,無線傳感器網絡技術以其投資成本低、架設方便、可靠性高的性能優勢得到了比較廣泛的應用。由于無線傳感器網絡節點需要實現采集、處理、通信等多個功能,因此硬件上采用模塊化設計可以大大提高網絡節點的穩定性和安全性。

2019-10-30 06:29:05

是德科技RapidIO總線數字調試解決方案

2019-08-02 12:42:32

本文介紹了一種基于FPGA芯片的高速智能節點的硬件結構和軟件設計,旨在提高現在LON網絡的智能節點的處理能力和通用性。

2021-05-06 08:20:28

高級處理器特性能否提高編碼效率?

2021-04-26 06:41:08

針對傳統總線PCI存在的問題,提出異步FIFO存儲轉發模式的串行RapidIO-PCI轉接橋方案,介紹RapidIO高速總線的體系結構及其性能優勢,根據PCI和RapidIO協議,給出轉接橋關鍵部分結構的設

2009-04-01 09:34:02 33

33 基于FPGA的PCI總線接口設計::PCI是一種高性能的局部總線規范,可實現各種功能標準的PCI總線卡。本文簡要介紹了PCI總線的特點、信號與命令,提出了一種利用高速FPGA實現PCI總線接

2009-06-25 08:17:18 48

48 多節點大容量FPGA系統的遠程升級方法:針對目前廣泛使用的以大容量FPGA 實現主要功能的多節點系統的遠程升級問題,提出了一種基于ATmega64 單片機和RS485 總線以及接入以太網的主控

2009-11-20 17:42:26 17

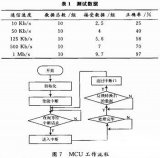

17 CAN總線是一種應用廣泛的實時性現場總線,提出了基于具有ARM7TDMI內核的32位微控制器的CAN總線智能節點設計方案。詳細介紹了ARM控制器(LPC2294)的特點、智能節點的結構以及系統軟

2009-12-01 14:27:35 18

18 RapidIO 互連構架是一個開放的標準,可應用于連接多處理器、存儲器和通用計算平臺。本文簡要介紹了基于Tundra 公司TSI568 芯片的RapidIO 交換模塊的設計原理和實現方法,并對一些

2010-01-06 16:47:48 40

40 本文首先簡單的介紹了總線的發展,從而引出一種新型的串行點對點交換結構RapidIO。DSP 在高性能處理系統中的重要性毋庸置疑,但是目前的很多DSP 并沒有RapidIO接口。本文提出了

2010-01-25 14:25:19 32

32 基于FPGA 的LON 網絡高速智能節點的設計作者:王傳云楊輝 來源:微計算機信息摘要:本文介紹了一種基于FPGA 芯片的高速智能節點的硬件結構和軟件設計,旨在提高現在LON 網絡的

2010-02-06 12:17:38 16

16 分析當前高速互連網絡中同時存在的TCP/IP, GAMMA, InfiniBand, SCI 等技術的實現機制,介紹RapidIO 高性能總線技術。研究RapidIO 協議和MPC8548 處理器的相關技術,提出在RapidIO 高速互連網

2010-09-22 08:35:11 20

20 摘 要 :PCI是一種高性能的局部總線規范,可實現各種功能標準的PCI總線卡。本文簡要介紹了PCI總線的特點、信號與命令,提出了一種利用高速FPGA實現PCI總線接口的

2009-06-20 13:13:28 936

936

基于CPCI總線的通用FPGA信號處理板的設計

?隨著雷達信號處理技術的不斷發展以及現代國防對雷達技術的需求,系統對雷達信號處理的要求也越來越高,需要實時處

2009-11-28 15:07:38 922

922

基于FPGA實現DSP與RapidIO網絡互聯

1. 引言

隨著通訊系統的數據處理量日益增大,過去總線形式的體系結構逐漸成為約束處理能力進一步提升的瓶頸。本文首

2010-02-25 16:46:46 867

867

利用串行RapidIO實現FPGA協處理

為了支持“三重播放”應用,人們對高速通信和超快速計算的需求日益增大,這向系統開發師、算法開發師和硬件工程師等人員提出了新

2010-02-25 17:06:55 1216

1216

用RapidIO提高DSP陣列的性能

“采用SERDES(串行/解串器)技術后只需少量引腳就能獲得很高的帶寬。由于硬件全部承擔了協議棧的處理,RapidIO減少了原來僅用于在系統中傳

2010-03-01 10:36:39 1318

1318

利用串行RapidIO實現FPGA協處理

為了支持“三重播放”應用,人們對高速通信和超快速計算的需求日益增大,這向系統開發師

2010-03-25 14:48:25 1389

1389

RapidIO總線的出現及其體系結構和應用

傳統總線多采用并線總線的工作方式,這類總線一般分為三

2010-12-06 10:16:37 2069

2069 為提高LonWorks總線的控制能力, 設計了以單片機AT89S51為主的處理器、神經元芯片MC143150為從處理器的LonWorks節點, 主處理器和從處理器之間的接口采用I2C通信總線, 節省了神經元芯片的I/

2011-05-18 16:38:57 18

18 該方案采用Altera公司的IP核和Cyclone系列FPGA,建立了串行RapidIO(SRIO)接口通信系統,并對其功能進行驗證。詳細分析了RapidIO應用系統及其驗證模型的功能結構和運行原理,為提高嵌入式

2011-12-23 14:47:22 38

38 基于對CAN 總線控制器的功能分析, 并應用Verilog語言進行軟件設計, 從而實現CAN節點之間的通信功能。

2012-04-28 09:56:54 13818

13818

儀器總線性能——理解儀器控制中的競爭的總線技術,本書提供了一個關于構建模塊化、軟件定義RF平臺的案例研究

2012-07-16 12:21:49 1053

1053 應用51單片機為控制核心結合其他的器件設計了一種能連接于CAN總線上的智能節點。通過單片機控制CAN總線控制器SJA1000,并進一步通過CAN總線收發器PCA82C250,實現該智能節點與CAN總線的

2013-01-10 16:54:57 120

120 介紹了RapidIo總線的特點,以及RapidIo總線初始化過程中面臨的系統網絡結構探測和最短路徑路由選擇問題。針對該問題,本文研究了深度優先(DFS)網絡拓撲探測方法在RapidIo總線枚舉過

2013-03-13 16:15:14 74

74 基于FPGA的系統提高電機控制性能 。

2016-01-07 15:00:19 24

24 CAN總線通訊已經從汽車電子行業逐漸向各行各業鋪開使用了,例如軌道交通、礦井監控等。在設計CAN總線接口電路時需要注意,

對于提高CAN總線節點的可靠性而言,離不開隔離、總線阻抗匹配、總線保護等,在設計CAN節點時要注意這些點以提高總線電路可靠性和安全性。

2016-06-08 11:41:27 2862

2862 基于FPGA的1024點高性能FFT處理器的設計_鐘冠文

2017-03-19 11:36:55 10

10 基于FPGA和多DSP的多總線并行處理器設計

2017-10-19 13:40:31 4

4 為提高集成架構中車電總線通信速率,結合綜合化處理系統項目要求,采用雙總線結合的方式,利用CAN總線和FlexRay總線實現功能及搭配上的互補,提出一種基于現場可編程門陣列(FPGA)的總線接口單元

2017-11-18 07:25:44 9023

9023

為了擴展VME總線和CAN總線的應用范圍,充分利用兩種總線的不同傳輸特點,采用了模塊設計方法,提出一種基于FPGA和MCU的總線轉換方案。該方案給出了FPGA與上位VME總線部分的VME總線接口

2018-07-17 10:11:00 3239

3239

您可以顯著提高無線系統中信號處理功能的性能。怎樣提高呢?有效方法是利用FPGA結構的靈活性和目前受益于并行處理的FPGA架構中的嵌入式DSP模塊。

2018-07-17 11:48:00 710

710

高性能 DSP 上的串行 RapidIO 接口

2018-06-12 03:44:00 3780

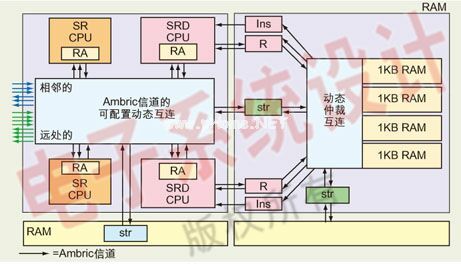

3780 隨著嵌入式系統對信號處理性能和數據傳輸性能的不斷提高,單純依靠提高處理器性能來改善系統性能的方法已無法滿足需求。并行計算正日益成為一種增加系統處理能力的可行方向,多處理器間的數據傳輸、資源共享與同步

2020-02-04 11:55:00 1995

1995

總線關閉是CAN節點比較重要的錯誤處理機制。在總線關閉狀態下,CAN節點的恢復流程是怎樣的?如何理解節點恢復流程的“快恢復”和“慢恢復”機制?本文將為大家詳細分析總線關閉及恢復的機制和原理。

2020-06-09 16:30:14 4047

4047 CAN總線節點軟件的設計與實現說明。

2021-04-19 16:59:10 20

20 RapidIO互連架構,與目前大多數流行的集成通信處理器、主機處理器和網絡數字信號處理器兼容,是一種高性能、包交換的互連技術。它能夠滿足高性能嵌入式工業在系統內部互連中對可靠性、增加帶寬,和更快的總線速度的需求。

2023-01-09 09:25:20 750

750 RapidIO 與傳統嵌入互連方式的比較 ????隨著高性能嵌入式系統的不斷發展,芯片間及板間互連對帶寬、成本、靈活性及可靠性的要求越來越高,傳統的互連方式,如處理器總線、PCI總線和以太網,都難以

2023-02-02 14:15:05 356

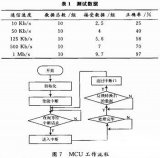

356 一般來說,CAN總線2可以掛載的節點數量10到110之間。下面采用了64個節點測試數據傳輸的性能,出現的問題如下。

2023-06-14 09:42:23 1191

1191

點擊上方 藍字 關注我們 摘要:以FPGA 代替傳統的單片機和外圍擴展芯片, 給出了CAN 總線通信節點的詳細設計方案。其中以SJA1000為CAN 總線控制器、FPGA 為主控制器, 設計實現通信

2023-06-18 11:15:01 1796

1796 。本文將深入探討訊維分布式節點的性能優勢,為讀者全面介紹這種技術架構的魅力。 一、高并發處理能力 訊維分布式節點通過將任務分配到多個節點上進行處理,大大提高了并發處理能力。與傳統的集中式計算架構相比,訊維分

2023-08-23 15:32:19 1006

1006 RapidIO交換芯片是一種基于RapidIO協議的專用交換芯片,它能夠實現高速、低延遲的數據傳輸和交換,廣泛應用于嵌入式系統、數據中心、網絡通信等領域。RapidIO協議本身是一種基于包交換的互連技術,具有高速、高效、可靠等特點,因此RapidIO交換芯片在數據傳輸和交換方面具有很高的性能優勢。

2024-03-16 16:40:09 1532

1532

電子發燒友App

電子發燒友App

評論