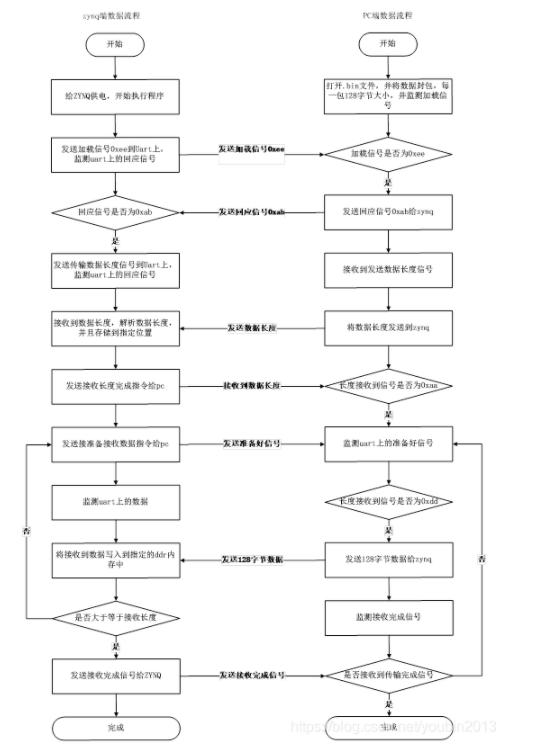

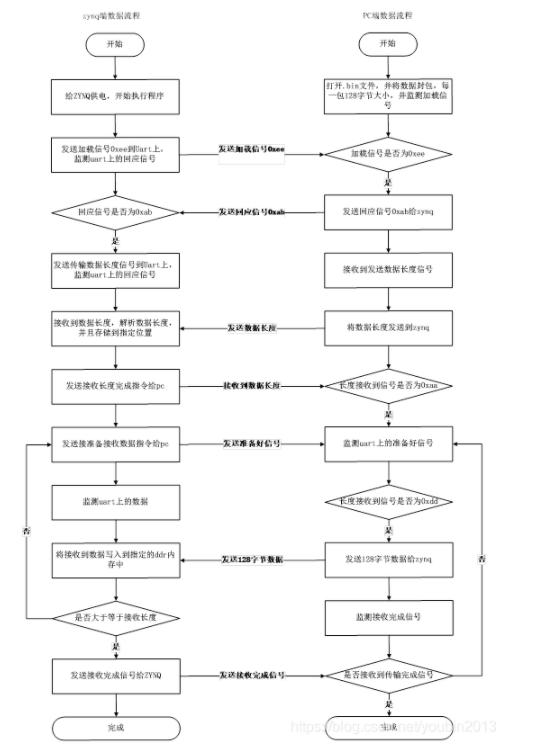

加載方法 ZYNQ的啟動鏡像是由FSBL程序(bootloader),PL配置文件(硬件比特流文件),應用層軟件三個部分組成,其通過SDK的軟件生成工具把三個部分按規定的格式拼湊成一個.bin文件

2020-12-05 10:15:37 4952

4952

比特流是一個常用詞匯,用于描述包含FPGA完整內部配置狀態的文件,包括布線、邏輯資源和IO設置。大多數現代FPGA都是基于SRAM的,包括Xilinx Spartan 和Virtex 系列

2022-11-30 10:59:17 733

733 FPGA器件有哪些配置下載方式?下載電纜ByteBlaster原理及配置方式

2021-04-15 06:26:33

嗨,大家好,只是一個簡單的問題。 FPGA編輯器是否有限制為包含嵌入式處理器(如PowerPC)的設計生成比特流?我問的原因是因為我在Project Navigator中創建了一個設計并運行了PAR

2018-10-18 14:44:29

Zynq FSBL src main.c在哪里是從QSPI加載比特流到Artix的PL的函數。我正在嘗試添加從QSPI加載位的功能到XIP的PL(參見下面的鏈接)。在下面的示例中,沒有PL。另一個

2020-03-19 10:33:09

嗨,我正在使用Zynq進行部分動態重新配置。我知道我可以在啟動時通過boot.bin加載靜態位流。同時,我還可以在boot.bin中包含我的部分比特流,以便在啟動時將其存儲在RAM中的某個地址中

2020-04-21 10:23:57

`請問比特流是什么?`

2019-08-23 16:24:40

ATK-領航者ZYNQ開發板-7010 Edition DEVB_120X160MM 6~24V

2023-03-28 13:05:54

ATK-領航者ZYNQ開發板-7020 Edition DEVB_120X160MM 6~24V

2023-03-28 13:05:54

STM32開發板 STM32F103RCT6最小系統板 ARM 一鍵串口下載 液晶屏

2023-04-04 11:05:04

1.為什么用USRP發送數字調制信號后,如FSK和QPSK,接收端解碼出來的比特流都是不對的?

2019-08-28 09:18:11

,我生成了比特流,我得到以下兩個錯誤:[DRC NSTD-1]未指定的I / O標準:4個邏輯端口中有1個使用I / O標準(IOSTANDARD)值'DEFAULT',而不是用戶指定的特定值。這可

2019-09-30 10:39:23

(xczu7eg-ffvf1517-1-e),代碼實現并正確生成比特流。然而,當我使用Xilinx平臺電纜II通過JTAG配置帶有比特流的設備時,我得到錯誤Labtools 27-3303。 (分配給設備的比特流不正確

2020-06-09 14:24:42

嗨,大家好,我正在開發一個Vivado項目,其中包含JESD IP內核。我使用的工具是Vivado 2015.4,我們擁有JESD的有效許可證。該項目的合成和實施是成功的。但是,生成比特流時發生錯誤

2018-12-18 10:45:31

大家好,最近剛接觸FPGA不久 現在手上有一塊xilinx SP3E開發板,簡單的設計了一個流水燈的程序 通過JTAG下載方式 直接下到FPGA里 板子可以運行 因為想實現斷電后重啟板子自動

2014-10-11 11:16:08

你好,我只是想知道Xilinx是否有用于比特流加密的文檔(或教程)。 UG191的第33-35頁有一些簡短的說明,但我不知道Xilinx是否喜歡逐步實施。謝謝。強

2020-06-15 13:39:44

(具體可以查閱xilinx的相關教程),然后再下載到開發板上的flash中。這整個過程都沒問題,但是本人一直很奇怪.mcs文件是怎么寫入flash中的,是通過JTAG連接器經過FPGA芯片在寫入

2017-09-20 21:29:07

大家好,我正在與SoC邁出第一步,我目前正在使用Zybo Zynq開發板。我有一個簡單的問題:是否可以創建多個設備配置,為每個配置生成比特流并將比特流存儲在內存或其他內容中,以便創建一個說“配置庫

2020-05-20 10:44:19

ch340下載方式與STLINK/JLINK下載方式有哪些不同呢?

2021-12-15 07:00:38

labview怎么導入視頻,然后再將其轉化為比特流?新手小白,求助各位大佬解答,最好能給個vi例子解釋一下,非常感謝

2023-10-18 23:58:07

。第二步:如果你是在原來的工程上面修改的,建議你在export hardware時把原來工程的.sdk文件夾里面的東西全都刪掉,然后再重新產生比特流。.sdk文件夾中的內容,.hdf是生成比特流后產生

2015-06-14 14:27:17

都還離不開ISE,除非,ISE不支持該芯片(比如A7最小的那幾塊)。 (3)用vivado集成環境內的硬件會話(hardware session)下載比特流時斷開板子再連接, hw_server就會連接不上, 卡頓在那,必須退出vivado, 在任務管理器結束hw_server才行。

2015-07-08 17:35:03

嗨,我正在嘗試部分自我重新配置。想法是通過介質將部分比特流發送到FPGA。FPGA接收它(在多個塊中)并將比特流寫入ICAP。當連接發生時,我的FPGA的行為會發生什么發送部分比特流中途消失了?我

2019-02-14 09:40:06

50MHz QSPI頻率.-使用比特流壓縮將我的比特流文件減少到大約1,6MB而不是3,6MB通過這種方法,我可以達到160毫秒左右的啟動時間。這適用于某些PC但不適用于所有PC。我知道Tandem

2020-06-09 16:42:15

大家好,有沒有一種簡單的方法可以使用IMPACT(ISE)將比特流下載到Zynq設備中而無需啟動ARM?我知道這可以用Vivado完成。TIA

2020-07-21 15:11:31

加載部分比特流時,它不起作用。我在ML605板上工作。我閱讀了有關PRC和EPRC的XAPP887,但我真的不明白如何更改設計以執行加密。有人可以幫幫我嗎?星期六以上來自于谷歌翻譯以下為原文Hi, I

2019-01-23 10:43:02

大家好,當我將在XPS中為我的系統生成的比特流下載到我的目標板時出現錯誤.jtag鏈是串行鏈,設備1是來自ACTEL的aglp125vs CPLD,設備2是目標fpga

2019-01-18 17:20:43

25MHz的自由運行clk模式下完成。我不知道如何調試這個。我可以以某種方式回讀fpga比特流,看看差異在哪里。我記得這對ise / impact來說是不可能的,因為比特流在回讀時會以某種方式被修改 - 是否有可能用vivado做到這一點?問候Klemen

2020-08-06 09:15:36

如標題所述,我想從相同的實現為同一FPGA(Artix-7)生成2種類型的比特流(SPI x4和SelectMAP x16)。這有點可能嗎?目前,我有兩種不同的實現運行(由于約束集 - 在xdc文件中的CONFIG_MODE是不同的),它們必須單獨運行以生成相應的比特流。

2020-06-09 07:40:00

我正在開發一個具有大型遠程可升級比特流和慢速閃存寫入速度的項目。這些比特流使用普通文件壓縮(pkzip,gzip等)傳送。我想將更新的比特流以壓縮格式存儲在閃存上,并使用多引導方法引導它們

2020-05-29 17:12:21

你好,請有人解釋我如何使用IMPACT在FPGA xilinx中下載比特流先謝謝你以上來自于谷歌翻譯以下為原文hello,please can someone explain me how

2019-01-15 10:08:59

:PROM應包含以USR_ACCESS寄存器為目標的數據包。我使用iMPACT生成了我的PROM文件,只需將兩個比特流放入單個MCS文件中,這可能是錯誤的。我認為我的MCS應該包含正常的主FPGA比特流,然后

2020-05-29 10:14:55

Mul7.穆添加8. Mul Sub9. Mul Mul現在我希望為上述任何一種組合提供完整的比特流(比如Add Add)。并且我希望部分比特流用于所選擇的組合,即添加用于部分區域1和1。 2,Sub

2020-05-05 09:42:44

的筆記本電腦我想將一些比特流文件發送到NEXYS 4 Board中的Artix-7 Xilinx FPGA,然后使用這個比特流數據存儲閃光燈。我已經為這塊板提供了Pmod Wifi模塊。可以與我的筆記本電腦

2020-04-30 07:46:17

如何檢查比特流中的多重引導回退設置? abitstream中的CONFIGFALLBACK ENABLE信息在哪里?我對多重引導的約束設置看起來很合理,我只想確認比特流中的設置是否符合約束條件。從我

2020-06-05 12:38:38

這就是為什么DDR3 SODIMM無法工作的原因。為了確認效果,我在比特流的“啟動選項”中選擇“等待DCI匹配”作為“自動”。根據選項,如果DCI無法匹配,DONE將不會變高。我使用上述設置下載比特流

2020-06-15 16:36:57

你好,這是一個思維設計,而不是我正在積極努力的東西,但是:我想分析一下比特流。比特流包含在時鐘脈沖或兩個時鐘脈沖之間對齊的脈沖。沒有明確的時鐘信號,但我知道粗略的時鐘速度,并且在比特流中嵌入同步序列

2018-12-17 16:35:26

所有:由于缺少DMS respin的源文件,我很高興不得不重用遺留部分。我所擁有的只是一個最初存儲在XC1701部件上的比特流。我們相信我們已經使用板外編程器成功地將此流編程到Micron

2020-05-29 11:06:25

XPS中設計了您的硬件平臺,最終為FPGA生成了一個比特流。”這是真實的,我就是這樣。現在它說,“......你將硬件平臺描述導出到軟件開發套件(SDK)。”手冊說要遵循以下步驟:1.在PlanAhead

2020-03-23 09:19:10

用iMPACT工具向Spartan 6下載“SPI Flash編程”比特流,該工具將從PC接收數據,以便使用步驟2中生成的文件對SPI進行編程。4.我們將使用PROG_B使用SPI中的新數據重啟Spartan

2019-07-04 08:13:32

你好我有一個在MIcroBlaze上運行linux的設計要求。我能夠在我的Virtex-7 FPGA上下載比特流(在Vivado 2014.4中生成)。我使用Impact來編程我的FPGA。我因此

2020-04-02 10:05:40

嗨,我有一個應用程序,我希望在下載到FPGA之前使用類似于data2mem的工具來在FPGA比特流中破解塊內存內容。FPGA可以是Virtex 6或Artix 7或Kintex 7。比特流未加密且未

2019-03-19 12:44:14

我在使用EDK 10.1中的微填充處理器在FPGA中下載比特流文件時遇到問題。我只是將Microblaze processsor比特串文件下載到FPGA中(斯巴達3a dsp)...連接的要求是什么?我有JTAG和一個串口....什么是stepi必須遵循。

2020-03-30 10:07:31

嗨,我有幾塊帶有Spartan 3器件的電路板,并希望將相同的比特流加載到所有電路板中。我應該選擇哪個端口在電路板和設備上使用?是否可以在JTAG配置模式下進行配置?謝謝。阿卜杜拉以上來自于谷歌翻譯

2019-01-10 11:15:42

嗨,我想嘗試色度重采樣器IP。所以我獲得了硬件評估許可證,以便在我的主板上進行測試。但是,在比特流生成過程中,我得到了:[Common 17-69]命令失敗:此設計包含一個或多個不允許生成比特流

2019-01-08 10:07:07

嗨我有一個問題,我無法在我的spi flash中加載比特流,我在鏈中有兩個不同的FPGA。 Impact看到了單個FPGA及其Flash,但是我無法在比特流中加載它們。我試圖簡化鏈路繞過兩個附加

2020-03-23 08:47:52

'hdcp@2015.09'未經許可.IPCP功能在IP GUI上也不可用(灰顯)。忽略此嚴重警告后,我們能夠生成,合成,放置和路由知識產權。但無法生成比特流。錯誤是:[Common 17-69]命令失敗:此

2019-01-03 11:06:05

你好,我使用Vivado 2017.4;當我運行Synthesis和Implementation時,一切似乎都可以。但是,當我想生成比特流文件時,沒有任何錯誤消息發生。.runs / impl_l

2018-11-09 11:37:53

嗨專家, 我正在使用spartan-6 FPGA進行多重啟動實驗。我發現位文件位于ug380上,如下圖所示。黃金比特流位于閃存的下部塊上,多重引導比特流位于閃存的較高塊上。 因此,如果我想使用保護區

2020-06-09 17:43:26

來自EMI12.4和13.3的比特流文件中的重要區別是什么?我從開始文件tosequence 0xF,交換和loadind到FPGA切換字節。來自12.4boot的比特流確定,但不是來自13.3。誰能幫我?

2020-06-12 14:04:57

求助,生成DDR200T開發板FPGA bit/mcs文件時需要下載Release package怎么下載?

2023-08-12 08:30:07

嗨,我正在嘗試使用JTAG將比特流下載到ML507。平臺電纜變為綠色并檢測到JTAG鏈。問題是,我無法下載比特流。IMPACT報告:錯誤顯示在狀態寄存器中,釋放完成位不是1。SW3配置為:00010100希望有人可以提供幫助,安德烈log.txt 6 KB

2019-08-26 10:03:51

大家好,當我嘗試在本教程中生成比特流時:http://blog.idv-tech.com/2014/05/18

2018-10-24 15:31:25

STM32程序的DAP下載方式和串口下載方式分析前提簡述DAP下載方式功能快捷鍵合理的創建標題,有助于目錄的生成如何改變文本的樣式插入鏈接與圖片如何插入一段漂亮的代碼片生成一個適合你的列表創建一個

2021-07-16 06:20:09

你好我用vertex6購買評估板我下載ISE 12.1,安裝完整版,進行30天評估,獲得許可。但是,當我在XPS中生成比特流時,我得到:信息:安全性:65- 您的“ISE”許可僅供試用:安全:69-

2018-11-27 14:36:14

有沒有辦法改變比特流文件位于Vivado(2016.1)內的位置?我知道我可以在Tcl控制臺上輸入tcl命令“write_bitstream”(https://forums.xilinx.com

2020-05-12 09:23:20

的模塊。之后,我可以執行實現和位生成,該工具將創建完整和部分比特流。通過這種方式,我將得到4個比特流,兩個部分(每個可重新配置模塊一個比特流 - 讓我們稱之為BIT_A)和兩個完整(一個比特流,左移

2020-06-04 08:52:24

MYD-C7Z015是米爾科技推出的基于Xilinx Zynq-7015(XC7Z015)芯片的一款FPGA+ARM的嵌入式開發板,該產品采用核心板加底板架構模式,提供了穩定的CPU最小系統模塊,方便二次開發產品外圍接口、功能,使不同行業應用的產品快速上市。

2021-07-27 11:08:19

FPGA/CPLD下載方式 (ISP下載線接口電路)

SP功能提高設計和應用的靈活性未編程前先焊接安裝系統內編

2009-03-08 10:47:02 129

129 本資料是FPGA開發板DIY 腳本文件。

2012-09-29 11:29:36 73

73 串口isp下載方式串口isp下載方式串口isp下載方式串口isp下載方式串口isp下載方式

2015-12-18 11:48:43 0

0 學習FPGA的程序下載方式,包含altera和xilinx程序下載方式,下載程序所用格式分類以及格式轉換工具介紹。

2018-10-31 08:00:00 17

17 在使用 FPGA 構建的基于微控制器的典型系統中,開發人員需要管理用于加載 FPGA 編程比特流的序列和安全性。在 Zynq SoC 中,集成的處理器負責執行常規微控制器的任務,包括管理 PL 結構

2019-04-30 16:42:51 4721

4721

本文檔的主要內容詳細介紹的是火龍果ZYNQ FPGA開發板的電路原理圖免費下載。

2020-03-09 08:00:00 37

37 有些人對于FPGA下JTAG的下載方式有些迷惑,為什么出現配置芯片了,為什么要用不同的下載電纜,不同的下載模式?通過在網上查閱相關資料做了總結和整理如下:

2021-01-05 16:21:16 17

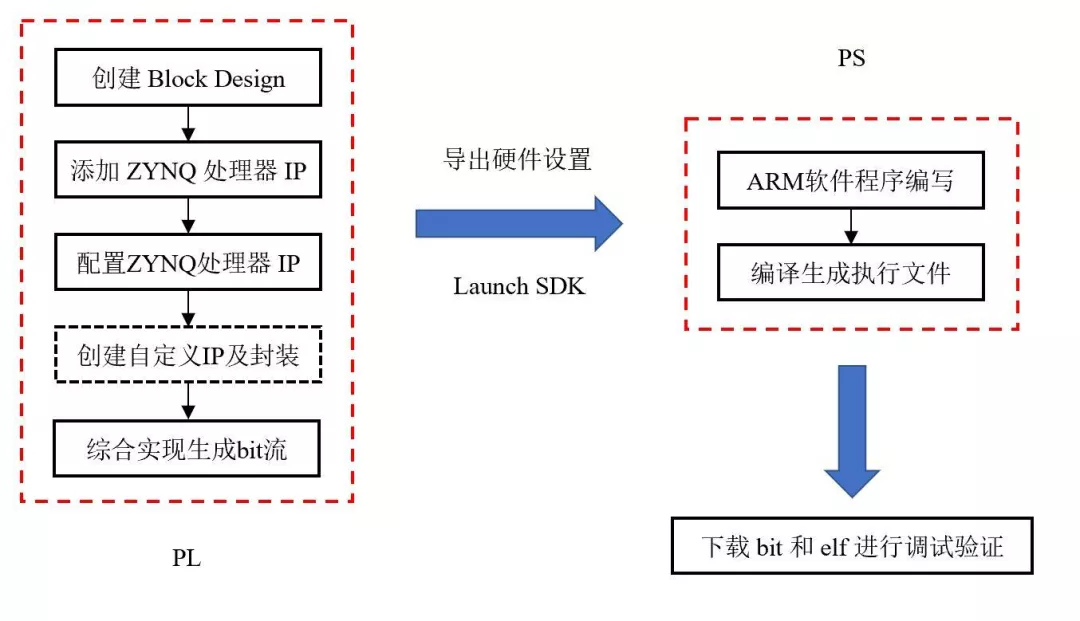

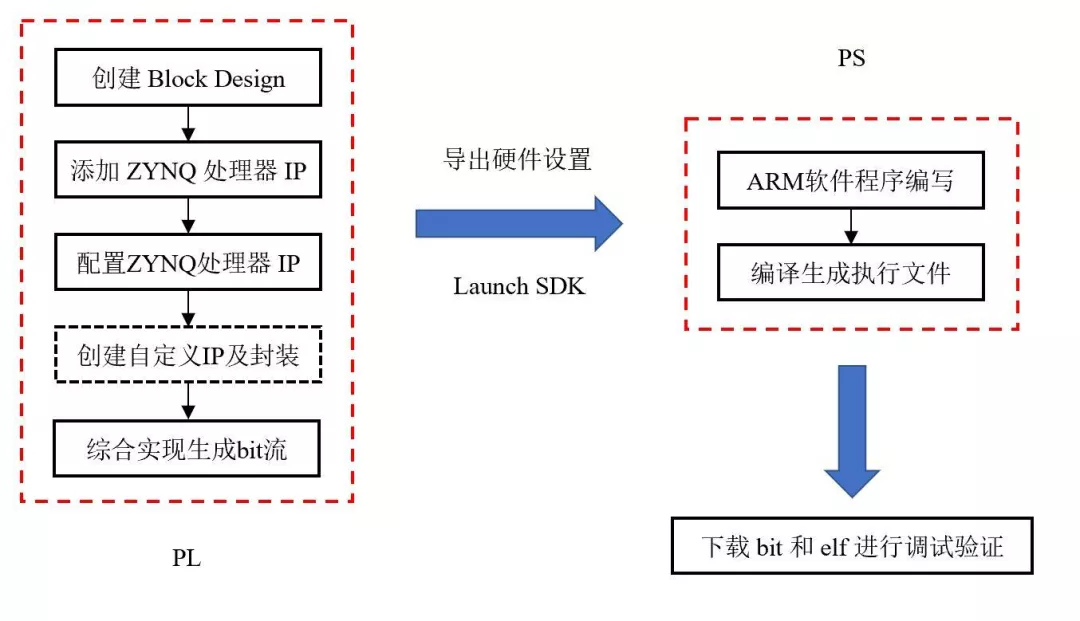

17 硬件比特流文件(.bit)和軟件的可執行鏈接文件(.elf)下載到 Zynq 開發板中,這樣就可以對自己的軟硬件設計進行調試和驗證。

2022-02-08 11:48:37 1021

1021

硬件比特流文件(.bit)和軟件的可執行鏈接文件(.elf)下載到 Zynq 開發板中,這樣就可以對自己的軟硬件設計進行調試和驗證。

2021-01-26 07:30:29 20

20 本文檔的主要內容詳細介紹的是Altera Cyclone III系列FPGA開發板的庫文件免費下載。

2021-03-07 08:00:00 17

17 STM32環境配置和下載方式

2021-12-07 11:06:10 6

6 電子發燒友網站提供《使用加密保護7系列FPGA比特流.pdf》資料免費下載

2023-09-13 15:31:19 0

0 接下來我們下載兩塊開發板的測試程序,先在5CEFA7F23的下載器內添加比特流文件,輸入翻轉率50%比特流文件并且加載。

2023-12-15 11:41:00 239

239

電子發燒友App

電子發燒友App

評論