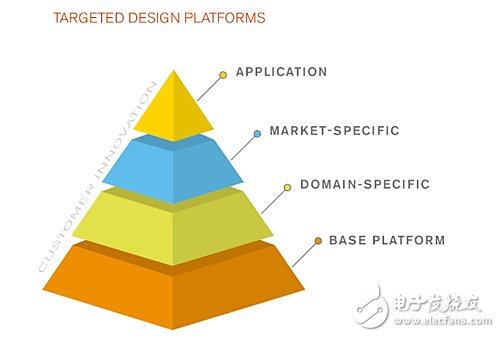

2009年2月Virtex?-6和Spartan?-6系列的隆重發(fā)布,標志著賽靈思公司致力于提高FPGA設計效率和增強FPGA易用性的嶄新平臺方法的開端。與半導體領域內的領先公司所采用的許多平臺設計方法相同,賽靈思的目標設計平臺 (Targeted Design Platform) 也采用了開放的標準、通用的開發(fā)流程以及類似的設計環(huán)境,盡量減少任何開發(fā)項目中都能遇到的通用工作對設計人員時間的占用,確保他們能集中精力從事創(chuàng)新性的開發(fā)工作。

之所以選擇了“目標”這個詞,是因為每一代新的FPGA都為日益增加的應用提供了更好的解決方案,解決這些應用在嵌入式、數(shù)字信號處理或系統(tǒng)方面所面臨的需要高帶寬通信通道以便處理大量數(shù)據(jù)的瓶頸問題。其成功之道在于能夠充分發(fā)揮FPGA內在的并行性、集成存儲、DSP和通訊特性的優(yōu)勢。進行系統(tǒng)設計的工程師背景各不相同,分別來自不同的設計領域,他們需要有助于發(fā)揮出各自領域專長的的工具和知識產權 (IP)。據(jù)此,賽靈思認識到必須推出能夠全面支持并可輕松擴展到不同終端應用的參考設計,確保參考設計能真正成為終端應用開發(fā)的基礎或起點。

每個開發(fā)套件都包括了面向Virtex-6或Spartan-6器件的開發(fā)板;面向DSP、嵌入式或連接、具有優(yōu)化設計流程的ISE? 設計套件完整版;經過全面驗證的目標參考設計;支持專門特性評估和板上診斷的設計示例和演示;完整的文檔資料和說明(包括設置、評估和修改參考設計所需的源代碼,可作為終端應用設計的起點);以及所有必需的電源、配置和通信線纜。

我們還提供一系列逐步深入的學習指南,幫助FPGA新手快速啟動設計工作。這些學習指南介紹了基本的設計方法,如FPGA編程、工具流程編譯步驟、設計方案的創(chuàng)建以及驗證等內容。

連接平臺

賽靈思的串行和并行連接解決方案能滿足實現(xiàn)背板、芯片間或不同產品間系統(tǒng)整合所需要的帶寬、電源和成本最高標準要求。利用最新一代Virtex-6和Spartan-6器件,可成功實現(xiàn)最低功耗、最高速串行收發(fā)器的設計,并得到業(yè)界最廣泛的協(xié)議支持。此外,內置的PCI Express?和三模以太網MAC塊還能節(jié)約寶貴的邏輯資源和功耗,同時以更低的成本實現(xiàn)高性能連接。

支持賽靈思 Spartan-6 FPGA和高性能Virtex-6 FPGA系列的兩款新型連接套件為賽靈思連接解決方案提供了簡單易用的完整開發(fā)和演示平臺。

處理平臺

對習慣于使用RISC或DSP處理器的開發(fā)人員來說,轉向采用FPGA硬件可能相當困難,他們需要學習一系列新的設計技巧,并對硬件進行一定的了解。對于剛接觸FPGA或FPGA處理的開發(fā)人員來說,這真是個非常重要的決定,因為有可能會增加潛在的風險,并有可能延長設計周期。

賽靈思面向嵌入式和DSP應用的Spartan-6和Virtex-6 FPGA開發(fā)套件專門設計專門用于簡化FPGA的推廣,使軟硬件和算法開發(fā)人員能快速啟動賽靈思 FPGA片上系統(tǒng) (SoC) 應用的開發(fā)工作。

?

圖2:賽靈思 Virtex-6 FPGA ML605和Spartan-6 FPGA SP605開發(fā)板

下面我們將詳細介紹2009年12月8日宣布推出的四款開發(fā)套件:

賽靈思 Spartan-6 FPGA連接開發(fā)套件

賽靈思 Spartan-6 FPGA連接套件采用低成本Spartan-6 LXT器件系列,是一款完整的、簡單易用的連接開發(fā)和演示平臺。作為賽靈思連接目標設計平臺,該套件提供了創(chuàng)建高速串行系統(tǒng)和其它開箱即用型連接應用所需的軟硬件、IP和目標參考設計。

Spartan-6 LXT FPGA能利用業(yè)界標準的PCI Express?(1.1版)、以太網(GMII、SFP)和DDR3等高速串行協(xié)議開展設計,而且支持基于其他串行標準和高達3.125Gb/s的專利實施方案以及包括3.3V I/O標準在內的多種并行協(xié)議的設計工作。

采用Spartan-6 LXT FPGA的連接套件簡化了多協(xié)議系統(tǒng)的設計、開發(fā)和驗證,使設計人員能通過高效、低成本的可編程連接解決方案來實現(xiàn)產品差異化。該套件集成了連接開發(fā)所需的關鍵組件,可加速設計、實施低成本協(xié)議橋接,而且對LVDS通信而言提供了效率更高的替代方案,能滿足多種不同細分市場的要求。通過提供可擴展的構建塊架構以及目標參考設計和業(yè)界標準的FMC子卡擴展硬件環(huán)境,它還能作為針對市場專用的連接設計平臺的起點。

特性和優(yōu)勢

提供創(chuàng)建功能全面的工作系統(tǒng)所需要的所有軟硬件、固件、IP和參考設計的綜合連接開發(fā)平臺

?ISE 設計套件:嵌入式版本專門用于邏輯和連接設計人員所需(器件鎖定為Spartan-6 LX45T FPGA)。

?預驗證、可定制的目標參考設計集成了PCIe、千兆以太網和板上DDR3存儲器以及虛擬FIFO和優(yōu)化Packet DMA,可加速帶寬。

?專為Spartan-6 FPGA和連接套件進行優(yōu)化了的完整版Northwest Logic PCIe Packet DMA引擎。

技術規(guī)范

?采用Spartan-6 LX45T FPGA且符合RoHS標準的SP605板,通用電源及配套線纜。

?支持插件可擴展性的板上FMC子卡接頭。

?具有設備驅動程序文件、設計源文件和應用的USB記憶棒。

?包括示意圖、Gerber文件、板BOM和詳細的用戶指南在內的可下載文檔資料。

賽靈思 Virtex-6 FPGA連接開發(fā)套件

賽靈思 Virtex-6 FPGA連接開發(fā)套件是一款采用高性能Virtex-6 LXT FPGA系列產品的全面的連接開發(fā)和演示平臺。作為賽靈思連接目標設計平臺,該套件提供了創(chuàng)建高速串行系統(tǒng)和其它開箱即用型連接應用所需的軟硬件、IP和目標參考設計。

Virtex-6 LXT FPGA幫助設計師進行設計時利用PCI Express 1.1/2.0、以太網(GMII、SFP、XAUI)、SATA和其它線速高達6.5Gb/s的專利高速串行協(xié)議,以及通過SelectIO?技術支持速度高達1.4Gb/s的多種并行標準。

這款采用Virtex-6 LXT FPGA的連接套件簡化了高性能、高帶寬、多協(xié)議系統(tǒng)的設計、開發(fā)和驗證工作,能滿足不斷變化的市場需求。Virtex-6 FPGA連接開發(fā)套件提供了經過生產檢驗的設計方法和工具套件使設計人員能實時分析并調試高速串行解決方案。

該套件能夠通過在正常工作的系統(tǒng)中集成了PCI Express和XAUI協(xié)議IP核心的目標參考設計快速啟動開發(fā)工作。該系統(tǒng)能通過虛擬FIFO訪問板上DDR3存儲器,并能通過高性能優(yōu)化包DMA加速帶寬。通過提供基于目標參考設計的可擴展構建塊架構以及業(yè)界標準FMC子卡擴展環(huán)境,Virtex-6 FPGA連接開發(fā)套件還可作為針對市場專用的目標設計平臺的起點。

特性和優(yōu)勢

?提供所有軟硬件、固件、應用IP和GUI的綜合開發(fā)平臺,可創(chuàng)建功能全面的系統(tǒng)解決方案。

?ISE 設計套件:專為邏輯和連接設計人員而定制的嵌入版提供ChipScope? Pro 分析器和Serial I/O 套件(器件鎖定為Virtex-6 LX240T FPGA)。

?面向PCIe-10GDMA-DDR3-XAUI的預驗證、可定制且全面支持的目標參考設計。

?提供多個設計示例,如SFI4.1、SFI5和PCIe 2.0以及1.1多信道配置等。

技術規(guī)范

帶有Virtex-6 LX240T器件且符合RoHS標準的ML605基礎版。

?通用電源和配套線纜,包括CX4 回路模塊。

?符合VITA57標準的FMC子卡支持CX4、SATA和SMA接口。

?存儲了設備驅動程序文件、設計源文件和應用的USB記憶棒。

?包括原理圖、Gerber文件、板BOM和詳細的用戶指南在內的可下載的文檔。

嵌入式目標設計平臺(賽靈思 Spartan-6和Virtex-6 FPGA嵌入式開發(fā)套件)

賽靈思嵌入式開發(fā)套件通過Virtex-6 FPGA和Spartan-6 FPGA簡化了嵌入式處理器系統(tǒng)的開發(fā)工作。作為賽靈思的嵌入式目標設計平臺,上述套件提供了創(chuàng)建開箱即用型嵌入式系統(tǒng)所需的所有軟硬件、IP和參考設計。

Spartan-6 FPGA嵌入式開發(fā)套件為需要連接功能的嵌入式應用提供了低成本基礎平臺。Virtex-6 FPGA嵌入式開發(fā)套件則為需要高性能處理、串行連接和高級存儲接口功能的嵌入式應用開發(fā)提供了功能全面的環(huán)境。上述兩款套件都配套提供可作為硬件定制和軟件開發(fā)起點的MicroBlaze?處理器子系統(tǒng)目標參考設計,而且還提供了視頻處理設計示例和學習指南,該指南詳細演示了如何進一步定制系統(tǒng)。

對獨立(或裸機)軟件開發(fā)來說,可使用基于Eclipse的軟件開發(fā)套件 (SDK) ,該套件包括GNU工具、創(chuàng)建軟件應用和鏈接器腳本所需向導、閃存寫入程序、以及滿足嵌入式外設需要的標準C語言庫和驅動程序等。Linux或RTOS軟件開發(fā)由一系列能與賽靈思 SDK無縫協(xié)同工作的第三方操作系統(tǒng)和中間件解決方案提供支持。

特性和優(yōu)勢

?提供所有軟硬件、固件構建塊和工具的綜合開發(fā)平臺,滿足快速啟動應用開發(fā)需要。

?符合RoHS標準的板可實現(xiàn)了嵌入式處理器子系統(tǒng)與DDR3、PCI Express、千兆以太網、支持插件可擴展性的UART接口和業(yè)界標準的FMC等完全集成。

?目標參考設計具有MicroBlaze處理器、多端口DDR3存儲控制器、三模以太網MAC、UART、SPI、I2C、計時器、中斷控制器和片上存儲器。

?軟硬件學習指南演示了如何定制設計,并提供了編譯、調試和剖析軟件應用的最佳實踐。

?支持Linux和RTOS。具體包括支持PetaLogix的PetaLinux OS以及通過uC/Probe調試工具支持Micrium的uC/OS-II和uC/TCP-IP端口。中間件則支持Treck的高性能TCP/IP堆棧。

技術規(guī)范

?Virtex-6 FPGA嵌入式開發(fā)套件:帶有Virtex-6 LX240T FG1156器件的ML605基礎板、通用電源和配套線纜。

?Spartan-6 FPGA嵌入式開發(fā)套件:帶有Spartan-6 LX45T FG484器件的SP605基礎板、通用電源和配套線纜。

?ISE 設計套件嵌入版。提供Platform Studio工具、EDK和SDK(器件鎖定為Virtex-6 LX240T或partan-6 LX45T FPGA)。

?存儲了參考設計、演示、文檔和學習指南的USB記憶棒。上述內容也可從網上獲得。

DSP目標設計平臺

FPGA是在DSP處理帶寬要求超過10 GMAC情況下一種常見的硬件選擇。FPGA的靈活性使其非常適用于高性能或多通道DSP應用,從而充分發(fā)揮硬件并行性的優(yōu)勢,讓更低成本和功耗的單芯片解決方案相對于多DSP實施方案而言實現(xiàn)更大的優(yōu)勢。

賽靈思 FPGA DSP套件將于明年1月接受預訂。該套件有助于設計人員在一天之內就在賽靈思 FPGA基礎上完成應用的原型設計工作。每個開發(fā)套件都配套提供逐步遞進的軟硬件設置指南,確保從一開始就不浪費時間。圖形用戶界面可引導新用戶通過以下三個步驟啟動設計工作。

賽靈思 Spartan-6 FPGA DSP開發(fā)套件

賽靈思 Spartan-6 FPGA DSP開發(fā)套件為在低成本、低功耗的Spartan-6 FPGA基礎上實施DSP算法提供了完整的開發(fā)平臺。作為一款賽靈思 DSP目標設計平臺,該套件提供了所需的全部即用型開發(fā)板、IP、設計軟件和參考設計。

采用Spartan-6 LX150T器件的Avnet AS-LX150T開發(fā)板是Spartan-6 FPGA DSP開發(fā)套件的核心組成部分。該器件系列針對DSP應用在連接、存儲器和DSP硬件資源的平衡方面進行了適當優(yōu)化。LX150T是最大的一款Spartan-6器件,即便是要求最高的大規(guī)模DSP應用,它也能提供足夠的硬件資源。

特性和優(yōu)勢

?Spartan-6 LX150T FPGA具有180個增強型DSP48A1 芯片,DSP性能可達50 GMAC。

?無需RTL設計經驗就能在Mathworks Simulink?和MATLAB? DSP建模環(huán)境中使用面向 DSP的軟件System Generator開發(fā)DSP應用。

?經過預驗證的DSP目標參考設計提供了設計基礎設施以及DSP開發(fā)起點。

?可通過兩個業(yè)界標準的FMC連接器以及FMC I/O子卡供應商生態(tài)系統(tǒng)擴展適用于垂直市場應用。

?通過可指導新用戶開始基本套件操作的圖形用戶界面快速啟動設計工作。

技術規(guī)范

?采用Spartan-6 LX150T FPGA 的 Avnet AS-LX150T開發(fā)板。

?ISE 設計套件:系統(tǒng)版器件鎖定為Spartan-6 LX150T FPGA。

?基于Simulink的數(shù)字上變頻器 (DUC)/數(shù)字下變頻器 (DDC) 和基于RTL的DUC/DDC目標參考設計。

?線纜、電源和小型閃存。

?包括硬件設置和開始指南在內的可下載文檔。

賽靈思 Virtex-6 FPGA DSP開發(fā)套件

賽靈思Virtex-6 DSP開發(fā)套件為在高性能Virtex-6 FPGA基礎上實施DSP算法提供了完整的開發(fā)平臺。作為一款賽靈思 DSP目標設計平臺,該套件提供了所需的全部即用型開發(fā)板、IP、設計軟件和參考設計。

Virtex-6 FPGA DSP開發(fā)套件采用了賽靈思 ML605開發(fā)板和Virtex-6 LX240T器件。該平臺包括700多個DSP48芯片,DSP處理帶寬可超過400 GMAC,不愧為高性能無線、航空航天和國防應用領域中的完美開發(fā)平臺。

?

特性和優(yōu)勢

?Virtex-6 LX240T FPGA采用了788個增強型DSP48E1 芯片,DSP性能可達472 GMAC。

?無需RTL設計經驗就能在Mathworks Simulink?和MATLAB? DSP建模環(huán)境中使用面向 DSP的軟件System Generator開發(fā)DSP應用。

?經過預驗證的DSP目標參考設計提供了設計基礎設施以及DSP開發(fā)起點。

?可通過兩個業(yè)界標準的FMC連接器以及FMC I/O子卡供應商生態(tài)系統(tǒng)擴展適用于垂直市場應用。

?通過可指導新用戶開始基本套件操作的圖形用戶界面快速啟動設計工作。

技術規(guī)范

?采用了Virtex-6 LX240T FPGA的賽靈思 ML605開發(fā)板。

?ISE 設計套件:系統(tǒng)版器件鎖定為Virtex-6 LX240T FPGA。

?基于Simulink的DUC/DDC 和基于RTL的DUC/DDC目標參考設計。

?線纜、電源和小型閃存。

?包括硬件設置和開始設計指南在內的可下載文檔。

?

電子發(fā)燒友App

電子發(fā)燒友App

評論