根據BPSK調制信號調制機理和平方倍頻法原理,在FPGA平臺上設計實現了BPSK調制信號載波頻率估計單元。

2014-09-01 11:26:40 2585

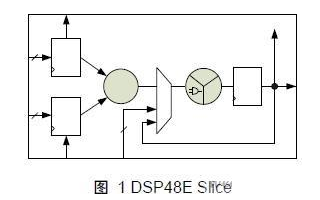

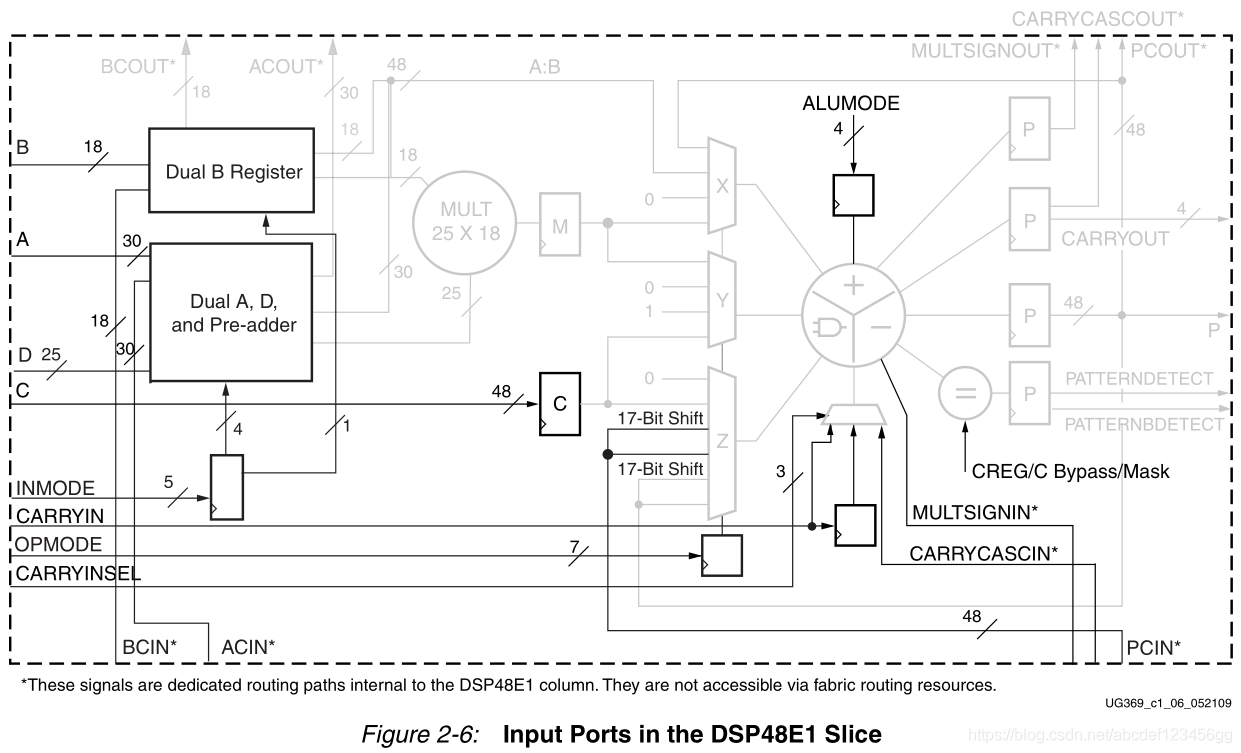

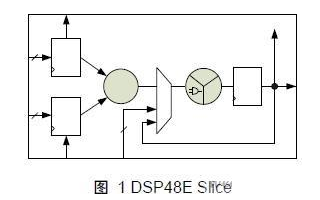

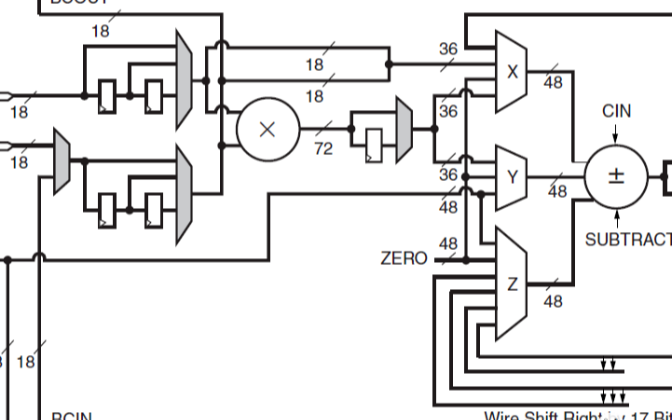

2585 本文系統的實現主要用到了兩類邏輯資源來優化系統性能:DSP48E Slice:25x18位二進制補碼乘法器能產生48位全精度結果。此功能單元還能夠實現諸多DSP模塊如乘累加器、桶形移位器、寬總線多路復用器等。

2020-09-03 12:45:22 555

555

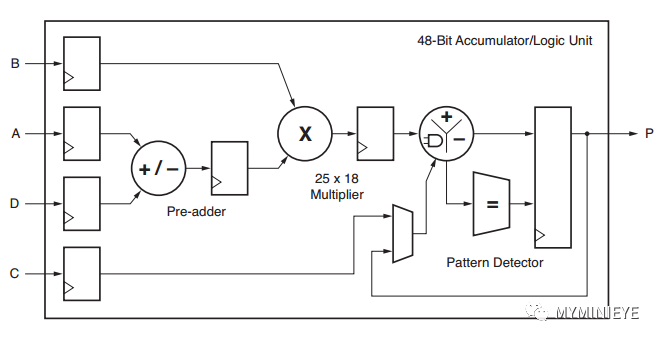

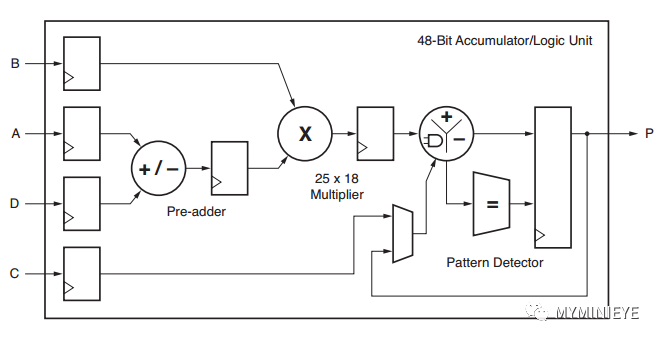

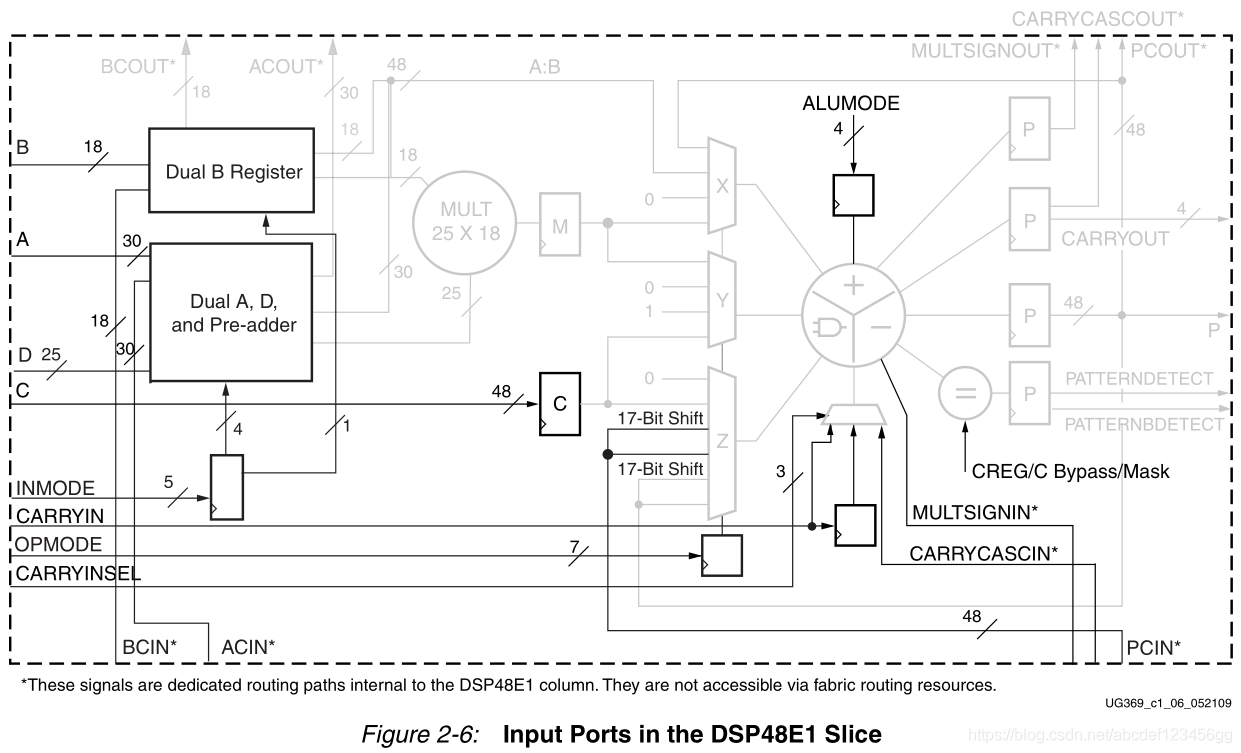

充分利用DSP資源,我們需要對DSP48E1有所了解。 1.DSP48E1介紹 DSP48E1是7系列的最小計算單元,DSP資源,支持許多獨立的功能,其基本功能如下所示 DSP48E1簡易模型 包括: 帶有D寄存器的25位預加法器 25*18二進制乘法 48位累加 三輸入加法 其他的一些功能還包括

2020-09-30 11:48:55 26617

26617

和C寄存器,具有獨立的復位和時鐘啟用。 ?CARRYCASCIN和CARRYCASCOUT內部級聯信號支持兩個DSP48E1片中的96位累加器/加法器/減法器 ?MULTSIGNIN

2021-01-08 16:46:10

7系列FPGA DSP48E1片的特點什么

2021-03-05 06:26:41

我正在實例化DSP切片并進行簡單的乘法然后加法((A * B)+ C)。根據DSP48E1用戶指南,當使用所有三個流水線寄存器時,它給出了最高頻率為600 MHz。但就我而言,它使用流水線寄存器

2020-06-12 06:32:01

嗨,我有一個如下的指令:(D-A)* B + C.端口A,B,C,D與DSP48E1輸入引腳相對應。我試圖將整個操作打包在DSP單元中。 (順便說一句,我的數據寬度是8位)在布局和布線完成后,我

2019-04-01 14:25:40

在我的設計中,我需要延遲一些數據(32位寬)一段時間。我一直在使用SRL16而不是FFs,它可以很好地延遲超過幾個周期。我還注意到,使用DSP48E1片很容易將數據延遲到48位寬,延遲三個周期,因此

2019-04-18 06:40:33

DSP48E1屬性

2021-01-27 06:21:23

。 DSP48E1片輸入數據端口支持許多通用的DSP和數學算法。DSP48E1片有四個直接輸入數據端口,分別為A、B、C和D。 A數據端口寬30位,B數據端口寬18位,C數據端口寬48位,預加器D數據端口寬25位

2020-12-23 16:54:08

)是指在系統加電時,DSP將一段存儲在外部的非易失性存儲器的代碼移植到內部的高速存儲器單元中去執行。這樣既利用了外部的存儲單元擴展DSP本身有限的ROM資源,又充分發揮了DSP內部資源的效能。盡管用戶代碼在

2011-07-08 11:10:56

DSP56800 16位DSP內核架構DSP56800內核是一款旨在同時提供高效實時DSP能力和通用計算能力的可編程CMOS 16位DSP內核。DSP56800內核由四個并行執行的功能單元組成,從而

2011-07-16 14:21:33

DSP56800 系列簡介DSP56800系列芯片基于DSP56800 16位定點DSP微控制器中央處理單元(CPU)內核。DSP56800內核的設計宗旨是同時提供高效的DSP和控制器運算能力。其

2011-07-16 14:20:41

`產品特點基于ZYNQ+并行DSP處理架構處理架構十分靈活,能夠滿足各類并行加速需求支持OpenCL編程,方便算法移植系統處理靈活:FPGA或DSP可選尺寸小巧,方便集成擴展能力強 應用領域并行控制

2017-06-08 10:33:07

DSP并行處理的方法摘 要:TI公司的TMS320C6x和AD公司的ADSP2106x是目前業界使用廣泛的數字信號處理器(DSP)。

2009-11-03 15:16:47

操作,用硬件的方法總比用軟件的方法有著無法比擬的速度優勢。 DSP處理都有自己的累加器單元AUL,大多數的DSP處理器在執行乘加操作時可以在一條指令周期內同時...

2021-11-03 08:41:44

想請教一下高手,公司了DSP開發或大家自己開發學習用TI定義的庫還是自己定義相關寄存器,然后在自己定義的基礎上進行相關算法的開發????

2014-05-22 12:58:35

充當,利用DSP的HPI接口組成一個多DSP互 連并行系統,一般是一個主處理器和一個從處理器,此種方法的一個應用實例是在雷達中的應用。滑窗算法是數字信號處理中一種常用的基本算法,但滑窗算法一般

2019-04-08 09:36:19

近來,Altera公司推出業界首款浮點FPGA,它集成了硬核IEEE754兼容浮點運算功能,提高了DSP性能、設計人員的效能和邏輯效率。據悉,硬核浮點DSP模塊集成在

2019-07-03 07:56:05

1.請問AM335X armv7 架構是否有向DSP 有單週期可執行多個乘加運算的功能 ??

2. FFT 運算式會運用到AM335X的VFP 還是NEON??

3.若執行一段浮點運算程式碼 例如

2018-06-21 06:58:42

算術邏輯單元(ALU)和一個帶有48位累加器的單24x24位乘加器(MAC)。這些單元都以并行狀態工作,并具有雙口數據存儲接口,可以同時產生地址信息。所有尋址模式包括反轉和求模運算都支持高效率的單周期訪問。

2011-03-12 03:00:07

分時鐘、DSP48E/A模塊、BRAM模塊、DCM模塊。0.5學時4. ISE高級操作技巧,包括:FloorPlanner、FPGA Editor、ChipScope Pro

2009-07-21 09:22:42

小、帶寬要求低等優點,特別適用于各種無線設備和智能卡等計算資源受限的設備,因而受到了人們的廣泛關注,成為新一代公鑰密碼標準。而模乘運算是橢圓曲線加密算法中的核心運算,如何高效地實現模乘運算是當前的一個研究熱點。

2020-03-20 06:04:40

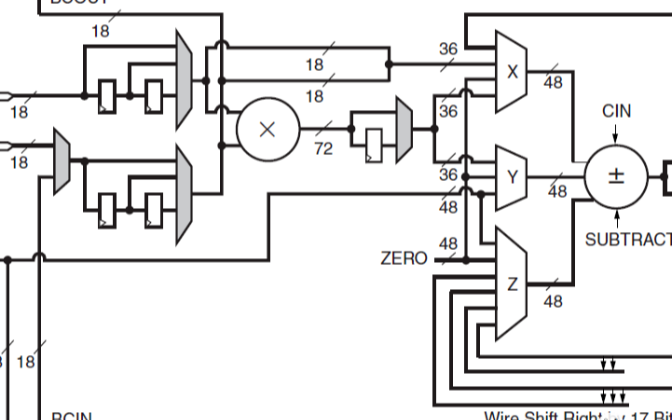

,Z選擇器的輸入;(7bit)

?ALUMODE邏輯控制選擇單元;(4bit)

我們通過構建一個乘累加器來介紹DSP的使用以及寄存器的配置。

實現的乘累加完成如下功能,即SUM = SUM

2023-06-20 14:29:51

數字信號處理(DSP)芯片曾經作為協處理器來實現濾波器算法。現在DSP技術的發展已實現了多個復雜算法的并行。但是,這種功能的擴展也產生了新的問題,開發人員發現,在DSP處理能力方面,當MIP和存儲器的問題得

2010-04-03 08:21:50

分時鐘、DSP48E/A模塊、BRAM模塊、DCM模塊。0.5學時4. ISE高級操作技巧,包括:FloorPlanner、FPGA Editor、ChipScope Pro

2009-07-21 09:20:11

分時鐘、DSP48E/A模塊、BRAM模塊、DCM模塊。0.5學時4. ISE高級操作技巧,包括:FloorPlanner、FPGA Editor、ChipScope Pro

2009-07-24 13:07:08

本帖最后由 eehome 于 2013-1-5 10:03 編輯

fpga實現濾波器在利用FPGA實現數字信號處理方面,分布式算法發揮著關鍵作用,與傳統的乘加結構相比,具有并行處理的高效性特點

2012-08-11 18:27:41

fpga實現濾波器fpga實現濾波器在利用FPGA實現數字信號處理方面,分布式算法發揮著關鍵作用,與傳統的乘加結構相比,具有并行處理的高效性特點。本文研究了一種16階FIR濾波器的FPGA設計方法

2012-08-12 11:50:16

為什么BUFG驅動DSP48E1的CE會出現問題?警告:LIT:683 - DSP48E1符號“Inst_control_loop / u_Subsystem11

2020-06-12 11:45:43

QuartusII中乘加器IP的手冊,如上圖所示,出現DSP Blocks字樣。手冊中說到,DSP塊由一些專用的邏輯塊組成。這些邏輯塊可以實現乘法、加法、減法、累加、求和運算。你可以把DSP塊配置成

2020-09-04 10:31:13

與遵循馮·諾依曼結構的CPU和單片機不同,典型的DSP內部采用改進的哈佛結構和流水線技術,可以在單指令周期內完成乘加指令,更具有擴展動態范圍的乘積累加單元、數據指針環形尋址和零開銷循環跳轉等特殊

2011-03-06 22:28:27

)、離散余弦變換(DCT)、小波變換、數字濾波器(有限脈沖響應(FIR)、無限脈沖響應(IIR)和自適應濾波器)以及數字上下變頻器。這些算法中,每一種都有一些結構性的元件可以用并行方法實現。而FPGA

2021-12-15 06:30:00

的軟件,變得更加重要。為滿足需求,文中提出一種基于DSP/ BIOS的軟件架構,可提高軟件的可維護性和可重用性,方便算法的裁減添加及程序的跨平臺移植,實現多類信號多路并行處理的軟件快速開發設計。1 DSP

2012-09-03 17:18:51

傳統數字濾波器硬件的實現主要采用專用集成電路(ASIC)和數字信號處理器(DSP)來實現。FPGA內部的功能塊中采用了SRAM的查找表(lo-ok up table,LUT)結構,這種結構特別適用于并行處理結構,相對于傳統方法來說,其并行度和擴展性都很好,它逐漸成為構造可編程高性能算法結構的新選擇。

2019-10-22 07:14:04

DSP并行系統。因為該系列的處理器在構成并行處理系統時其本身就提供了實現互連所需的片內總線仲裁控制和特有的鏈路口,可以以各種拓撲結構互連DSP,滿足大運算量和片間通信靈活的要求。此外,選用ADSP

2019-05-21 05:00:19

的距離塊就可以完成256個單元的計算。把上述結構映射到FPGA上實現,則FPGA上并行32個運算單元,且每1個運算單元具有1個與其他運算單元獨立的復數乘加模塊、寄存器組和1個互相關值輸出鎖存寄存器

2009-09-19 09:25:42

DSU相關的權函數使用,記為fI和fQ;接收回波信號在A/D采樣后,經過正交分解形成數據流rI和rQ,然后對接收數據進行相關操作,即回波數據以流水方式通過相關器與發射樣本數據逐點進行乘加處理。本論

2015-02-05 15:34:43

針對長期演進(LTE)下行正交頻分復用(OFDM)系統的最小二乘(LS)信道估計算法對噪聲比較敏感的問題,提出了一種基于小波變換去噪與變換域插值相結合的信道估計方法。該方法通過在最小二乘(LS)估計

2010-05-06 09:01:31

/20755211100719/1310381718_530721f7.gif]4 FFT復乘的FPGA實現由于軟件和DSP實現的速度較慢,而FPGA資源豐富,組織結構便于采用流水線結構和并行運算,其速度快、擴展能力強

2011-07-11 21:32:29

本帖最后由 mr.pengyongche 于 2013-4-30 03:23 編輯

8核的TMS320C6678款DSP芯片一個周期可

2012-02-18 13:19:36

本帖最后由 mr.pengyongche 于 2013-4-30 03:23 編輯

8核的TMS320C6678款DSP芯片一個周期可

2012-02-18 13:29:59

,圖2-1和第14頁和第16頁的2-2中的原理圖,我注意到乘法路徑具有實現3級流水線所需的寄存器但是,C輸入的datha路徑只能使用2個寄存器。所以我的問題是,我應該在DSP48E1 Block之外添加

2020-07-21 13:52:24

FIFO芯片是什么?如何利用FIFO去實現DSP間雙向并行異步通訊?

2021-06-02 06:08:17

DSP48E1片的數學部分由一個25位的預加器、2個25位、18位的補法器和3個48位的數據路徑多路復用器(具有輸出X、Y和Z)組成,然后是一個3輸入加法器/減法器或2輸入邏輯單元(參見圖2-5

2021-01-08 16:36:32

簡化DSP48E1片操作

2021-01-27 07:13:57

喜據我所知,有些xilinx FPGA具有DSP Slice(DSP48E)。在fpga設計摘要中,我看到切片寄存器,切片LUT,占用切片等以及DSP48E的單獨行。我的問題是 - 1)DSP48E

2019-04-04 06:36:56

值。目前,數字信號處理器(DSP)技術的高速發展為高效媒體處理器的實現提供了可靠的硬件平臺。C64系列DSP是當前TI(Texas Instruments)公司推出的處理能力最高的定點DSP,NVDK

2008-06-25 10:35:31

我一直在嘗試將DSP48E1原語用于具有自動終端計數重置的計數器。大部分工作都很好,但我看到的一個問題是我無法讓DSP48E1進行模式檢測0.如果我將C輸入設置為48'd0,則在P =開始時

2020-07-28 10:38:40

。 Achronix為了解決這一大困境,創新地設計了機器學習處理器(MLP)單元,不僅支持浮點的乘加運算,還可以支持對多種定浮點數格式進行拆分。

2020-11-26 06:42:00

嘿,為了在Zynq設備上對一種算法的不同實現進行簡單比較,我想為每種實現的資源使用創建一個指示符,例如CLB的使用。因此,獲得基本元素CLB,DSP48E1和BRAM36K的面積指標會很好。在

2020-07-25 11:04:42

基于STM32F407-DISCO的低通濾波器的設計

單電源低通加隔值電容

STM32F407自帶DSP硬核和FPU處理單元,對外部輸入的低頻信號

2017-04-16 21:54:33

、譯碼和執行等操作可以重疊執行。 當然,與通用微處理器相比,DSP芯片的其他通用功能相對較弱些。 DSP優勢在于其有獨特乘法器,一個指令就可以完成乘加運算,但GPP(通用處理器)處理一般是用加法代替乘法

2018-12-11 12:05:54

、譯碼和執行等操作可以重疊執行。 當然,與通用微處理器相比,DSP芯片的其他通用功能相對較弱些。 DSP優勢在于其有獨特乘法器,一個指令就可以完成乘加運算,但GPP(通用處理器)處理一般是用加法代替乘法

2019-02-25 16:58:00

操作,使取指、譯碼和執行等操作可以重疊執行。 當然,與通用微處理器相比,DSP芯片的其他通用功能相對較弱些。 DSP優勢在于其有獨特乘法器,一個指令就可以完成乘加運算,但GPP(通用處理器)處理一般是用

2019-05-16 17:06:34

我看書上說現代DSP內置MAC硬核,可以在一個時鐘周期完成取數相乘并累加。實驗如下,例如c=a*b+c;反匯編如下可以看到有七句匯編,先用2個周期取ab值,1個周期相乘,1個周期取c值,1個周期想加

2018-10-10 11:08:14

【摘要】針對以往DOA估計算法中智能天線系統的陣列單元模型多采用全向振子的情況,分析了當天線單元存在方向性時對MUSIC算法估計信號到達角的影響,并在進行陣元互耦校正后

2009-03-14 15:12:51 18

18 基于VxWorks的多DSP并行處理系統的實現

2009-03-29 12:31:18 17

17 High DSP Performance Platform– The DSP48E Slice– Essential DSP Building Blocks• Imaging Algorithms

2009-04-09 22:05:31 12

12 本文針對CDMA 系統,提出使用DSP 器件TMS320C6701 實現對CDMA 信號的波達方向估計。該算法基于對解擴前后相關陣相減,去除了干擾相關陣是,然后使用傳統MUSIC或ESPRIT 算法進行DOA 估

2009-06-18 09:13:09 16

16 本文針對CDMA 系統,提出使用DSP 器件ADSP21160 實現對感興趣用戶的波達方向和多徑時延進行聯合估計的算法。該算法是對傳統MUSIC 方法的推廣與變形,克服了要求接收信號數小于陣

2009-08-26 08:55:22 11

11 信道估計是RAKE 接收機的關鍵技術,WCDMA 中可采用時分復用導頻完成,給出了用DSP 的具體實現方案。關鍵詞:DSP;信道估計;WCDMA

2009-09-15 09:36:23 28

28 PC機與DSP之間的并行通訊技術

摘要:對PC 機在EPP 模式下與C6000 系列DSP 的HPI 口之間進行的并行通訊進行了研究,提出了用EPP 協議和CPLD 實現DSP 與計算機并口

2010-04-07 14:37:06 35

35 基于TMS320C6416高性能通用DSP,實現了對AWGN信道的信噪比(SNR)估計,并以此估計值設計了一種低密度奇偶校驗(LDPC)碼的譯碼系統;詳盡介紹了集成SNR估計的譯碼系統的實現方案和流程;仿真

2010-07-27 16:28:32 11

11 摘要:提出了一種巧妙實現DSP并行自舉的方法,即采用“兩次下載法”,利用DSP自身對FLASH編程,以實現DSP的并行自舉。這種在系統編程的DSP自舉實現方式無需文件

2006-03-11 17:39:50 1400

1400

帶有飽和處理功能的并行乘加單元設計

本文介紹了一種48bit+24bit×24bit帶飽和處理的MAC單元設計。在乘法器的設計中,采用改進的booth 算法來減少部分積的數目,用由壓縮單

2009-03-28 16:28:58 1598

1598

在水下日標檢測和跟蹤系統中,多目標方位估計算法起著重要的作用.MUSIC算法是最具代表性的方法}為了滿足目標方位估計對高速變時并行處理技術的要求,針對水下陣列信號處理的實

2011-10-12 16:19:54 41

41 介紹了時差測向的基本原理,其關鍵在于對時差的測量,因此主要工作即為對跳頻信號進行時差測量。基于信道化方法對跳頻信號進行時差估計具有較高的精度,可以在FPGA中實現。

2012-02-08 15:12:58 34

34 基于ADSP_TS201S的多DSP并行系統設計

2015-12-29 17:33:04 22

22 題(1):使用DS48E1的SIMD功能實現四路并行12位加法”,要求數據從不同的DSP48端口進去。 評分標準: 1)使用Vivado 仿真通過 2)使用7A50T板子,使用Vivado硬件實現且記錄波形,或者,使用Matlab sysgen硬件仿真,或者其他硬件實現方式且有硬件結果 軟件環境:

2017-02-07 20:23:33 2159

2159 TMS320VC5416DSP并行自舉方案的設計與實現

2017-10-20 09:15:22 12

12 DSP通過FLASH并行加載的分析和實例

2017-10-20 10:15:16 7

7 DSP并行系統的并行粒子群優化目標跟蹤

2017-10-20 10:54:00 6

6 介紹了利用CYPRESS公司的FIFO芯片CY7C419實現DSP間雙向并行異步通訊的方法,該方法簡單實用,速度快,特別適用于小數據量的數據相互傳送。文中給出了CY7C419的引腳功能以及用FIFO

2017-10-25 11:35:25 0

0 根據BPSK調制信號調制機理和平方倍頻法原理,在FPGA平臺上設計實現了BPSK調制信號載波頻率估計單元。利用ModelSim仿真環境對載頻估計功能進行仿真,驗證了平方倍頻法對BPSK信號進行載波

2017-11-18 05:13:05 3576

3576

針對均勻線性陣列DOA估計中的實時性和解相干問題,提出了一種基于單次快拍數據的估計算法,通過對陣列接收的單次快拍數據進行相關處理后重構Toeplitz矩陣,并證明該矩陣的秩不受信號相干性的影響。通過

2018-03-06 10:57:38 0

0 更加多樣化。DSP48基本結構如下圖所示(圖片來源:ug073, Figure 2-1)。DSP48中的核心單元是18x18的乘法器。從圖中不難看出,DSP48可實現基本數學函數P=Z(X+Y+CIN

2020-10-30 17:16:51 5768

5768

A、B、C、CARRYIN、CARRYINSEL、OPMODE、BCIN、PCIN、ACIN、ALUMODE、CARRYCASCIN、MULTSIGNIN以及相應的時鐘啟用輸入和復位輸入都是保留端口。D和INMODE端口對于DSP48E1片是唯一的。本節詳細描述DSP48E1片的輸入端口

2022-07-25 18:00:18 4426

4426

擴頻碼的相關解擴是擴頻通信接收機的關鍵技術之一,主要介紹了數字相關器在全球定位系統(GPS)信號捕獲中的應用,并進行了FPGA實現。在設計中,采用了16路并行相關運算的方式加快相關解擴運算速度

2021-01-26 16:22:43 15

15 在DSP48E1列中,級聯各個DSP48E1片可以支持更高級的DSP功能。兩個數據路徑(ACOUT和BCOUT)和DSP48E1片輸出(PCOUT、MULTSIGNOUT和CARRYCASCOUT)提供級聯功能。級聯數據路徑的能力在過濾器設計中很有用。

2021-01-27 07:34:32 8

8 A、B、C、CARRYIN、CARRYINSEL、OPMODE、BCIN、PCIN、ACIN、ALUMODE、CARRYCASCIN、MULTSIGNIN以及相應的時鐘啟用輸入和復位輸入都是保留端口。D和INMODE端口對于DSP48E1片是唯一的。本節詳細描述DSP48E1片的輸入端口

2021-01-27 08:18:02 2

2 DSP48E1片的數學部分由一個25位的預加器、2個25位、18位的補法器和3個48位的數據路徑多路復用器(具有輸出X、Y和Z)組成,然后是一個3輸入加法器/減法器或2輸入邏輯單元(參見圖2-5)。使用2輸入邏輯單元時,不能使用乘法器。

2021-01-29 08:19:37 13

13 在定位系統的時差提取方法中,傳統的互相關算法抗噪能力較弱、時差提取精度較低,針對以上缺點,提出卡爾曼-最優階互相關算法,并且通過仿真對比分析相同條件下該算法和基本互相關算法、廣義加權互相關算法的時差

2021-06-18 11:28:06 16

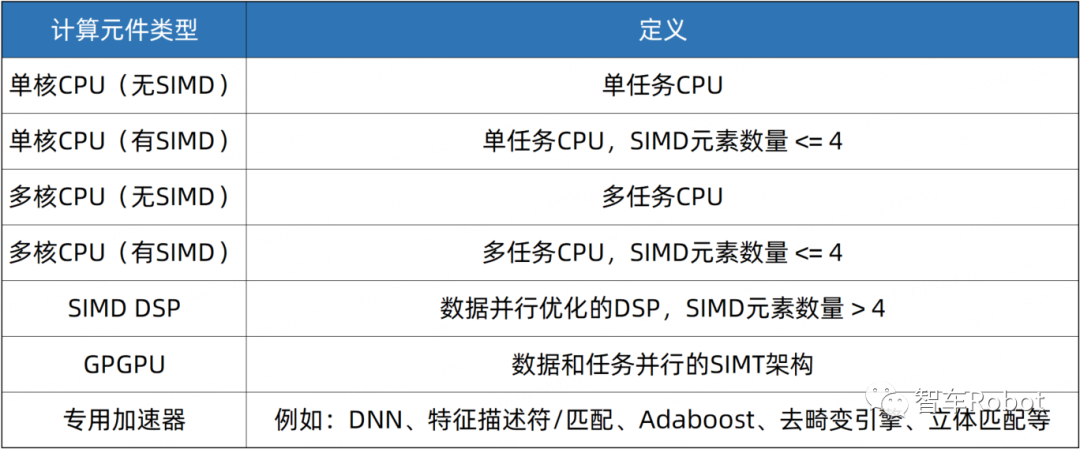

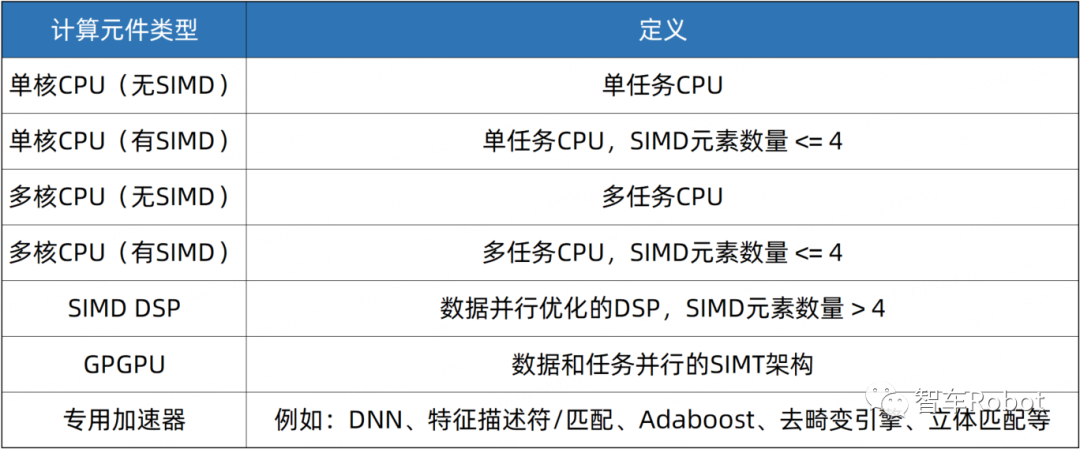

16 元件,如通用CPU、SIMD DSP、GPGPU和專用加速器等。 計算元件特性 ?通用CPU適合運行順序代碼和有限的數據并行。 ?SIMD DSP處理更數據密集的任務。 ?GPGPU也可以處理高數據量和控制順序靈活的任務。 ?專用加速器針對特定操作實現最高執行效率

2023-10-04 10:34:00 262

262

電子發燒友App

電子發燒友App

評論