在自適應光學系統中,哈特曼波前傳感器檢測到的波前信息通過高速CCD相機采集輸出,然后由波前處理機完成斜率計算、波前復原運算和控制運算。自適應光學系統研制時,為了縮短研制周期,哈特曼傳感器和波前處理機需要同步進行設計和研制,以便同步完成后進行系統集成調試。

然而,通常都要等到哈特曼傳感器研制完成,并且配合必要的光學系統之后,才能輸出子光斑圖像給波前處理機進行調試。這樣給波前處理機的研制周期帶來了很大壓力。因此,如果可以建立一個模擬前端系統哈特曼傳感器作為子光斑圖像輸出的信號源,則可以簡化波前處理機對調試環境的要求、縮短其研制周期。本文以XC2V1500-FPGA和K9F1G16UOM-FLASH ROM為載體,設計了一種模擬哈特曼傳感器中CCD相機圖像輸出的信號發生器。該系統不僅能為波前處理機的調試提供信號源,而且還可以為已經研制完成的波前處理機提供算法驗證的支持。

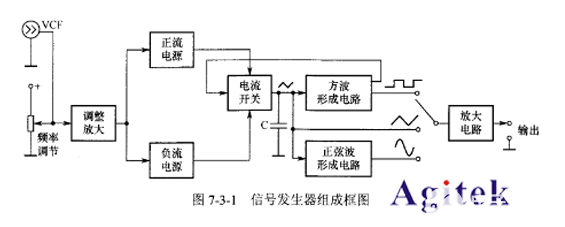

1、系統原理及組成

該圖像信號發生器的基本原理如下:通過模擬產生CCD相機輸出控制時序,將特定圖像進行循環播放輸出。目標圖像數據可通過PC機進行加載,并且需要進行非易失性存儲。這樣在完成圖像加載之后,系統一經啟動就能夠將圖像數據按照要求進行輸出。目標圖像按要求均是灰度圖像,可以是單幀、也可以是多幀,可以是從相機采集而來,也可以是通過Matlab仿真模擬得到的。選擇載入不同的目標圖像序列,則系統可以完成不同的需求任務。

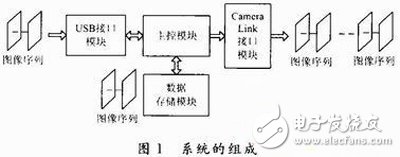

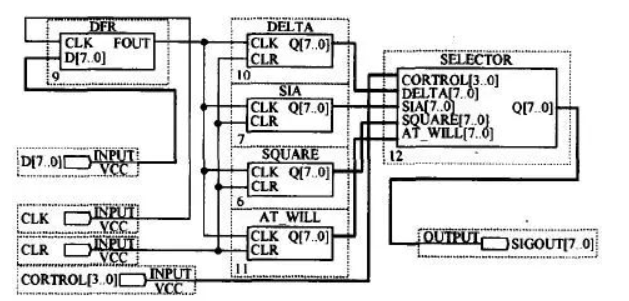

系統組成如圖1所示,主要由主控模塊、USB接口模塊、數據存儲模塊和Camera Link接口模塊組成。

?

主控模塊由一片XC2V1500-FPGA來實現。CY7C68013A芯片組成USB接口模塊,實現PC機與系統的通信功能。8片并行K9F1G16UOM-FLASHROM芯片組成數據存儲模塊,可提供1 GB的存儲空間、良好的讀寫速度。對于Camera Link接口模塊,采用3片DS90CR287、1片DS90LV019和1片DS90LV048A來實現,可以支持Carnera Link接口的初級配置(Base)、中級配置(Medium)和高級配置(Full)。Camera Link接口是一種應用最廣泛的高幀頻相機接口,具有差分傳輸、傳輸速率高的特點。

系統的任務可以分為兩個過程:首先PC機通過USB總線和FPGA將目標圖像序列寫入FLASH;然后由于FLASH是一種非易失存儲器,接下來系統一旦啟動后FPGA就能夠模擬產生CCD相機時序、將FLASH中的數據進行循環輸出。這兩個過程的實現可加載不同的FPGA程序來完成。

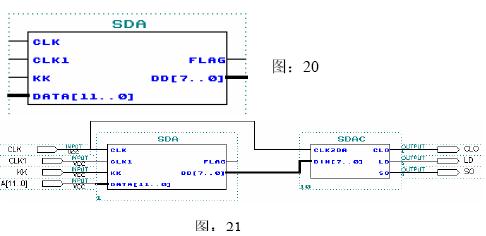

2、系統實現

2.1、USB接口模塊

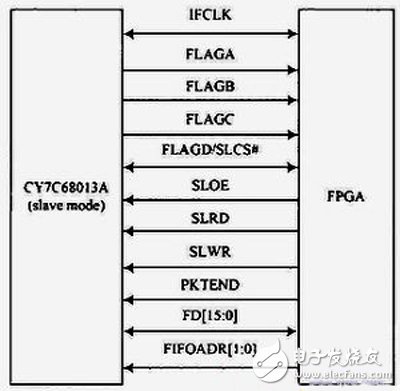

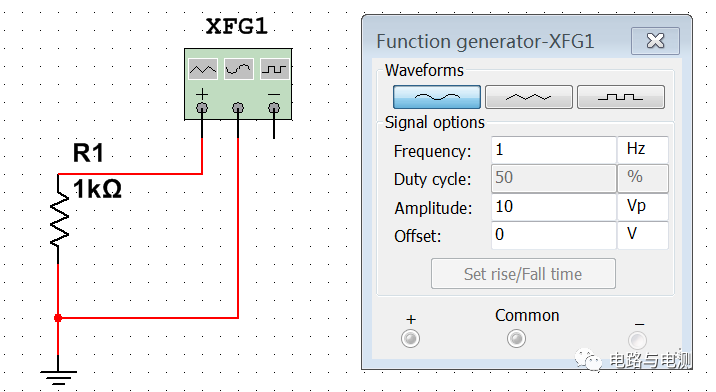

USB接口具有傳輸速度快、即插即用等優點,所以使用USB來實現PC機與系統的通信。CY7C68013A作為USB 2.0控制器,有3種接口工作模式:Ports,Slave FIFO和GPIF。根據系統構成和實際要求,選用Slave FIFO模式的數據傳輸方案。具體的硬件連接如圖2所示。

?

圖2 Slave FIFO模式的硬件連接圖

CY7C68013A通過固件編程來配置具體的功能。應用程序通過USB驅動程序建立與USB外部設備的聯系。本文采用了Cypress公司提供的通用驅動CyUsb.sys,該驅動程序完全滿足本系統設計的要求。應用程序可以通過兩種方式來訪問CyUsb.sys:

(1)使用Windows API如SetupDiXxxx和Deviceio Control;

(2)使用Cypress公司提供的CyAPI.lib。

本文采用CyAPI.lib來訪問USB驅動,CyAPI.lib提供了簡單高效的與Cyusb.sys通信的方法,方便掌握、可有效縮短USB設備的開發周期。

在完成圖像數據寫入功能時,FPGA接收到圖像數據寫入的命令后,使faddr地址指向用于下傳數據的端點FIFO,然后開始獲取來自USB控制器的數據,FPGA內部USB通信模塊工作情況如圖3所示。IFCLK是由FPGA提供的40MHz時鐘,CY7C68013A的端點FIFO被配置為同步工作。

圖3 CY7C68013A的工作時序

2.2、FLASH ROM無效塊管理

選取 SAMSUNG 公司的 NAND 型的K9F1G16UOM-FLASH作為存儲芯片,單片容量為1 Gb、數據寬度為16 b。大容量的FLASH器件一般都是按塊(block)管理其存儲空間。FLASH芯片可能有包含一個或多個無效位的無效塊,這在NAND型FLASH中是不可避免的。無效塊出現的幾率很小,但影響很大。如果對FLASH中的無效塊進行操作,無效塊會在數據記錄的過程中造成數據的丟失和誤碼,影響數據的有效性和完整性。由于無效塊和有效塊相互隔離,無效塊并不會影響有效塊的操作,因此只要在數據存儲前將FLASH中的無效塊剔除,就可有效避免數據的丟失和誤碼。

FLASH在出廠時會對無效塊進行檢查,并將信息標注在FLASH每一塊的第一頁和第二頁的第1 024個字,0xFFFF表示塊有效。非0xFFFF則表示無效塊。為避免破壞這些標注信息,在對FLASH進行任何擦除或寫入操作前,要首先建立無效塊信息表。SAMSUNG公司保證其FLASH的第一塊一定是有效塊,并且在對其擦寫1 000次以內不會出任何錯。所以本文使用該塊來保存整片FLASH的無效塊信息。FPGA遍歷訪問FLASH中的每個塊的第一頁和第二頁,判斷該塊是否滿足有效塊的要求,若不滿足則將其塊地址緩存到FPGA的RAM中;接下來,將FLASH的無效塊數量和無效塊地址存入該片FLASH的第一塊的第一頁內。在FLASH的使用過程中,仍然有可能產生新的無效塊,當出現這種情況時,則需要更新無效塊信息表。無效塊信息表用來供讀寫地址產生器查詢時使用,這樣就可以避開壞塊的影響。

2.3、數據寫入管理

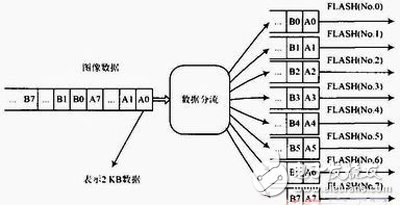

圖像數據寫入時,FPGA接收來自USB控制器的數據,并產生控制時序將數據寫入FLASH。由于高幀頻相機一般是多通道輸出,所以在模擬這類相機的時候要注意這個因素。對于某一幅目標圖像,圖像數據寫入首先是應用程序獲取圖像數據;然后將各個通道對應位置的像素數據按次序調整在一起;接著通過USB將數據傳輸至FPGA,FPGA將數據截斷成2 KB大小并依次將各分段數據塊寫入8片FLASH中,數據分流如圖4所示。圖像數據按通道進行調整可以使得系統輕松地實現多通道輸出。對數據的分流處理,使得系統的8片FLASH在讀出時可以真正實現并行讀取數據。

?

圖4 數據分流示意

FLASH的一頁(page)的大小為2 KB,也是它的基本瀆寫單元。要想連續寫入2 KB的數據,需要將訪問FLASH的頁地址都設為00H。當FPGA需要向某一片FLASH寫入數據時,首先要查看該片FLASH的FPGA寫入管理模塊是否處于ready狀態;若處于busy狀態,則應用程序進入傳輸等待,當寫入管理進入ready狀態后,則應用程序發送數據,一共2 KB數據緩沖到FLASH在FPGA中對應的RAM;數據緩沖完成之后,該FLASH的寫入管理模塊進入busy狀態并開始將RAM中的數據寫入FLASH ROM的某一頁(page),同時FPGA轉向對下一片FLASH進行傳輸訪問。

2.4、數據讀出管理

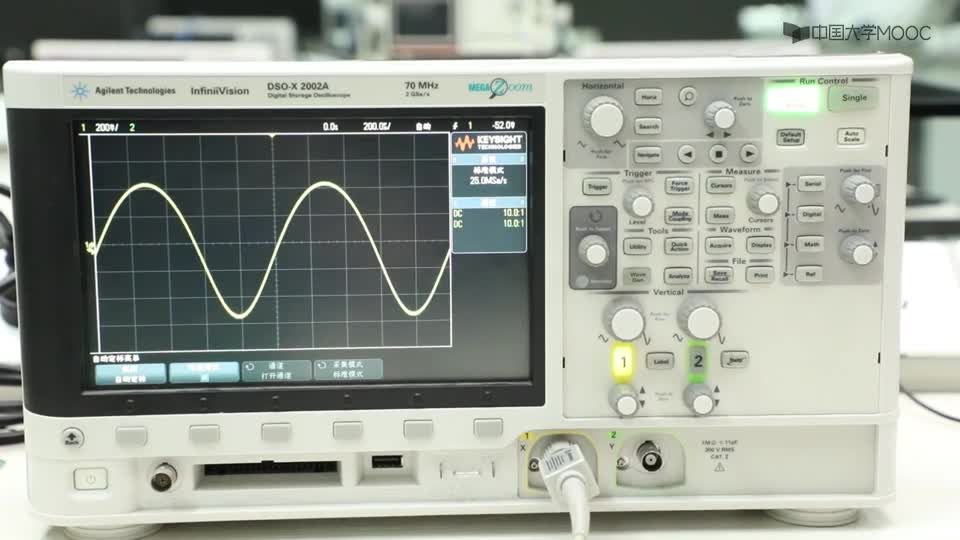

數據讀取輸出是指FPGA模擬CCD相機輸出時序,將FLASH中的數據通過Camera Link接口進行循環輸出。所選的FLASH的單片最大讀出速率可達25 MB/s,由于8片FLASH可以并行讀出,所以整個系統的數據讀出率可以達到200 MB/s。這樣有利于模擬出較高幀頻的CCD相機輸出。當系統進行圖像數據瀆取輸出時,FPGA中設置了FIFO來緩沖數據。Camera Link輸出管理模塊產生相機時序,將FIFO中的數據按要求送到Cam era Link接口。對于從FLASH向FIFO轉移數據,首先將各FLASH中的2 KB數據被讀入其在FPGA中對應的RAM中;然后控制各RAM中的數據被按順序轉移至FIFO中,控制器通過FIFO的數據深度來判斷是否需要繼續讀入數據,當判斷FIFO中的數據快滿時暫停讀取,這時由于數據繼續被讀出,隨著FIFO中的數據減少到一定程度時,啟動將RAM中的數據繼續讀入FIFO;一旦一個RAM中的數據被轉移,則FLASH讀取管理模塊繼續將該FLASH中的后續數據寫入該RAM。

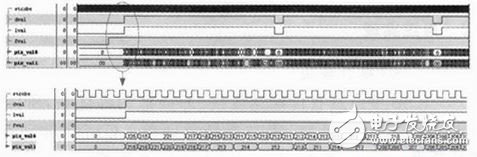

?

圖5 Camera Link接口輸出信號

在加載某種8位數據寬度、雙通道輸出的目標圖像時,使用Chipscope得到的Camera Link信號如圖5所示。其中,strobe為時鐘信號,dval,lval,fval分別是數據有效、行有效、幀有效信號。觀測結果說明輸出的數據與加載的數據保持一致,輸出控制時序也符合要求。

為了模擬出不同類型的CCD相機,只需要修改FPGA程序中設定的strobe時鐘頻率、Line blanking時間、Frame blanking時間等必要參數即可。

3、實驗結果與分析

系統實物圖如圖6所示。

?

圖6 系統實物圖

為了檢測該信號發生器的性能,將其輸出接入圖像采集卡進行驗證。經過試驗驗證,FLASH ROM中存儲的圖像數據與從PC機載入的數據完全一致、控制時序符合設計要求。通過改變Strobe的頻率大小,驗證得到Camera Link輸出的像素時鐘頻率最大可以達到70 MHz。對于尺寸為128×128、位寬為8 b的目標圖像,在采用40 MHz的Strobe時鐘進行單通道輸出時,幀頻可以達到1 876 f/s。對于尺寸為512×512、位寬為8 b的目標圖像,當Strobe時鐘為70 MHz,單通道輸出時,幀頻可以達到252 f/s;雙通道輸出時,幀頻可以達到476 f/s。該信號發生器可以模擬目前大部分波前處理機所需的信號源。在進行單通道或雙通道輸出時,系統可以充分利用Camera Link接口的輸出能力。但是當進行更多通道的輸出時,由于受限于FLASH的讀出速率,該系統不能充分應用Camera Link接口的輸出能力。對于這個缺陷,在對系統進行改進時可以通過使用FLASH ROM和高速大容量RAM共同組成數據存儲模塊來解決。

4、結論

根據本文介紹的設計方案,采用FPGA技術設計的圖像信號發生器結構簡單,實現方便,易于修改。FLASH ROM提供了較高的數據讀出速率,支持系統能夠模擬出較高幀頻的CCD相機輸出。經過試驗驗證,系統工作穩定,達到了設計要求。

電子發燒友App

電子發燒友App

評論