摘要: 文中介紹了一種基于FPGA的數字秒表設計方法。采用VHDL硬件描述語言, 運用ModelSim等EDA仿真工具。該設計具有外圍電路少、集成度高、可靠性強等優點。最后經實驗驗證, 該數字秒表計時準確, 輸入信號能準確控制秒表運行。系統所采用的自上而下的模塊化設計方法, 對于其他復雜的系統設計也有很強的借鑒意義。

數字集成電路作為當今信息時代的基石, 不僅在信息處理、工業控制等生產領域得到普及應用, 并且在人們的日常生活中也是隨處可見, 極大的改變了人們的生活方式。面對如此巨大的市場, 要求數字集成電路的設計周期盡可能短、實驗成本盡可能低, 最好能在實驗室直接驗證設計的準確性和可行性, 因而出現了現場可編程邏輯門陣列FPGA。對于芯片設計而言, FPGA的易用性不僅使得設計更加簡單、快捷, 并且節省了反復流片驗證的巨額成本。對于某些小批量應用的場合, 甚至可以直接利用FPGA實現, 無需再去訂制專門的數字芯片。

文中著重介紹了一種基于FPGA利用VHDL硬件描述語言的數字秒表設計方法, 在設計過程中使用基于VHDL的EDA工具ModelSim對各個模塊仿真驗證, 并給出了完整的源程序和仿真結果。

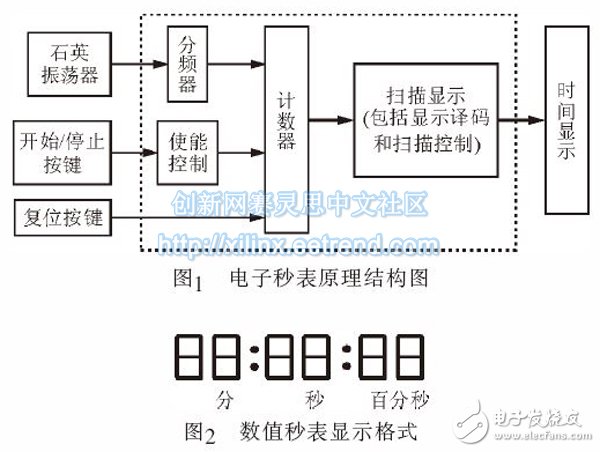

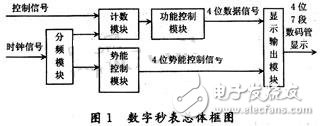

1 總體功能結構設計

一個完整的數字秒表應具有計時、相應的控制以及計時結果顯示功能, 總體的功能結構如圖1所示。黑色線框內是計數模塊、使能轉化模塊和顯示譯碼模塊, 左邊是輸入控制信號, 右邊是顯

示計時結果的數碼顯示管, 用六位BCD七段數碼管顯示讀數, 顯示格式如圖2, 計時范圍為: 1小時,精度為0.01s。

輸入時鐘信號由32MHz的石英晶振提供, 考慮到設計指標要求秒表精度為0.01秒, 計數脈沖的時

鐘輸入就應該是頻率為100Hz的脈沖, 所以先要設計一個320000分頻器, 分頻器的輸出可作計數器的輸入; 其次計數模塊設計應綜合考慮秒表的計時范圍(1小時) 和顯示輸出(6位輸出), 6位輸出中有兩位是六進制輸出, 其余四位是十進制輸出,所以可通過設計4個模10計數器和2個模6計數器來實現, 其中較低位的進位輸出就是高位的計數輸入端。

控制模塊應包括開始計時/停止計時、復位兩個按鈕, 即電路設計經常用到的使能端和清零端,這兩個控制端口直接接到計數器的清零和史能端即可實現復位、開始計時/停止計時; 但是外圍使能輸入需要經過使能轉換電路后, 才可變為計數器可用的使能控制信號。因此在輸入使能信號和計數器使能輸入之間需設計一個信號轉換模塊。

顯示計數結果的模塊實現較為簡單, 只需將六位計數結果通過七段譯碼電路接到輸出即可點亮數碼管, 無需時序控制, 直接用組合邏輯電路就可以實現。數碼管顯示可以采用掃描顯示, 用一個頻率1KHz的信號掃描一個多路選擇器, 實現對六位已經鎖存的計數結果的掃描輸出。

2 各功能模塊設計

2.1 分頻器模塊

分頻器的功能是提供標準時鐘控制信號以精確控制計數器的開閉, 提供的標準信號是32MHz,根據設計精度0.01s的要求, 輸出信號是100Hz, 所以該分頻器實現的功能是320000 分頻, 具體的

VHDL源程序:

process (clk)

begin

if (clk'event and clk='1') then

if (q=159999) then

q<=0;

count_temp<=not count_temp;

else

q<=q+1;

end if;

end if;

end process;

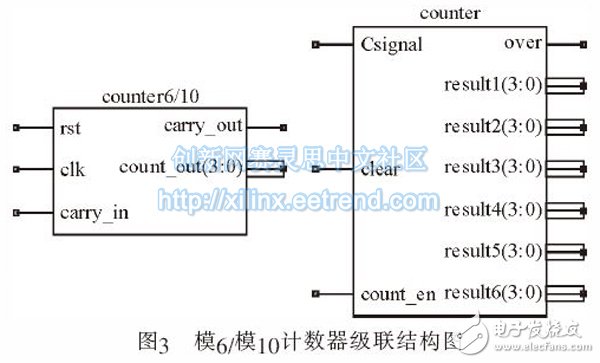

2.2 計數模塊

該計數器要實現最大計數值為59分59秒99的計數, 而且為了數碼管顯示方便, 該模塊必須通過計數器的級聯來實現, 即首先分別設計一個模6計數器和一個模10計數器, 然后將他們級聯, 其中調用4次模10計數器、2次模6計數器, 這樣可以比直接設計模100 的計數器和模60的計數器節省資源。級聯時低位的計數進位輸出接高位的計數輸入端, 如圖3所示。再考慮到控制模塊的要求, 每個計數器有三個輸入端: 時鐘、使能和清零, 兩個輸出端: 計數輸出和進位輸出, 采用同步使能異步清零的設計方法, 每個計數器的使能和清零端都與外圍的使能和清零端相聯。

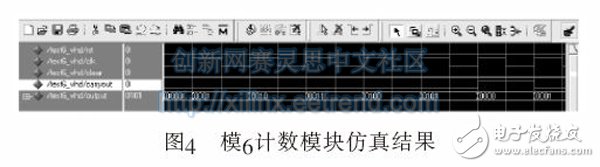

該模塊的源程序以及ModelSim仿真輸出結果如下:

模6計數器的VHDL源程序如下:

process (clear,clk)

begin

if (clear='1') then

tmp<=" 0000" ;

carryout<='0';

elsif (clk'event and clk='1') then

if (rst='0') then

if (tmp=" 0101") then

carryout<='1';

tmp<=" 0000" ;

else

tmp<=tmp+1;

carryout<='0';

end if;

end if;

end if;

模10計數器的VHDL源程序與模6計數器類似,為節省篇幅, 不再給出。

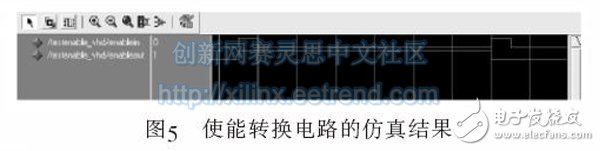

2.3 使能信號轉換模塊

數字秒表輸入的開始和停止信號是單個脈沖信號, 而計數器要持續計數所需的使能信號是持續的高電平, 所以需要通過使能控制電路實現使能信號的轉換。該模塊的VHDL源程序以及Model-Sim仿真輸出結果如下:

該模塊源程序:

process (enablein)

begin

if (enablein'event and enablein='1') then

temp<= not temp;

end if ;

end process;

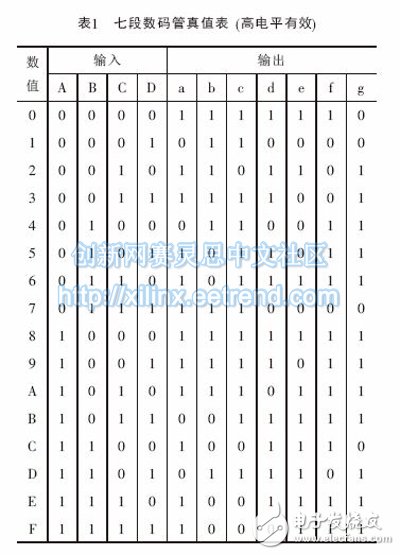

2.4 譯碼顯示模塊

由上面的設計可知, 計數器輸出為二進制碼,不能直接點亮數碼管, 要想將計數結果通過數碼管顯示必須再設計一個七段譯碼電路, 以便將計數結果輸出。通過分析可知該譯碼器是一個4輸入, 7輸出元件, 其真值表如表1所示:

根據以上真值表可寫出譯碼電路VHDL源程序如下:

process (datainput)

begin

case datainput is

when " 0000" =>dataoutput<=" 0000010" ;

when " 0001" =>dataoutput<=" 1001111" ;

when " 0010" =>dataoutput<=" 0010001" ;

when " 0011" =>dataoutput<=" 0000101" ;

when " 0100" =>dataoutput<=" 1001100" ;

when " 0101" =>dataoutput<=" 0100100" ;

when " 0110" =>dataoutput<=" 0100000" ;

when " 0111" =>dataoutput<=" 0001111" ;

when " 1000" =>dataoutput<=" 0000000" ;

when " 1001" =>dataoutput<=" 0000100" ;

when others=>dataoutput<=" 1111111" ;

end case;

end process;

3 功能驗證以及下載實現

完成以上各個子模塊的設計后, 該數字秒表的模塊設計就基本完成了, 剩下的工作就是通過一個頂層文件將各個子模塊連接起來。在頂層文件中可以將以上各個子模塊看作一個個黑匣子,只將其輸入輸出端對應相連就可以了。下面是該頂層文件的VHDL源程序:

architecture Behavioral of topfile is

signal clk:std_logic:='0';

signal enableout:std_logic:='0';

signal data0,data1,data2,

data3,data4,data5:std_logic_vector (3

downto 0) :=" 0000" ;

component abc

port (clk:in std_logic;

dout:out std_logic) ;

end component;

component enable

port (enablein:in std_logic;

enableout:out std_logic) ;

end component;

component highlevel

port (rst,clk,clear:in std_logic;

output1,output2,output3,

output4,output5,output6:out

std_logic_vector (3 downto 0) ;

carryout:out std_logic) ;

end component;

component yima

port (datainput:in std_logic_vector (3 downto 0) ;

dataoutput: out std_logic_vector (6 downto 0)) ;

end component;

begin

u0:abc port map (clkin,clk) ;

u1:enable port map (enablein,enableout) ;

u2:highlevel port map ( enableout,clk,clear,data0,data1,

data2,data3,data4,data5) ;

u3:yima port map (data0,dataout0) ;

u4:yima port map (data1,dataout1) ;

u5:yima port map (data2,dataout2) ;

u6:yima port map (data3,dataout3) ;

u7:yima port map (data4,dataout4) ;

u8:yima port map (data5,dataout5) ;

end Behavioral;

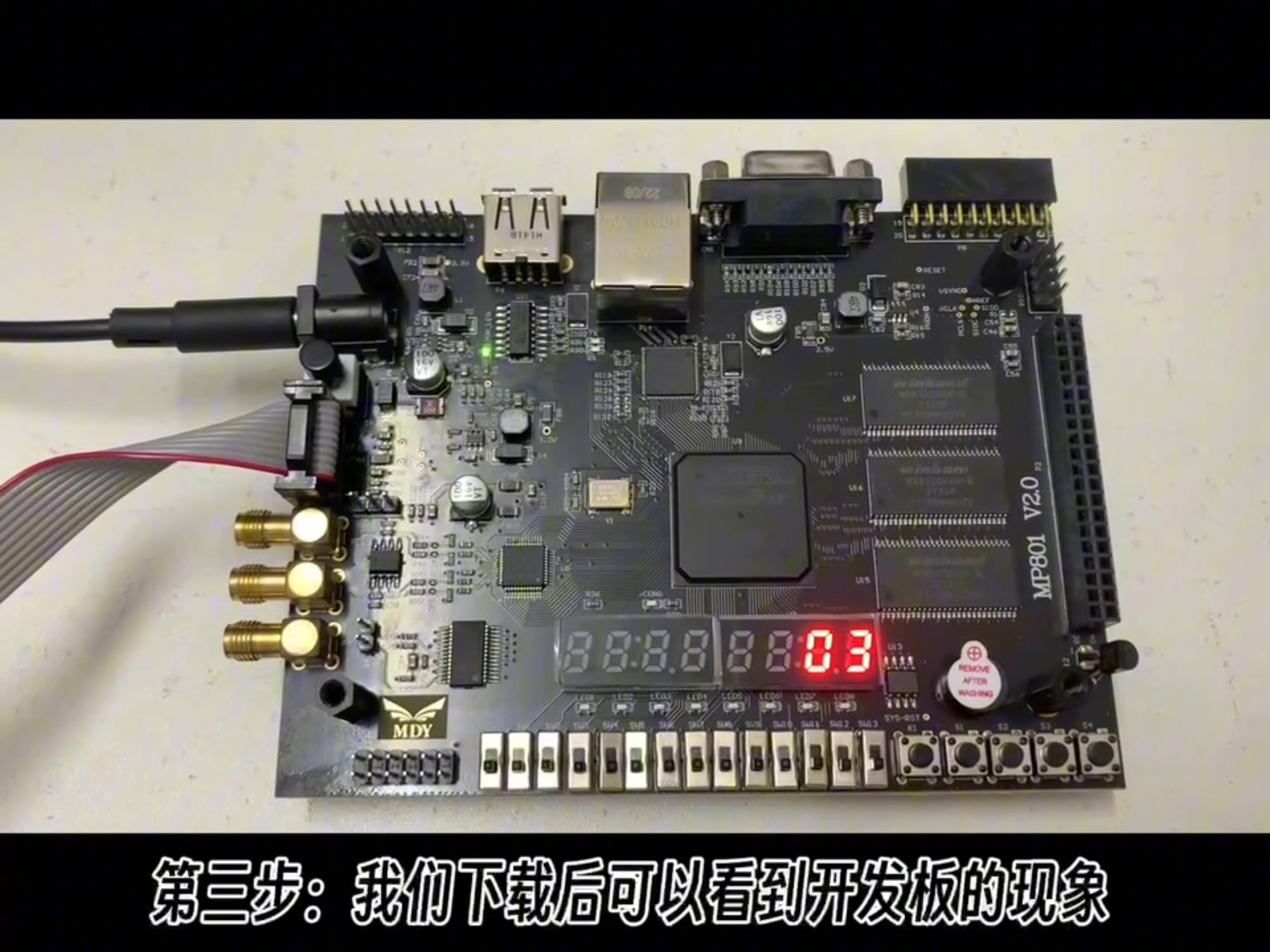

由于各個子模塊都已經經過驗證無誤, 并且頂層文件中不涉及復雜的時序關系, 相當于只是將各個模塊用導線連接起來, 只要各個端口的連接對應正確即可, 所以不需寫專門的test bench進行驗證。完成以上設計后, 即可進行邏輯綜合,綜合無誤后進行管腳適配, 生成.bit文件然后下載到實驗板上測試。經過反復多次測試, 以上設計完全滿足了預期的設計指標, 開始/停止按鍵和清零按鍵都能準確的控制秒表的運行, 七段顯示數碼管也能夠準確的顯示計時結果。通過與標準秒表對比, 該設計的計時誤差在0.03s以內, 而這其中也包括實驗板上晶振由于長期使用所帶來的誤差。

4 結束語

本文所介紹數字秒表設計方法, 采用了當下最流行的EDA設計手段。在Xinlinx FPGA開發環境下, 采用至上而下的模塊化設計方法, 使得系統開發速度快、成本低、系統性能大幅度提升。通過實驗驗證, 本文設計的數字秒表計時準確、性能穩定, 可以很容易嵌入其他復雜的數字系統,充當計時模塊。

利用EDA設計工具, 結合基于FPGA的可編程實驗板, 輕松實現電子芯片的設計, 現場觀察實驗結果, 大大縮短了產品的設計周期和調試周期,提高了設計的可靠性和成功率, 體現了邏輯器件在數字設計中優越性。

電子發燒友App

電子發燒友App

評論