1. 介紹

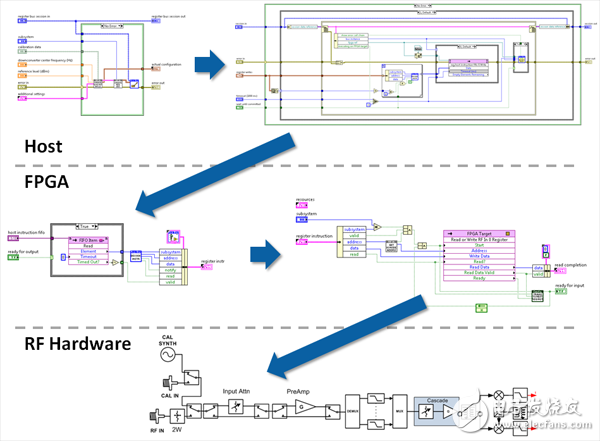

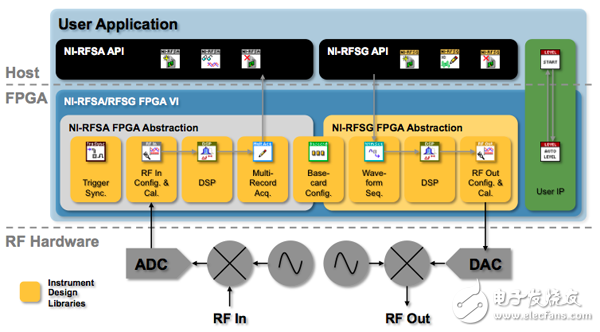

NI VST FPGA軟件包含多層代碼,提供了從底層控制到高層抽取的一切,擁有RF信號分析儀和RF信號發生器的功能。底層組件實現了具體硬件的標準功能,包括信號校準、前端控制,以及基于記錄的采集和生成,被稱為儀器設計庫。這些庫提供了互相匹配的主機和FPGA代碼對,并且可以聚集以構建完整的硬件設計。LabVIEW項目樣例包含了基于儀器設計庫的相關主機和FPGA代碼,提供了開發各種應用所需要的模板。另外,NI-RFSA和NI-RFSG儀器驅動還支持VST儀器驅動FPGA擴展,使VST FPGA源代碼完美適合具體應用。

2. 儀器設計庫

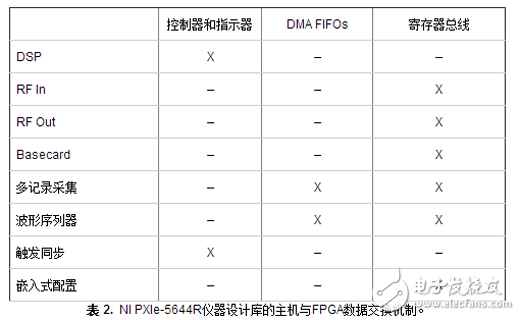

NI提供矢量信號收發器所用的多種儀器設計庫。如上文所述,這些儀器設計庫存在于用戶和生產廠商的關于主機端和FPGA的代碼中,,實現了儀器的常見功能。表2列出了一些頂層儀器設計庫及其功能。

?

ni.com/vst/getting-started/zhs/所列軟件安裝了這些儀器設計庫,在硬盤的 c:Program FilesNational InstrumentsLabVIEW [version]instr.lb位置。這些庫具有顏色和諧的粗邊框,與其他VI明顯有別。

?

圖1:儀器設計庫具有顏色和諧的粗邊框,此獨特圖標使其與其他VI相區別

另外,這些庫在默認情況下處于鎖定狀態,用戶在修改內容之前,需要先通過會話框將VI解鎖。下文所述是使用這些儀器設計庫的詳細信息,適用于任何更改。

在給定儀器設計庫的主機與FPGA之間交換數據可采用多種機制。所有采用LabVIEW RIO架構和LabVIEW FPGA的NI產品均使用NI-RIO驅動,此驅動提供了單點方式的、存儲器映射、基于寄存器的主機至FPGA以及FPGA至主機通信,還有從主機至FPGA以及FPGA至主機的多點連續DMA FIFO。這些都是功能強大的數據交換機制,實現主機與FPGA之間的有效通信不需要了解或者只要些許了解底層總線架構。

儀器設計庫的一個常見要求是:主機代碼需要將大量的設置下載到設備中,例如要對與FPGA相連接的芯片寄存器進行編程,或者更新設置組,例如FPGA上的濾波器抽頭。由于一些儀器設計庫要求采用此策略,并且設備的DMA通道數目有限,所以這些庫可能需要共享一個FIFO,從而需要在主機端和FPGA端增加額外的邏輯來實現。另外,對于大數據集來說,此類通信一般為單向,但是可能也需要提供從FPGA至主機的某種單點確認,例如確認所有設置均已成功應用等等。所有這些概念組成為一個單獨概念,稱為寄存器總線,并為一些儀器設計庫所采用。

寄存器總線使用一個主機到FPGA端的 DMA FIFO來下載設置,以及一些寄存器/NI-RIO控制器和指示器,用于握手,將單點數據返回主機,或者發出信號,確認已下載設置中的指令已經應用。

?

圖 2. 寄存器總線是基于NI-RIO DMA、控制器和指示器構建的輕質協議,實現了大量設置組至FPGA的高效下載,這是給定儀器設計庫的主機與FPGA側之間的常見要求。

為了完成仲裁,每個儀器設計庫均有一個獨一無二的子系統ID,從而使得多個庫能夠共享一條寄存器總線。為了更好地總結VST儀器設計庫的通信策略,表2說明了每個庫所采用的策略。

?

?

另外,通過與嵌入式配置儀器設計庫配合使用,寄存器總線還可以在不牽涉主機的情況下完成FPGA觸發的重新配置。

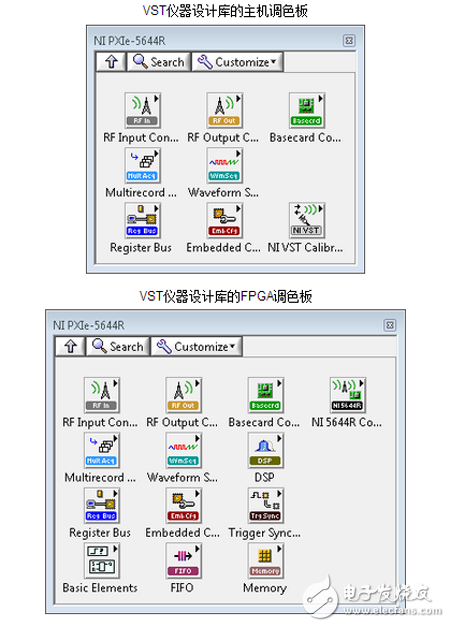

由于儀器設計庫代表了賣主與用戶代碼之間的已定義接口,所以位于主機和FPGA兩者的調色板上。在LabVIEW VI方塊圖的主機情境下,儀器設計庫的主機側接口見于Functions>>FPGA Interface>>NI PXIe-5644R 或者 Functions>>FPGA Interface>>NI PXIe-5645R。在FPGA側,則位于Functions>>NI PXIe-5644R 或者 Functions>>NI PXIe-5645R下。

?

?

圖 3. NI VST儀器設計庫的主機和FPGA調色板。FPGA調色板包含了實現常用底層功能的其他儀器設計庫

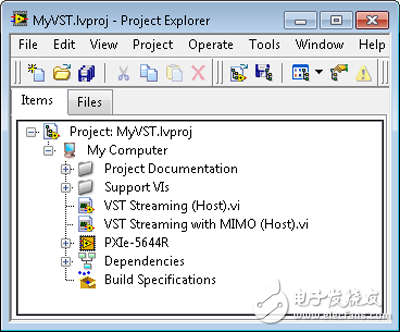

3. LabVIEW項目樣例

NI VST儀器設計庫的能力強大,但是并不能單槍匹馬地完全滿足軟件設計儀器實現默認功能的要求,也不能提供大多數VSA和VSG儀器編程人員所熟悉的簡單主機接口。

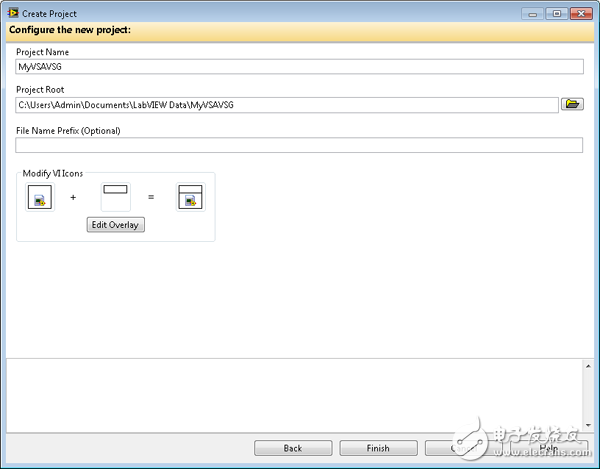

LabVIEW 2012提供了一個新功能,這種方便的機制不僅能夠分配附加代碼,從而提供默認、預編譯的功能和一個方便的主機接口,而且還使用戶能夠輕松地掌握這些代碼。此機制是LabVIEW項目樣例,將LabVIEW項目、具體VI,以及相關文件復制到用戶指定的硬盤位置。另外還提供文件重命名和更新VI標題的能力。

?

圖 4.利用LabVIEW 2012項目樣例,軟件設計儀器的用戶可以完全掌握代碼的相關部分

欲了解創建NI VST項目樣例的詳細信息,請訪問ni.com/vst/getting-started/zhs/。

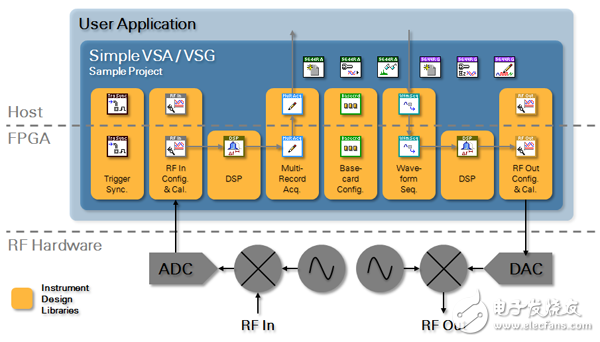

NI PXIe-5644R的軟件安裝程序能夠創建具有不同特征的多個項目樣例。最類似于默認VSA和VSG功能的項目是Simple VSA/VSG項目樣例。此項目樣例提供了與其他VSA和VSG API相似的主機接口。Simple VSA/VSG項目樣例的高層架構和數據流如圖5所示。

?

圖 5. Simple VSA/VSG項目樣例在主機和FPGA上聚集儀器設計庫,提供了一個VSA和VSG用戶所熟悉的起點

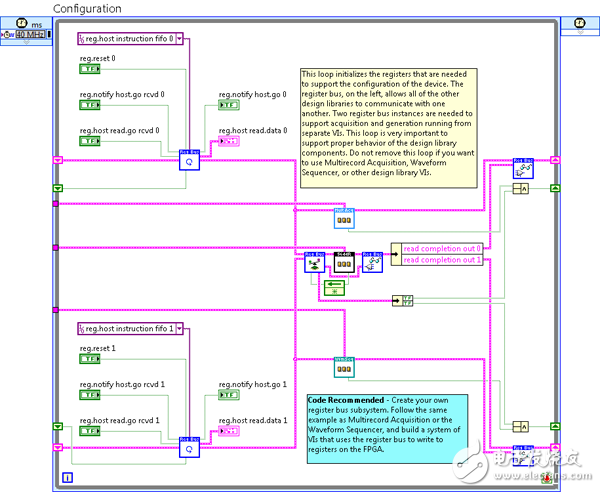

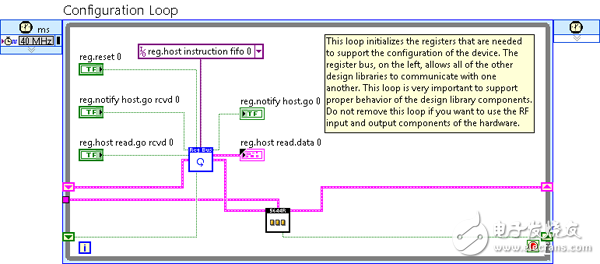

從Simple VSA/VSG項目樣例的FPGA VI開始,有四個主要回路,一些附加功能位于過程subVI內。為配置NI VST的所有可編程組件,以及FPGA上的一些儀器設計庫,配置回路從主機處接收寄存器和設置,然后將其分布至各個FPGA子系統和外部電路。為了提高性能以及使主機上的多個過程均能夠獨立訪問,有兩個寄存器總線。一個用于采集,另一個用于生成,并且每一個都必須能夠配置共享資源,例如計時。

?

圖 6. 配置回路負責接收主機的數據以及對儀器進行編程

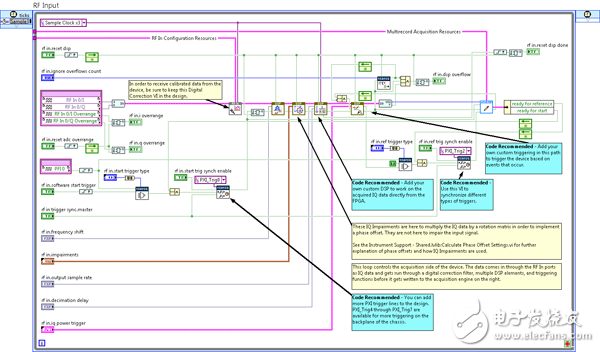

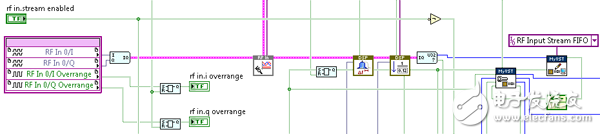

RF輸入回路獲取模數轉換器(ADC)的數據;進行復矢量校準;并進行頻移、相位校準、減損,以及可變、部分、防混疊抽選。另外,RF輸入回路還實現了同步以及數字式功率水平觸發,然后將數據寫入FIFO,并最終寫入DRAM。

?

圖 7. RF輸入回路以可配置I/Q速率生成已校準數據,并將其寫入DRAM

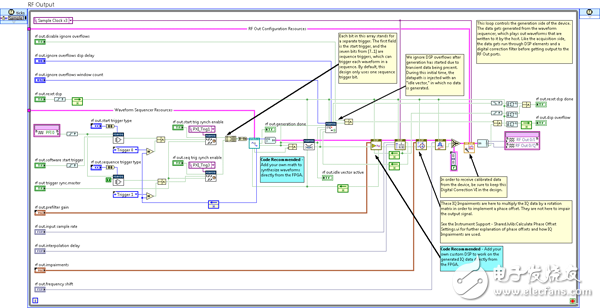

RF輸出循環類似于RF輸入循環,但是操作順序相反。來自DRAM的數據進行內插、定標、頻移、相位校準、內插、校準,然后通過數模轉換器(DAC)生成。另外還有觸發和同步所用信號。

?

圖 8. RF輸出循環檢索來自DRAM的數據然后生成數據

過程子VI包含有循環和狀態機,實現了多數據記錄采集和DRAM控制器對波形的排序。這些子VI包含了大量代碼,滿足了大帶寬和低滯后性能要求,確保這些子VI能夠在全速率ADC數據轉換下溢出,以及產生全速率DAC數據而不發生下溢,同時仍然與主機之間進行波形數據傳輸。

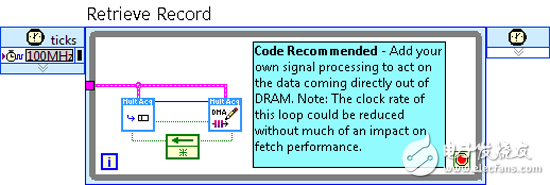

讀取循環實現的功能可以存在于多記錄采集過程之內,然而為了方便起見而將其顯示出來。該循環可以再數據離開DRAM時并在被發送到主機前進行數據處理。此路徑在它自己的回路之內,從而那些并不符合120 MHz RF輸入和輸出回路的定時要求的IP仍然可以使用。為了適應這種IP,稍微降低此回路速率并不會影響讀取性能,然而如果降得過多,則只會增加數據到達主機所需時間。這樣即使采樣內存被填滿了,也不會丟失樣點或破壞數據。

?

圖 9.讀取循環提供了在已采集數據返回主機之前對其進行處理的機會。在默認情況下,讀取回路返回原始數據

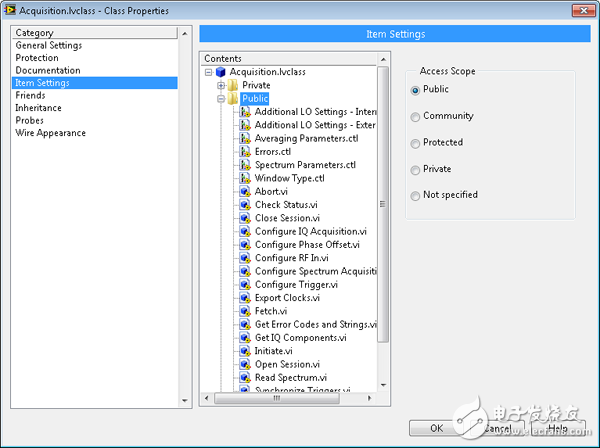

雖然頂層FPGA VI集合了13個儀器設計庫的功能,然而在主機上對所有這些庫進行獨立編程仍然不方便,并且此應用層主機代碼一點也不像傳統的VSA或者VSG API。為了解決此問題,Simple VSA/VSG項目樣例包含了一個附加主機層,將這些儀器設計庫集合在一個接口內,提供了與供應商定義的VSA/VSG API相類似的功能。LabVIEW類為此提供了一個方便的機制,即提供一個嚴格類型的會話,公有和私有方法,以及一個方便的子VI圖標頭文件保持機制。請注意,LabVIEW類中面向對象的繼承,并沒有用于此主機接口。

?

圖 10.LabVIEW類提供了一個方便的功能集合和主機接口保持機制

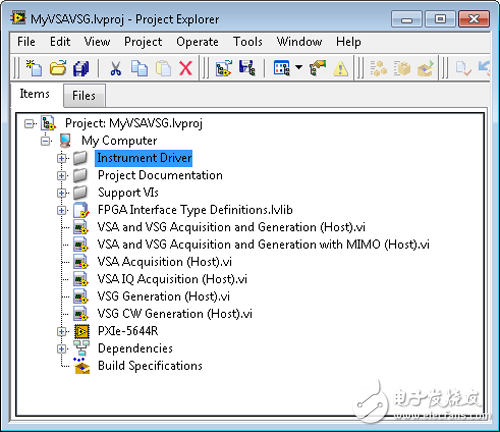

這個簡單的 VSA/VSG樣例項目還提供了常見的RF VSA和VSG操作所用的若干個主機樣例,這些樣例說明了如何正確使用主機接口。這些樣例涵蓋頻域和I/Q采集;CW和基于序列的波形發生;以及多輸入多輸出(MIMO)同步。

?

圖 11.一些主機樣例說明了Simple VSA/VSG項目樣例使用基于類的主機接口的方法

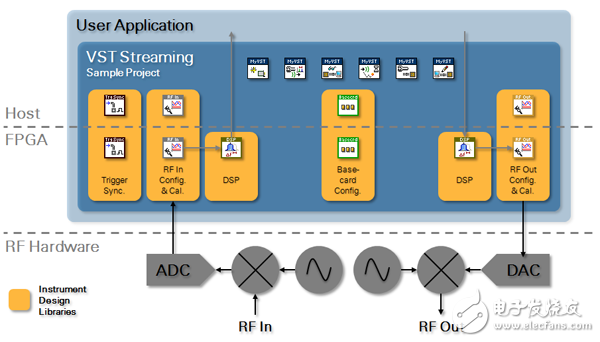

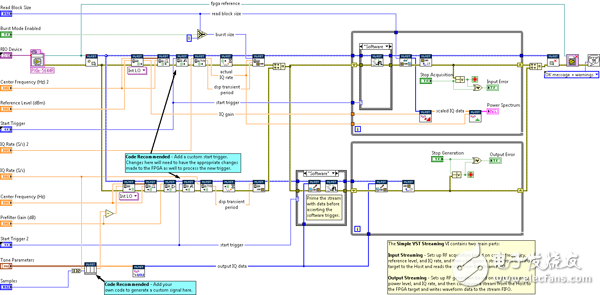

簡單 VSA/VSG項目樣例包含極多功能,并提供了熟悉的主機接口。然而該實用工具的代價就是代碼的復雜度。具體地說,FPGA上的DRAM采用基于波形的抽取,顯著增加代碼量、復雜度,以及VST FPGA資源占用。然而,并不是所有應用均需要基于波形或者儀器數據移動范式。一些應用更加適合實時流數據移動架構。對于這些應用,VST Streaming項目范例是一個更好的起點,自定義的自由度更廣。

?

圖 12.VST Streaming項目樣例在主機和FPGA上集合了儀器設計庫,提供了一個靈活地開發實時、低滯后信號處理和嵌入式應用的起

VST Streaming項目樣例的頂層FPGA VI的架構與簡單 VSA/VSG項目樣例相近。然而如果仔細考察,會發現要簡單得多。可以明顯看出,VST Streaming沒有代碼量極多的配置過程。配置循環也簡單得多,只有一條寄存器總線而非兩條,并且所有子系統均包在一個子VI中。

?

圖 13.VST Streaming項目樣例中的FPGA VI配置回路,只有一個寄存器總線接口,比Simple VSA / VSG要簡單得多

VST Streaming項目樣例沒有獨立的采集和發生循環,而是所有模擬I/O均采用一個循環。對于要求RF輸入輸出之間的相位關系已知的應用,由于ADC和DAC使用相同的采樣時鐘,此架構提供了兩者之間的確定性同步。DSP和VST Streaming項目樣例的校準類似于VSA / VSG。

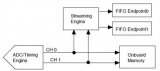

兩個項目樣例FPGA VI之間的主要區別是:VST Streaming項目樣例使用輕質機制完成與主機之間的數據收發。它采用簡單的流控制器,支持基本觸發、連續和間斷流,以及溢出和下溢檢測。這些控制器中斷信號源與目的地之間的2線握手信號,有效地選通數據流。控制器不支持全4線握手方案,該方案能夠調整上游節點或者被下游節點所調整;因此,系統特性化以及確保這些流控制器控制的所有FIFO均能夠以要求的速率產生或消耗數據就落到了程序員的肩上。在VST Streaming項目樣例中通過簡單的更改默認情況下完成與主機之間的數據收發的FIFO,可以支持數據流傳輸到VST FPGA上的其他位置以進行進一步處理,或者通過PXI Express背板,利用P2P傳輸至其他模塊。

?

圖 14.FPGA流控制器和FIFO封裝實現基本流控制,并且能夠輕松改變數據流的源及目的地路線

現在來看VST Streaming項目樣例的主機端,雖然機制與Simple VSA/VSG不同,也存在類似于儀器設計庫主機組件的集成,。VST Streaming項目樣例不使用LabVIEW類,而是將功能簡單地集成到子VI中,并將會話傳遞至子VI之間的寄存器總線。此寄存器總線會話還包含有FPGA VI 引用,因此所有這些子VI不僅能夠訪問寄存器總線通信策略,而且還可以訪問NI-RIO FIFO和控制器。另外,不存在獨立的數據采集和生成會話;所有VI均使用同一會話。

?

圖 15.VST Streaming項目樣例主機接口具有一個基于寄存器總線的會話線,用于采集和生成subVI。在邏輯上,此樣例將采集和生成分組成為獨立的行,以方便閱讀

VST Streaming項目樣例提供兩個主機樣例。較簡單的一個樣例把從VST處采集得到的增多的或者連續的波形數據傳輸至VST進行生成,。比較高級的樣例說明了多個VST的MIMO同步。

?

圖 16.這些樣例說明了VST Streaming項目樣例的主機接口

4. 儀器驅動FPGA擴展

儀器驅動FPGA擴展提供了一種兼容NI-RFSA和NI-RFSG儀器驅動的VST FPGA編程方法。FPGA上的抽取層實現了所需要的儀器驅動功能,同時提供接口以改善具體應用的FPGA。雖然不像儀器設計庫的直接編程那樣靈活,然而儀器驅動FPGA擴展支持的修改類型與標準信號分析儀和信號發生器的基于記錄的采集和生成模式相一致。

?

圖 17. 儀器驅動FPGA擴展架構包含VST儀器設計庫,并且增加了一個抽取層以保護組件。用戶IP不在此代碼中,由主機進行控制,并且不受預編譯封閉源NI-RFSA和NI-RFSG的影響

欲了解儀器驅動FPGA擴展的更多信息,請閱讀?儀器驅動的FPGA擴展介紹。

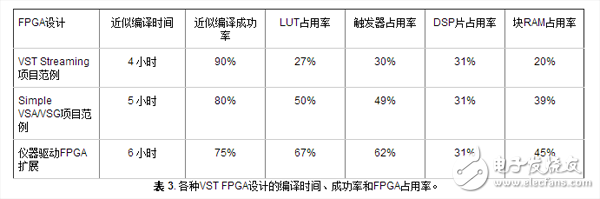

5. 大型FPGA開發考慮事項

The Virtex-6 LX195T FPGA on the NI PXIe-5644R and the NI PXIe-5645R is a large FPGA, though the full suite of instrument design libraries consumes a considerable fraction of the available resources. As such, compilation times can take 5 hours or more when using the NI LabVIEW FPGA Compile Cloud Service, depending on the complexity and resource utilization of the FPGA design. Furthermore, FPGA compilation is a non-deterministic process, and as a design consumes more FPGA resources, the repeatable compilation success rate drops below 100%. For such designs, initiating multiple compiles in parallel can help to ensure a successful compilation in approximately the same time as a single compilation. Table 3. provides some estimates for the different FPGA designs discussed in this paper.

電子發燒友App

電子發燒友App

評論