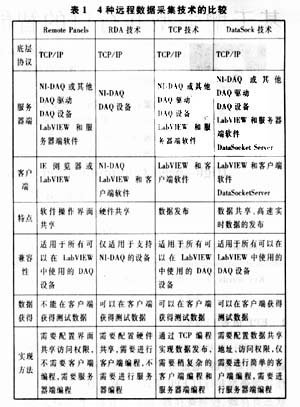

多功能智能DAQ設備配有自定義式板載處理功能,最大限度地為系統定時及觸發提供靈活性能。 與控制設備功能的固定ASIC不同,智能DAQ采用基于FPGA的系統定時控制器,令所有模擬和數字I/O能夠根據特定應用操作接受相應的配置。 本指南展示了:如何使用R系列智能DAQ板卡和NI LabVIEW FPGA,靈活自如地執行數據采集任務。

1. 入門

NI LabVIEW FPGA模塊幫助DAQ系統的開發者靈活自如地進行應用程序編程以實現各類輸入/輸出操作。 用戶無需預先了解VHDL等硬件設計工具,便可將LabVIEW代碼嵌入FPGA芯片并獲得硬件定時的速度和可靠性。

讓我們先從數據采集硬件的常用組件切入論題。 假設您擁有了模數轉換器(ADC)、數模轉換器(DAC)和數字輸入/輸出線,則所有I/O便要根據實際操作接受某種方式的定時和控制。 典型的多功能數據采集設備采用功能齊全的ASIC,滿足了大多數的功能性需求。 比如:M系列DAQ設備通過DAQ-STC2,控制著各類硬件組件的定時和觸發。 智能DAQ硬件(如:R系列DAQ設備)區別于市面上的其他任何數據采集設備,因為在控制設備功能方面智能DAQ用基于FPGA的系統定時控制器取代了傳統ASIC,從而使得所有模擬和數字I/O都能根據特定應用操作接受相應的配置。 可重配置FPGA芯片通過NI LabVIEW FPGA模塊進行編程,此時NI LabVIEW的數據流模式仍舊適用,不過采用了一組新函數控制最底層的設備I/O。 LabVIEW FPGA I/O節點并不通過NI-DAQmx函數負責實現常見的任務和功能,而是靈活自如地在各個通道最底層上運行。 通過以下各部分的內容,我們將了解NI-DAQmx的特定實例,并學習如何通過智能DAQ定制各類數據采集任務。

2. 定時和觸發

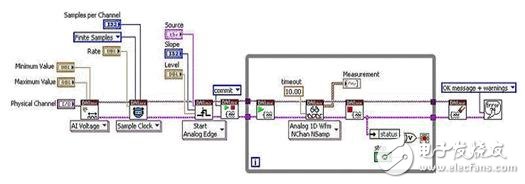

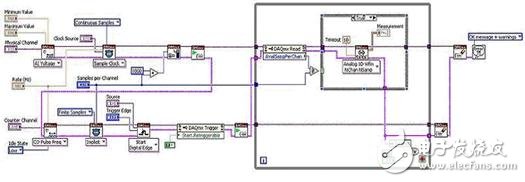

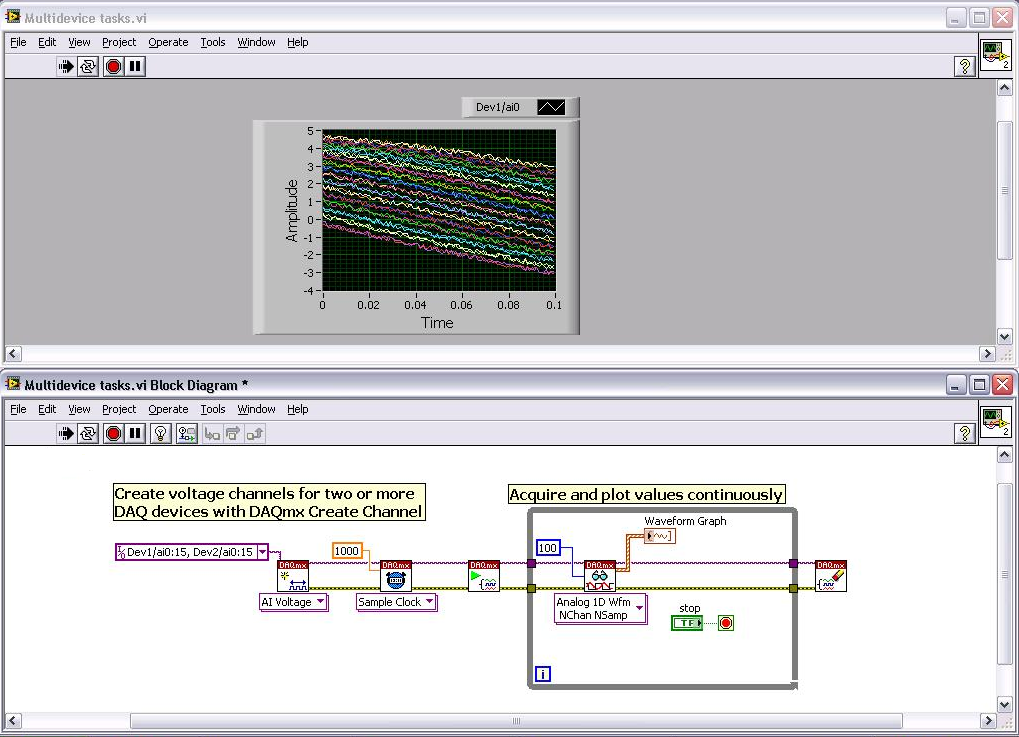

實現高級數據采集的智能DAQ主要用于定制定時和觸發。 下方的范例程序框圖展現了:NI-DAQmx幫助實現的觸發式模擬輸入任務。

?

?

圖1. 通過NI-DAQmx實現的觸發式模擬輸入

如圖1所示,智能DAQ并未使用不同函數配置通道,而是通過名為I/O節點的函數讀寫各路模擬和數字通道。 讓我們看看使用NI LabVIEW FPGA中I/O節點所獲得的相同功能。

?

?

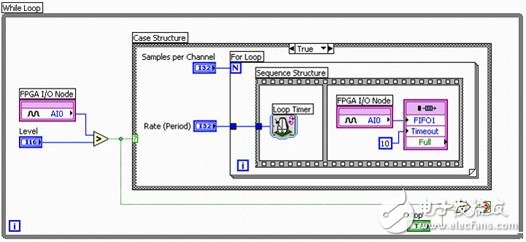

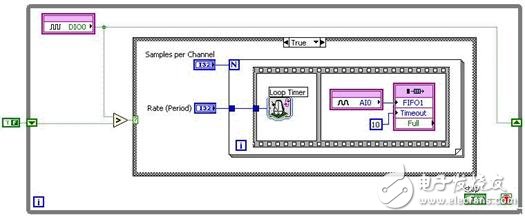

圖2. 通過智能DAQ和NI LabVIEW FPGA實現的觸發式模擬輸入

上圖既沒有針對全局通道、采樣時鐘、觸發的配置函數,也沒有開始、停止和清除等任務。 所有內容都被1個簡單的模擬I/O讀取所取代;全部定時都為本地LabVIEW結構(如:While循環和條件結構)所控制。由于整個程序框圖均在FPGA硬件內執行,LabVIEW代碼的運行便體現出硬件定時的速度和可靠性。 讓我們更深入地了解一下該程序框圖的運行方式。 模擬I/O節點并不指定某個采樣速率,而使用For循環采集各個樣本。 與之對應的ADC在I/O節點被調用時,負責對輸入信號進行實際數字化,因而通過For循環接受定時。 若想在100 kHz的頻率下進行信號采樣,針對循環的延遲就必須設定為10 μs。 循環的定時器函數從第2輪循環迭代開始便確保著特定的時間延遲,用戶因而能夠通過順序結構保證樣本之間存在著指定的時間間隔。 NI LabVIEW FPGA中功能強大的條件結構,實際代表了用于封裝各類代碼的硬件觸發。 由于所有的函數和結構都通過邏輯單元在硬件內運行,所以條件結構確保開始具有實時10 μs時間精度的采樣。 最后需指出的是,由于操作位于硬件層,只涉及幾個層次的抽象處理,因此用戶無需清除任務ID或釋放內存。

就基于FPGA的智能DAQ硬件而言,其真正的優勢是能夠定制各類定時和觸發,并在硬件中進行信號處理和決策。 現在讓我們了解一下:針對某類自定義應用,需對模擬輸入觸發做出哪些修改。 若我們希望在2路模擬輸入通道的某路電壓超過指定范圍時便觸發采集,又該如何修改呢? 借助NI LabVIEW FPGA,此類任務的執行易如反掌。

?

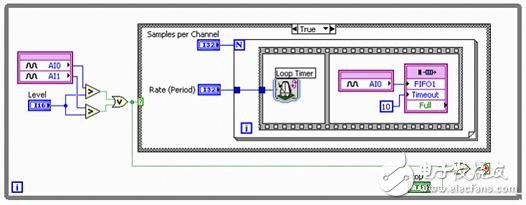

圖 3. 通過智能DAQ和NI LabVIEW FPGA實現的自定義觸發式模擬輸入

這里,我們已經為程序框圖添加了第2個I/O節點和第2個比較函數,以及1個布爾“或”函數。 智能DAQ硬件為所有的模擬輸入通道提供專用ADC,因而2路通道能夠接受同步采樣;同時,只要任何1路通道的電壓超過了指定范圍,條件結構便會執行“真”條件,并開始以10 μs時間精度進行采樣。 請記住:缺少智能DAQ便不可能生成類似的觸發;在其他DAQ硬件上應用時,觸發需要具有更高延遲的軟件定時來實現。 如果此后我們希望通過擴展將監控范圍從2路通道延伸至全部8路通道,甚至希望添加數字觸發,就需要簡化自定義代碼。 添加預觸發掃描后,用戶便可對輸入通道不斷進行采樣并將數據傳送至FIFO緩沖器。 觸發器一旦接受讀取,FIFO緩沖器和此后的采樣便可經由DMA通道,被傳送至主機。

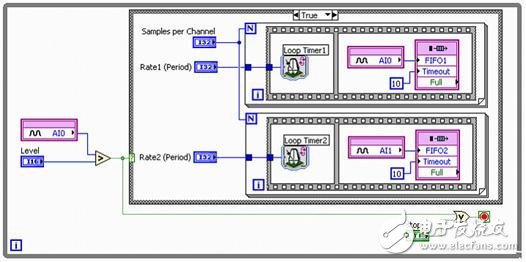

如果我們希望借助NI-DAQmx驅動,對第2模擬輸入通道進行采樣,則該程序框圖與圖1所示的內容相差無幾。然而限制依然存在,因為2路通道均被迫引用相同的觸發器并以相同的時鐘頻率進行采樣。 現在我們來看看:智能DAQ和NI LabVIEW FPGA幫助實現的各類多通道采樣。

?

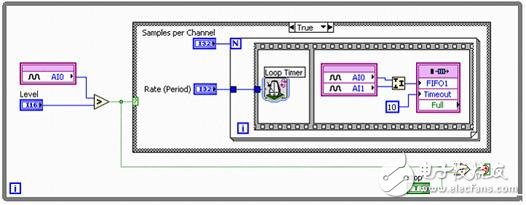

圖4. 通過智能DAQ實現的觸發式同步模擬輸入

圖4(上圖)展現了:如何基于模擬輸入通道0中的模擬觸發器,對2路不同的模擬輸入通道進行同步采樣。由于智能DAQ設備均配有獨立的ADC,在同一I/O節點中的2路通道可在完全相同的時刻接受采樣。 典型的多功能DAQ設備可通過一個ADC多路復用所有通道,因此,各路通道必須共享相同的采樣時鐘和觸發線。 圖5(下圖)展現了:智能DAQ硬件其實能夠以獨立的速率,對不同的模擬輸入通道進行采樣。 在獨立回路中放置模擬輸入I/O節點后,每路通道會以完全不同的速率進行采樣,然后各自通過2條DMA通道讀寫硬盤。

?

圖5. 通過智能DAQ實現的觸發式多速率模擬輸入

最后需指出的是,我們若是希望2路通道具有相互獨立的采樣率和開始觸發,則可參照圖6,將所有I/O節點都部署在并行循環結構中。該方式充分利用了FPGA的并行性,確保了各項任務能夠使用專用資源并在執行時完全獨立于其他采集任務。

?

圖6. 通過智能DAQ實現的獨立觸發式多速率模擬輸入

3. 同步

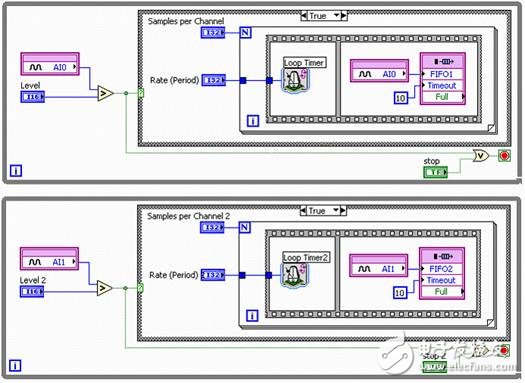

DAQmx驅動程序提供多種同步選擇,幫助建立輸入和輸出的時間相關性。 在下方的程序框圖中,模擬輸入通道和模擬輸出通道借助數字觸發實現同步;過程中,需對模擬輸入指定數字觸發,并使用模擬輸入的觸發器信號觸發產生模擬輸出。

?

?

圖7. 通過NI-DAQmx實現的同步模擬輸入和輸出

用戶可通過智能DAQ硬件輕而易舉地執行同步任務,而無需借助任務ID和板載信號路由。 本處即顯示了NI LabVIEW FPGA中的內容。

?

?

圖8. 通過智能DAQ實現的同步模擬輸入和輸出

此處,我們再次通過條件結構在FPGA芯片上執行硬件觸發,而數字通道0上的上升沿則啟用了真條件中的代碼。 在順序結構中,模擬輸入與輸出的節點在同時接受調用的過程中,幾乎沒有任何抖動;而我們只要簡單地在各個獨立的While循環內嵌入模擬I/O節點,即可令其擁有獨立的采樣速率。 另外值得注意的是: 程序框圖中顯示的正弦發生器函數是1個Express VI,可幫助用戶在查找表(LUT)中交互式地配置正弦值。

圖8中的智能DAQ程序框圖與圖7中的DAQmx VI皆具有相同的功能,而唯有智能DAQ才能為自定義任務提供相應的靈活性。 舉例為證:如需添加1個暫停觸發,我們只消在內部While循環中添加1個條件結構,并通過另一個數字I/O節點選擇真條件或假條件,即可輕松完成任務。 對硬件進行編程的強大功能,實現了各類I/O的定時與同步。

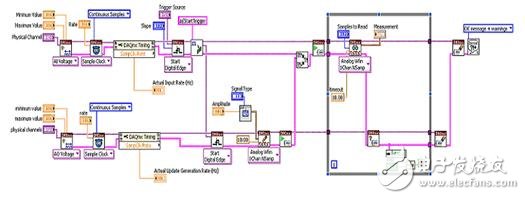

多功能同步的另一例證體現為:通過板載計數器產生有限脈沖并將計數器輸出用作模擬輸入的采樣時鐘。 該過程是進行可重觸發式有限采樣的常用手段。 下圖顯示了開展此類采集所必需的DAQmx代碼。

?

?

圖9. 通過NI-DAQmx實現的可重觸發式有限模擬輸入

現在,讓我們對下圖內容和呈現相同功能的NI LabVIEW FPGA程序框圖,加以比較。

?

?

圖10. 通過智能DAQ和NI LabVIEW FPGA實現的可重觸發式有限模擬輸入

由于NI LabVIEW代碼在硬件層運行,圖10中的驅動配置步驟顯然得到了極大精減。 我們已經借助簡單的數字輸入線和For循環結構,創建了硬件可重觸發式有限采集。 圖9中的程序框圖使用2個板載計數器,創建出可重觸發的有限脈沖序列;典型的多功能DAQ設備只有2個計數器。 而借助NI LabVIEW FPGA,智能DAQ硬件卻能夠將任意一條數字線配置成計數器。 我們將在之后的段落里,涉及更多“通過智能DAQ運行計數器/定時器”的內容。

我們能夠借助由頻率觸發的采集,進一步地推進智能DAQ在硬件定時方面的靈活性特性。 用戶可通過高速板載決策計算輸入信號的頻率,而后選擇條件結構中所需的代碼;這一點是使用典型多功能DAQ設備所無法企及的。 在多設備的同步進程中,智能DAQ還可提供用于PCI板卡的RTSI總線或是用于PXI模塊的PXI觸發總線。 這些外部定時和同步線還可通過程序框圖上的I/O節點接受訪問。

4. 模擬波形的生成

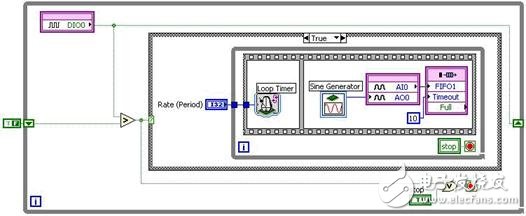

不少多功能DAQ設備都配有模擬輸出通道,能夠為了生成連續的模擬波形而需要用到FIFO緩沖。 生成的波形可將FIFO用作循環緩沖區,且無需從主機處接受任何更新數據,即可連續不斷地重新生成一系列的模擬值。 通信總線的有無對此影響不大,因為并沒有針對設備的頻繁數據讀寫。 而如果波形需要修改,就必須重新啟動輸出任務并向FIFO寫入新數據。 另一個辦法是向硬件FIFO設備連續讀寫數據,而這又會導致輸出任務出現時滯。 借助智能DAQ,用戶能夠將波形輸出結果存儲于硬件,甚至能夠通過硬件觸發改變波形,進而創建任意波形發生器。

下方的函數發生器范例通過數字輸入線,觸發了輸出波形中的改動。 通過組合數字I/O線0與1,我們取得了應用于模擬輸出的4種不同狀態或稱條件。

?

?

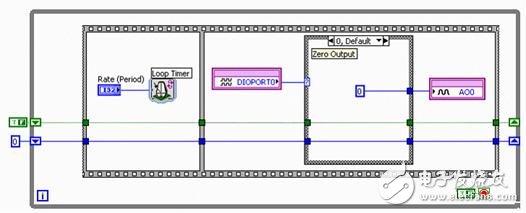

圖11a. 配有智能DAQ條件0的函數發生器 – 零輸出

?

?

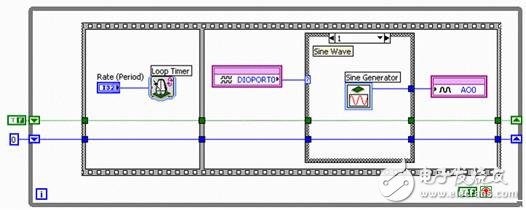

圖11b. 配有智能DAQ條件1的函數發生器 – 正弦波

當兩線皆呈現低電平時,執行條件0;如圖11a所示,輸出值為0 V常量。而當DIO線0呈現高電平而DIO線1呈現低電平時,條件1將在模擬輸出0上執行并生成一個正弦波。用戶可通過該正弦生成結構(圖11b)中的正弦發生器Express VI,配置NI LabVIEW FPGA必需的參數,交互地配置正弦波。

?

?

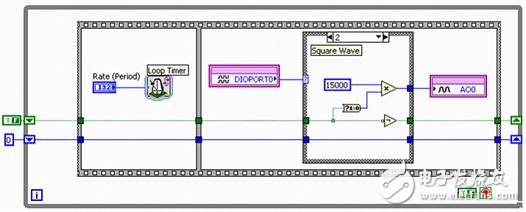

圖11c. 配有智能DAQ條件2的函數發生器 – 方波

條件2(圖11c)能夠在While循環的每輪迭代中,輕松切換布爾值。 數值較低時,整數15000便被寫入模擬輸出AO0,以對應16位DAC內由輸出寄存器存放的數值:15000。 16位有符號整數可以包含-32768到32767之間的數值。當輸出電壓范圍介于-10 V和10 V時,向模擬輸出AO0寫入-32768會生成-10 V電壓,而寫入32767則生成10 V電壓。該例中,因我們的寫入值為15000,則生成的電壓將低于5 V。(數學公式為: 15000/32767 * 10 V = 4.5778 V) 通常,條件2會輸出一個在0 V和4.578 V之間變換的方波。

?

?

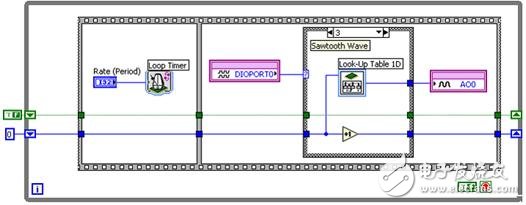

圖11d. 配有智能DAQ條件3的函數發生器 – 鋸齒波

當DIO 0和DIO 1均呈現高電平時,便執行最后一個條件(圖11d);其間,須借助查找表(LUT)連續生成一個鋸齒波。 作為另一類Express VI的查表VI,既能存儲任意波形值,也能通過編程建立波形值的索引。 該例中,接受配置的鋸齒波可在模擬輸出通道0上生成。

通過將所有的值都存儲在FPGA上,用戶在降低總線依賴性的同時,也確保了波形更新時硬件定時的速度和可靠性。 之前各部分中所描述的模擬輸入的觸發和同步靈活性同樣適用于模擬輸出;借助智能DAQ,用戶能夠以不同速率,完全獨立地更新各路模擬輸出通道。 這意味著:用戶可在不影響其他通道輸出結果的前提下,修改單個周期性波形的頻率。 請注意:大多數數據采集硬件均不具備此項功能。

另見:通過RIO硬件和NI LabVIEW FPGA模塊實現的任意波形發生

5. 計數器/定時器的操作

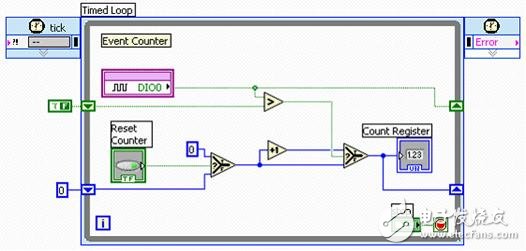

如前所述,典型的多功能DAQ設備只有2個板載計數器,而智能DAQ則能在各條數字線上運行計數器功能。 數字I/O節點能夠在NI LabVIEW FPGA中利用名為單周期定時循環的專業結構,幫助用戶在2.5 MHz至200 MHz的特定頻率范圍內執行代碼。 例如,借助40 MHz的時鐘,用戶可使用單周期定時循環,在各條數字線上創建40 MHz計數器。 圖12(下圖)展現了程序框圖的樣式。

?

?

圖12. 配有智能DAQ的簡單事件計數器

由于計算值基于U32(32位整數)的數據類型被發送至顯示控件,該代碼便在FPGA芯片上生成了1個40 MHz的32位計數器。 用戶可對其進行數次復制與粘貼,令不同數字線上的多個計數器都能夠彼此完全并行地運行。 通過對智能DAQ中參數的設置可以實現定時器操作的自定義。 通過選擇,用戶能夠每隔2個上升沿便進行1次計數器遞增,甚至能基于計數寄存器的值觸發模擬采集。 許多復雜的計數器操作(如:有限脈沖序列生成和級聯式事件計數)均需要使用2個計數器,這意味著使用典型多功能設備中的所有板載計數器。 在總共160條數字線的幫助下,智能DAQ硬件上定時器的最大數量很少受到I/O可用性的影響,而往往取決于FPGA芯片的大小。 由于NI LabVIEW代碼運行于硅芯片中,因而用戶無需“裝備”或“重新裝備”通用計數器,即能全面控制計數器的運行。

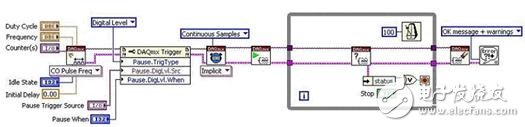

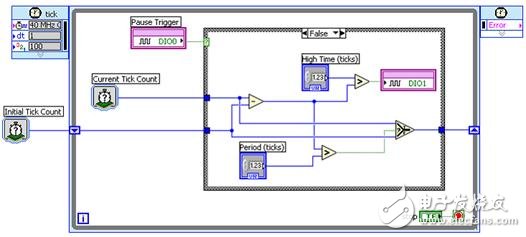

圖13(下圖)中的范例使用計數器,生成了一個連續脈沖序列并將暫停觸發器置于NI-DAQmx中。

?

?

圖13. 連續脈沖序列的生成和配有NI-DAQmx的暫停觸發器

在NI LabVIEW FPGA中,暫停觸發器無需接受配置,因為只需簡單的條件結構便能在硅芯片中實現相同的功能。 此處是通過智能DAQ運行時所展現的相同功能(圖14)。

?

?

圖14. 連續脈沖序列的生成和配有智能DAQ的暫停觸發器

在這種情況下,數字I/O線DIO0用作暫停觸發,而脈沖將在數字I/O線DIO1上生成并輸出。使用單周期定時循環可令各個脈沖獲得25 ns的分辨率,因為這將成為單個計時在使用40 MHz定時源時的值。

另見:通過NI LabVIEW FPGA模塊實現的PWM輸出

6. 數字I/O應用

智能DAQ硬件提供多達160條硬件定時數字線,令諸多數字應用成為可能。 我們已經學習了如何使用數字I/O實現觸發、同步及計數器/定時器的運行,而智能DAQ還可用于誤碼率測試、數字模式匹配、脈沖寬度調制、正交編碼器和數字通信協議。 自定義或標準形式的串行接口均能直接通過數字定時框圖編程來實現。 舉例說明,SPI便是一款與硬件組件(如:微控制器或ADC)進行通信時最常用的串口協議。 圖15(下圖)展現了在進行16位SPI通信時,3條必要數字線所對應的定時框圖。

?

?

圖15. SPI通信輸入定時框圖

如定時框圖所示,所有16位數據均在每個時鐘周期上順次傳遞,而片選控制線(chip select line)則呈現低電平。 現在,我們來看看在NI LabVIEW FPGA中,如何通過智能DAQ硬件上的3條數字線進行此類編程。

?

?

圖16. 16位SPI通信程序框圖

圖16中,外部While循環確保了所有代碼均能連續執行,而寫入布爾輸入控件則通過條件結構啟動著數據傳遞。 順序結構中的第一框架將片選控制線(chip select line)設置為低電平,之后由中間框架寫入數據位并將時鐘線切換16次。 最終,第三順序框將片選控制線(chip select line)設置回TRUE狀態,并將數據線重置為默認的FALSE狀態。 這一簡單范例只是借助智能DAQ進行數字通信時的一項內容。 用戶若想應用數字握手,便需為ACK(備用)和REQ(暫停)線準備2路通道,其中一路通道面向并行運作的時鐘信號和數據線。

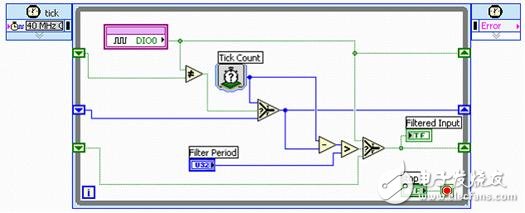

數字線會時常抖動,在使用機電接觸時更是如此,然而用戶可通過NI LabVIEW FPGA,選擇不同方式,在數字輸入線上添加去抖動濾波器。 在消除狀態的錯誤改動時,數字去抖動濾波器確保數值的變化能夠保持一段最短的時間,因而規避了因抖動引發的錯誤讀取。 圖17展現了如何通過智能DAQ實現此項功能的內容。

?

?

圖17. 智能DAQ硬件上的數字濾波器程序框圖

另見:

借助NI LabVIEW FPGA實現的SPI通信

借助NI LabVIEW FPGA實現運行的I2C

借助NI LabVIEW FPGA開發的SPDIF輸入模塊

使用NI LabVIEW FPGA模塊的RS-232模塊

7. 數據傳輸方式

配備NI-DAQmx驅動程序的傳統多功能DAQ和智能DAQ之間的最大差異在于:數據傳輸的執行方式。 NI-DAQmx驅動程序將承擔由設備至主機的各項傳輸任務,此項操作中NI LabVIWE FPGA會對基于FPGA的所有板載硬件進行編程。 用戶可通過多種途徑緩沖設備上的板載數據,并使用不同方式(如:DMA通道或中斷請求)傳輸數據。

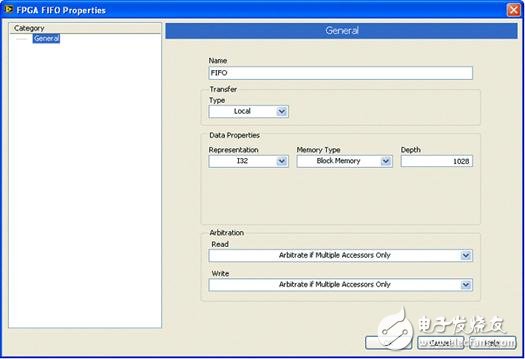

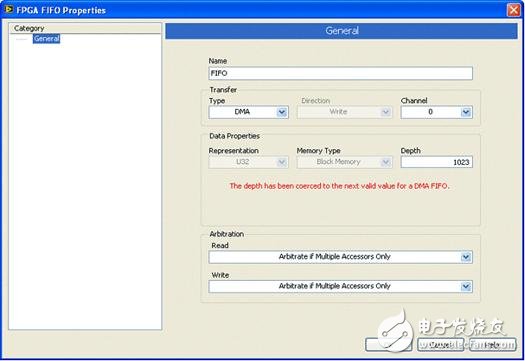

NI LabVIEW FPGA中的FIFO緩沖區在LabVIEW項目瀏覽器中接受配置,并能借助板載內存或硬件邏輯獲得運行。 圖18顯示了如何經由項目瀏覽器,在板載塊存儲器中配置整數的FIFO緩沖區。

?

?

圖18. NI LabVIEW FPGA中的FIFO配置

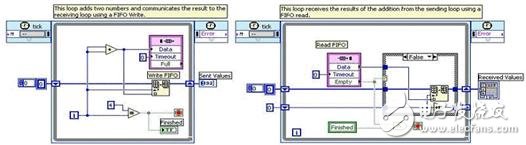

FIFO一經創建,便能用于NI LabVIEW FPGA程序框圖上多個循環之間的數據傳遞。 圖19中的范例顯示:數據先被寫入左側循環中的FIFO,并隨即從右側循環中的FIFO被讀出。

?

?

圖19. 通過FIFO和多循環實現的NI LabVIEW FPGA程序框圖

同樣通過LabVIEW FPGA FIFO獲得應用的直接存儲器訪問(DMA)通道,在項目瀏覽器中接受了類似的配置。

?

?

圖20. NI LabVIEW FPGA中的DMA FIFO配置

?

?

圖21. 通過DMA FIFO和位組裝實現的NI LabVIEW FPGA程序框圖

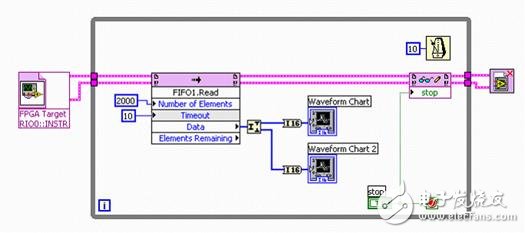

所有的DMA FIFO數據傳輸寬度均為32位;因此,當其傳遞源自16位模擬輸入通道的數據時,往往能夠合并2路通道或2個樣本上的數據再進行傳輸,從而提高帶寬使用率。 這即是圖21所展現的位組裝。當數據被直接傳遞到主控計算機的內存后,便可通過在Windows環境下運行的NI LabVIEW主接口函數接受讀取(圖22)。

?

?

圖22. 通過DMA FIFO讀取和位拆裝實現的主接口代碼

如圖22所示,主接口程序框圖引用FPGA終端VI,然后使用While循環連續讀取DMA FIFO。 32位的數據被分解為2路16位通道,在波形圖表上接受采樣和繪制。 主接口VI還能對FPGA VI前面板上的各類顯示控件和輸入控件進行讀寫操作;在這種情況下,“停止按鈕”輸入控件也被寫入。

另見:使用DMA FIFO, 為可重復配置式I/O設備開發高速數據采集應用程序

8. 結論

盡管DAQ-STC2等固定ASIC能夠滿足數據采集的大多數需求,然而,唯有借助智能DAQ中基于可重新配置FPGA的I/O定時和控制,方能實現高度靈活性和完全定制。 借助NI LabVIEW FPGA,觸發和同步任務獲得了簡化,因為通過繪制圖形化程序框圖即可充分滿足用戶需求;借助獨立的模擬和數字I/O線,智能DAQ可利用FPGA提供的實際并行。 R系列智能DAQ設備已經針對多速率采樣、自定義計數器操作和頻率高達40 MHz的板載決策,為多功能數據采集進行了各項可能的修繕。

電子發燒友App

電子發燒友App

評論