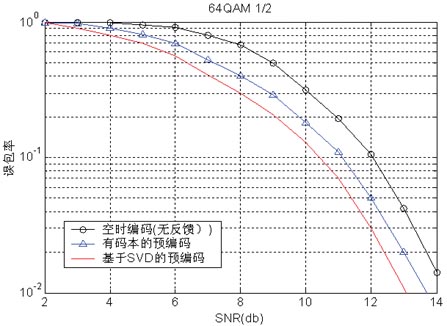

引言

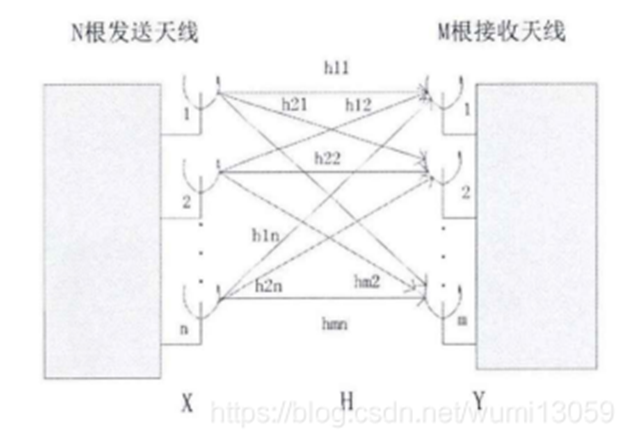

隨著物聯網的興起和移動互聯網業務種類的日漸豐富,人們對蜂窩移動通信數據傳輸速率以及服務質量提出了更高的要求。由于能夠充分挖掘空間維的自由度,在提高頻譜效率的同時獲得較好的功率利用率,大規模MIMO系統引起了國內外的廣泛關注,并成為下一代無線通信系統最有潛力的無線傳輸技術之一。大規模MIMO系統配置的大規模天線陣列在帶來性能增益的同時也帶來了前所未有的挑戰,如大規模天線陣列系統下傳輸方案的設計、急劇增加的系統硬件復雜度和計算復雜度等,如何實現大規模MIMO的原型驗證系統也是一個非常具有挑戰性的問題。

本文首先對基于NI平臺的大規模MIMO應用程序框架進行簡單介紹,接著本文將重點闡述采用NI的硬件平臺成功搭建的Mini Massive MIMO原型驗證系統,包括系統的整體架構,系統時鐘和觸發信號的產生和分配,上下行鏈路的數據處理流程,以及系統的實際測試結果,最后本文將對全文進行總結。

一、基于NI平臺的大規模MIMO應用程序框架

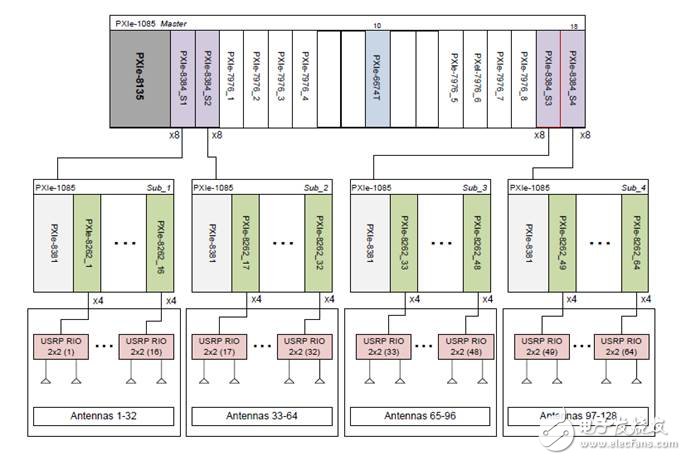

基于NI平臺的大規模MIMO應用程序框架將軟件無線電(Software Defined Radio,SDR)節點(主要為USRP-RIO系列)、時鐘分配模塊、高數據吞吐量PXI系統以及LabVIEW相結合,提供了一個具有魯棒性和確定性的研發所使用的原型設計平臺,圖1給出了一個最多可支持128根天線的大規模MIMO原型設計平臺的示意框圖。

?

圖1 NI 基于PXI和USRP RIO的可擴展大規模MIMO系統框圖

從圖中可以看出,整個系統的框架由PXIe-1085機箱搭建而成,采用層次化設計,數據由USRP-RIO采集后經PXIe-8262接口匯聚到各個子PXIe-1085機箱,每個子PXIe-1085機箱最多可連接16個USRP-RIO即構成32×32的MIMO,各個子PXIe-1085機箱再通過PXIe-8384和PXIe-8381匯聚到主PXIe-1085機箱,主PXIe-1085機箱上除配置PXIe-8135高性能嵌入式控制器外,還搭載了PXIe-7976的FPGA協處理器以用于提高數據的處理能力。

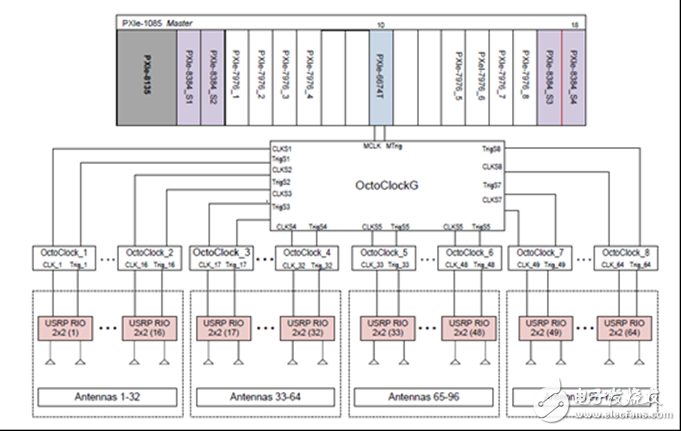

定時和同步對于任何一個需要部署大量無線電設備的系統來說都是至關重要的,對于大規模MIMO系統來說也是如此,圖2展示了NI 基于PXI和USRP RIO的可擴展大規模MIMO系統的時鐘連接框圖。圖中所用到的OctoClock模塊為時鐘模塊,該模塊既可使用內部集成的GPS鎖定晶體振蕩器(GPSDO)作為時鐘源,也可采用外部的10MHz參考時鐘和每秒脈沖數(PPS)信號作為時鐘源和觸發信號源。輸入的時鐘信號和觸發信號可分別經由OctoClock模塊放大和分發為8路信號,從而可同時提供給8個OctoClock模塊或8臺USRP設備在時鐘和觸發信號上的同步。

?

圖2 系統時鐘連接圖

基于NI平臺的可擴展大規模MIMO系統的系統級同步原理可大致總結如下,PXIe-6674T定時和同步模塊具有一個恒溫晶體振蕩器(OCXO),位于主機箱的第10槽,可生成一個非常穩定且精確的10MHz參考時鐘(50 ppb的精確度)和提供一個數字觸發信號給OctoClock-G時鐘分配模塊以用于時鐘和觸發信號的分發。之后,OctoClock-G放大并分發這一10MHz參考時鐘信號(MCLK)和觸發信號(MTrig)至8個OctoClock模塊,接著每個OctoClock模塊再以一對八的比例提供給USRP RIO設備,從而確保64個USRP RIO設備的所有天線共享10MHz的參考時鐘和主觸發信號。這樣通過PXIe-6674T定時和同步模塊和OctoClock時鐘分配模塊整個系統中的所有PXI機箱和無線電設備都共享一個通用10MHz參考時鐘和一個數字觸發信號,從而確保了整個系統的系統級同步,各個無線電設備可同步進行數據采集和生成。

二、Mini Massive MIMO原型驗證系統

本節將從系統的整體架構、系統時鐘和觸發信號的產生和分配、上下行鏈路的數據處理流程這三個方面對Mini Massive MIMO原型驗證系統進行詳細介紹,系統的實際測試結果與現場成果展示將放在第三節進行單獨介紹。

1.系統的整體架構

1)硬件部分

基于NI大規模MIMO應用程序框架所構建的Mini Massive MIMO原型驗證系統的系統框圖如下圖所示

?

圖3 Mini Massive MIMO原型驗證系統框圖

系統主要由NI的PXI機箱和軟件無線電節點USRP RIO系列組成,以下是系統框圖中所涉及的各組件的簡要介紹:

1、PXIe-1085機箱:18槽3U PXI Express機箱,包含有16個混合插槽和1個PXI Express系統定時插槽,每插槽可達4 GB/s的專用帶寬,整個機箱可達12 GB/s的系統帶寬。

2、PXIe-8135:NI PXIe-8135是基于Intel Core i7-3610QE處理器的高性能嵌入式控制器,配置了2.3 GHz基頻、3.3 GHz(單核Turbo Boost模式)四核處理器和雙通道1,600 MHz DDR3內存,可用于PXI系統。在外設方面,PXIe-8135包含2個SuperSpeed USB端口、4個高速USB端口、2個千兆以太網端口、GPIB、串口和其他外設。

3、PXIe-8374/ PXIe-8262:MXIe x4 Cabled PCIe接口板卡,可用于連接USRP RIO與PXI機箱以進行數據交換,實時的數據傳輸帶寬可達200MHz,最大傳輸速率可達800MB/s。

4、PXIe-6674T:定時和多機箱同步模塊,板載高穩定性10 MHz OCXO (50 ppb精度)和高精度DDS時鐘生成,分辨率可達0.3 Hz至1 GHz,該模塊可生成時鐘和觸發信號,生成的時鐘或觸發信號可在1個PXI Express機箱中的多個設備之間進行路由,也可路由至其他PXI和PXI Express機箱以及第三方儀器以實現整個系統的時鐘和觸發信號的精確同步。

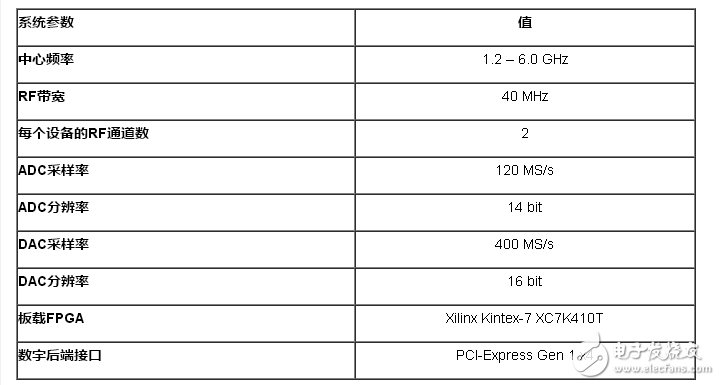

5、NI 2953R:USRP RIO系列軟件無線電節點,其內部包含一個可編程(Xilinx Kintex-7)FPGA和兩個40MHz 帶寬的RF收發器,中心頻點可配置在1.2-6GHz的頻段范圍內,最大的信號發射功率為15dBm,表1給出了NI 2953R的一些詳細硬件參數。

?

表 1 NI 2953R的詳細硬件參數

?

?

圖中,高性能嵌入式控制器PXIe-8135插于PXIe-1085機箱的第1個插槽,定時和多機箱同步模塊PXIe-6674T插于第10槽, 8個NI 2953R分別通過PXIe-8374或PXIe-8262接口板卡連接到PXIe-1085機箱的其它8個插槽,從而每個NI 2953R能夠以最大800MB/s的速率將數據匯集到PXI機箱并通過機箱背板進行板間數據交換以實現軟件無線電節點間、軟件無線電節點與PXIe-8135控制器間的數據傳遞。

由于所搭建的Mini Massive MIMO原型驗證系統是TDD系統,且采用簡化的LTE無線幀格式和使用OFDM無線傳輸技術,考慮到系統的可擴展性和系統未來帶寬的增加(如引入載波聚合等先進技術),同時為滿足系統速率要求和有限資源限制,Mini Massive MIMO在設計時考慮將整個系統劃分為多個子系統(并保留相關數據接口),每個子系統由8個NI 2953R和其對應的1個PXIe-1085機箱組成,負責處理分配給當前子系統的固定帶寬的數據,因而圖3所示的Mini Massive MIMO系統框圖實際僅為一個子系統的系統框圖,需要注意的是,除了所處理的數據所在頻帶不同外,各個子系統的結構與各部分功能均完全一致。

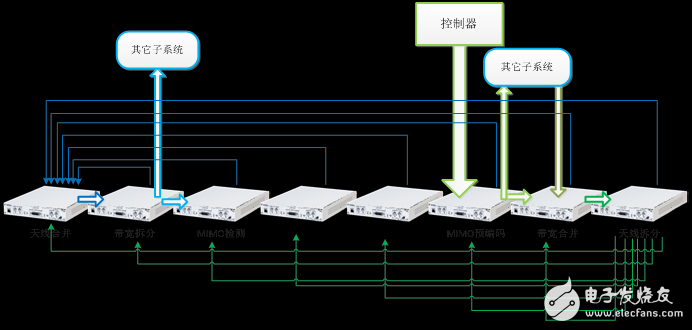

本文主要對當前子系統(即16*2的Mini Massive MIMO系統)進行介紹。根據實現功能的不同, 16*2的Mini Massive MIMO系統中的8個NI 2953R被劃分為不同的功能模塊,如圖4所示,它們分別是天線合并模塊、帶寬拆分模塊、信道估計模塊、MIMO檢測模塊、射頻通道校準模塊、MIMO預編碼模塊、帶寬合并模塊和天線拆分模塊。其中,天線合并模塊和天線拆分模塊分別負責匯聚來自各個天線的數據和將數據分發至各個物理天線,帶寬拆分模塊負責將該子系統中整帶寬的數據劃分成不同子帶并分配至其它子系統,帶寬合并模塊負責匯聚其它子系統傳輸過來的子帶的數據,MIMO檢測模塊和MIMO預編碼模塊則是分別負責對該子系統所負責的子帶數據進行檢測譯碼和預編碼。

?

圖4 系統功能模塊劃分

對于上行鏈路,接收到的數據首先會匯聚到天線合并模塊,然后由天線合并模塊傳遞給帶寬拆分模塊進行數據的按帶寬劃分以分配給不同的子系統,各子系統的信道估計模塊接收到來自帶寬拆分模塊的數據后進行信道估計,并將估計出的信道信息傳遞給MIMO檢測模塊以用于用戶數據的檢測;同樣的對于下行鏈路,要發送的數據首先由控制器傳送給MIMO預編碼模塊,MIMO預編碼模塊根據信道估計模塊和射頻通道校準模塊的信息對數據進行預編碼后將已預編碼的數據傳遞給帶寬合并模塊,以合并其它子系統所處理的帶寬的數據從而形成整帶寬數據,最后整帶寬的數據將會被傳送給天線拆分模塊以實現所要發送的數據被分配至各個實際的物理天線進行發送。

2)軟件部分

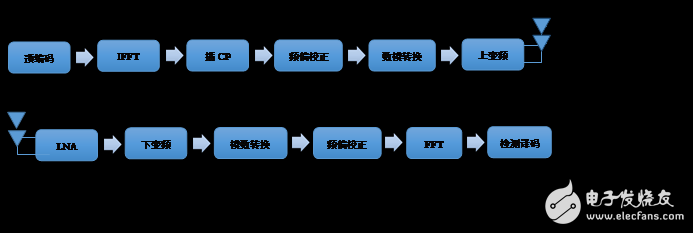

系統的軟件部分包括FPGA程序與上位機程序,其中,FPGA程序運行于NI 2953R上,主要完成接收信號或發射信號的下、上變頻,模數、數模轉換以及硬件部分所述的模塊功能,信號處理流程見圖10。

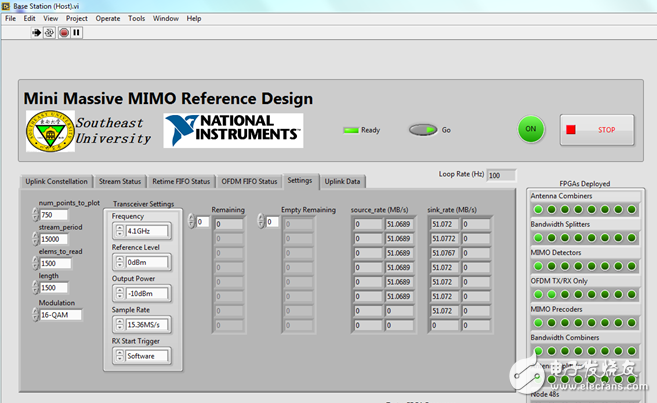

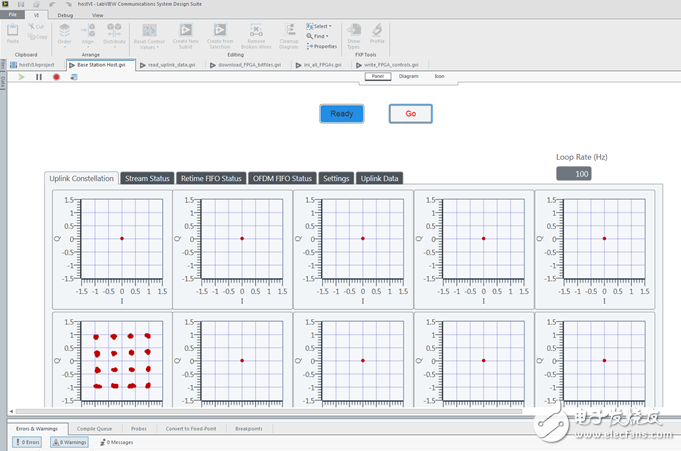

另一方面,上位機程序主要負責設置系統的相關參數、配置各NI 2953R、產生所需發送數據或顯示系統接收到的數據以及啟動或停止系統的運行,圖5和圖6給出了上位機程序的前面板。

?

圖5 上位機程序前面板一

圖中部的上行鏈路星座圖上顯示出當前有兩個用戶正在發送數據,且數據采用16QAM調制,圖左下角的簇控件中指示系統將USRP1配置為天線合并模塊,USRP2配置為帶寬拆分模塊,USRP3配置為MIMO檢測模塊,以此類推。

?

圖6 上位機程序前面板二

上圖給出了系統的相關參數的配置,包括系統的載波頻率,發送功率,采樣率,調制方式等等,如當前系統的載波頻率為4.1GHz,采樣率為15.36MS/s,調制方式為16QAM。上位機對系統的配置流程圖見圖7。

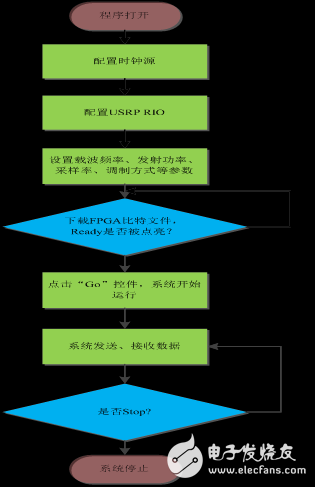

?

圖7 上位機對系統的配置流程

2. 系統時鐘和觸發信號的產生和分配

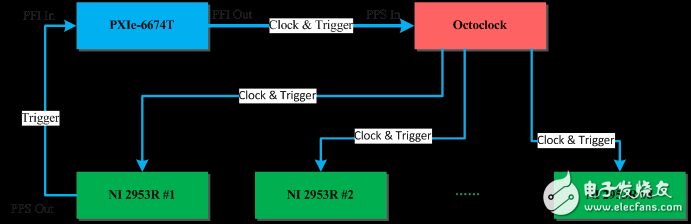

參考于NI 基于PXI和USRP RIO的可擴展大規模MIMO系統的時鐘連接,Mini Massive MIMO系統的時鐘和觸發信號分發網絡如圖8所示:

?

圖8 Mini Massive MIMO系統的時鐘和觸發信號分發網絡

系統采用OctoClock模塊構建時鐘和觸發信號分發網絡,系統的觸發信號和源時鐘信號從PXIe 6674T引出后輸入到OctoClock模塊進行路由和分發,而后OctoClock模塊輸出端的8路時鐘信號和8路觸發信號分別通過等長的傳輸電纜輸入到8個NI 2953R以確保系統各個NI 2953R的時鐘與觸發信號的同步。源觸發信號的產生是通過設定主NI 2953R然后在主NI 2953R中以軟件觸發的方式發出一個啟動脈沖來實現。該啟動脈沖信號(源觸發信號)在主設備的一個輸出端口上被引出,并輸入至PXIe-6674T中放大,然后傳遞到OctoClock模塊,并沿著電纜向下分布到系統中的各個NI 2953R設備(包括主設備自己),它的主要作用為設置參考時鐘邊沿以用于各個NI 2953R發射和接收時同步啟動采集。圖9為系統時鐘和觸發信號分發網絡的實物連接圖。初步測試結果顯示在此同步架構下,參考時鐘偏移在100 ps以內,觸發偏移在1.5 ns以內。

?

圖9系統時鐘和觸發信號分發網絡的實物連接圖

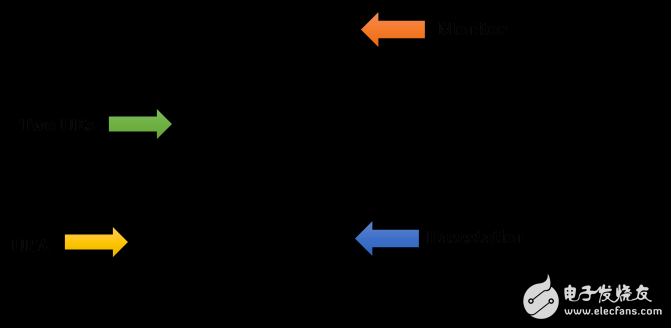

3. 上下行鏈路的數據處理流程

對于上行鏈路,系統中的8個NI 2953R的16根天線采集到的射頻信號經過射頻通道的低噪聲放大、下變頻和ADC采樣量化后被分別送入到各個NI 2953R的FPGA中進行下采樣、頻率偏移校正、IQ信號校正和FFT,之后壓入P2P FIFO或本地FIFO中以用于傳遞到相應模塊進行后續處理,如信道估計,信號檢測等。

?

圖10上下行鏈路的數據處理流程

對于下行鏈路,數據首先由控制器傳遞到MIMO預編碼模塊進行預編碼,然后通過帶寬合并和天線拆分模塊分發到8個NI 2953R,在各個NI 2953R的FPGA中進行OFDM調制、頻率偏移校正和IQ信號校正,校正過后的數據再被送入到各個射頻通道進行數模轉換和上變頻最后通過天線發送出去。

三、 系統的實測結果與現場成果展示

系統的實測結果如圖11所示。圖中展示的是在LabVIEW Communication下的程序前面板框圖,從圖中可以看出,當前有一個用戶在發送上行數據,數據調制方式為16QAM,由于沒有其它用戶干擾,星座圖的星座點較細系統性能較好。

?

圖11 LabVIEW Communication下系統實測結果

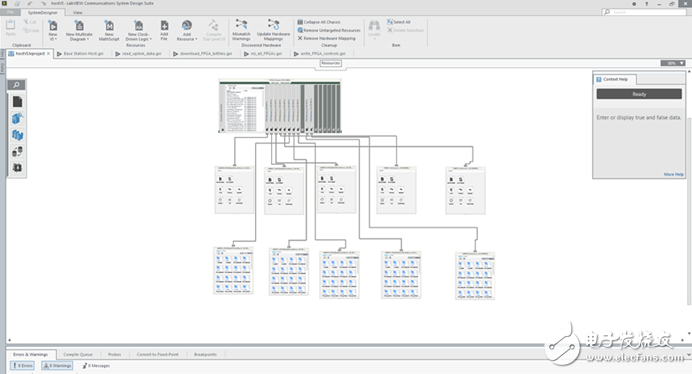

?

?

圖12 LabVIEW Communication下的System Designer所顯示系統邏輯連接圖

Mini Massive MIMO系統的實物圖見圖13和圖14,其中,圖13給出的是系統整體外觀,從上至下依次為系統Host端顯示器用于顯示接收信號星座圖,由兩個NI 2953R構成的兩個單天線用戶,由10個NI 2953R(其中2個為模擬其它子系統的存在)和PXIe-1085機箱構成的Massive MIMO系統的基站,以及8*2的UPA天線陣列。

?

?

圖13 系統實物圖

?

?

圖14 系統Host端顯示器

四、結論

本應用利用NI USRP RIO與PXI平臺,采用NI LabVIEW和LabVIEW Communication作為開發軟件,構建了面向5G無線通信技術的Mini Massive MIMO原型驗證系統。系統采取層次化設計,各部分功能模塊相對獨立,具有較強的可擴展性,系統的核心算法如OFDM調制解調、信道估計與MIMO檢測等均在高性能的FPGA端完成,滿足系統的實時性的要求,Mini Massive MIMO原型驗證系統非常適用于驗證和測試面向大規模MIMO無線通信系統的多種關鍵技術和算法性能。

電子發燒友App

電子發燒友App

評論