3.3.3 FPGA端設計

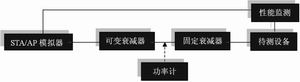

FPGA的設計比較復雜,也是數據處理部分的核心,這一部分主要完成基帶信號處理的關鍵工作,此外還負責射頻卡5791的配置、P2P傳輸、FPGA間同步設計。

(1)射頻卡5791配置

射頻卡的配置在FPGA中完成,主要完成將HOST傳遞過來的參數寫入射頻卡相應寄存器里,尤其是關于速率的小數變換。

系統基帶數據帶寬為20MHz,而AD/DA端采樣速率為130MHz,為了完成速率的匹配,必須對基帶數據作相應處理。對于發送端,通過插值處理將20MHz升至130MHz,實現方式為每隔130/20=6.5個時鐘周期從基帶數據FIFO中讀出數據,并進行擴展,形成130MHz的發送信號;類似的,接收端通過抽取方式實現130MHz降至20MHz,實現方式為每隔6.5個時鐘將接收到的數據寫入基帶處理FIFO中。

(2)P2P傳輸

P2P將兩塊FPGA的數據合并到一塊FPGA中,并在一塊FPGA中完成后續的MIMO基帶處理,因此在本系統中,P2P是實現MIMO的重要紐帶。

P2P的配置主要包含兩方面,在主機(HOST)端將一塊FPGA的寫入數據流和另一塊FPGA的讀取連接起來,在FPGA端,P2P數據讀取和寫入節點為數據交換提供FIFO的接口,這樣的接口類似于DMA和本地FPGA 的FIFO,如圖4所示。

(3)FPGA間同步設計

出于硬件平臺的局限性,兩根發射天線由兩塊FPGA分別連接,這樣的硬件架構帶來的問題就是如何保證兩根天線發出數據的同步性。這是任何一個設備平臺都需要考慮的問題,各個廠家也提供了不同的方案,NI利用其獨特的模塊化設計,FPGA之間存在trigger總線連接,利用trigger觸發實現同步。

當不同的設備之間共享triggers時,信號路徑的傳播延時會造成trigger到達設備的時間不同步。NI自帶的同步庫可以利用CPTR(同周期時間相關)減緩trigger的評估速率。關鍵是所有的設備都必須構建一個CPTR信號,這些CPTR信號之間同頻同相。

FPGA端的同步程序構建和關聯CPTR信號,這些CPTR信號在不同的FPGA間是同時產生的。CPTR信號是周期性的,采樣周期可以控制CPTR的周期。

(4)基帶信號處理設計

在基于IEEE802.11ac協議的系統中,發送端包括前導碼生成、信道編碼、流解析、比特交織、星座映射、插入導頻、添加CP、引入CSD以及IFFT轉換等過程;接收端包括時間同步、FFT轉換、去除CP、信道估計、信號均衡、去除導頻、解映射、比特解交織、逆流解析、信道解碼等過程。一些主要模塊的具體細節如下:

BCC編碼

采用IP核實現802.11ac標準規定的BCC編碼器,其生成多項是g0=133(8)和g1=171(8),分別對應于生成多項式S0(x) = x6 + x5 + x3 + x2 + 1和S1(x) = x6 + x3 + x2 + x1 + 1,可以使用移位寄存器來實現。卷積編碼后的兩路輸出相互合并再進行后續傳輸。根據不同的規則進行刪余打孔,BCC信道編碼器支持1/2、2/3、3/4、5/6四種編碼速率,以滿足更高的傳輸效率。

流解析與逆流解析

在經過信道編碼后,流解析將編碼比特被重新排成一組新的、等于空間流數(NSS)的比特串。其輸出為NSS路并行比特序列,每個串的長度為NCBPSS (每空間流編碼比特)。

逆流解析時流解析的逆過程,主要完成兩個數據流合并成一個流的過程。

調制與解調

星座映射過程是把比特序列以一定的方式映射到星座圖中的一個復數星座點。IEEE802.11ac支持的映射(調制)方式包括BPSK、QPSK、16QAM、64QAM和256QAM,各調制方式下每個子載波的復數星座點分別承載1、2、4、8和16個比特的信息,也即調制階數NBPSCS。前導碼字段中的信令字段均采用BPSK調制。生成數據字段時,根據信令字段中的MCS信息,子載波選擇相應的映射(調制)方式。在20MHz帶寬下,每個OFDM碼元是由52個有效的復數星座值組成;4MHz帶寬時這個有效值為108個。

解調是星座映射調制的逆過程,以恢復傳輸傳輸。

IFFT與FFT

實現發射端頻域數據到時域數據的轉換,同理,FFT則實現了接收端時域數據到頻域數據的轉換,以用于后續處理。

同步

在基于IEEE802.11ac協議的接收機中,同步過程主要包括時間同步,載波頻率同步和采樣時鐘同步。由于NI-PXI平臺具有優良的集成工藝和精密性,收發機的本振頻率幾乎一致,采樣時鐘也幾乎保持完全相同,因此在原型機系統設計中可以暫時忽略系統的載波頻率偏差和采樣時鐘偏差帶來的影響。因此本文原型機的接收端采用基于前導碼訓練序列的MIMO-OFDM系統時間同步方案。

時間同步的處理主要分為捕獲和跟蹤兩個階段,具體分為幀同步過程和符號同步過程。幀同步又稱作粗時間同步,用于檢測數據分組的到來,這是時間同步的捕獲階段;符號同步又稱作精時間同步,用于精確定位OFDM符號數據的起始位置,這是時間同步的跟蹤階段。

信道估計與均衡

信道估計是獲取信道信息的重要模塊,利用估計出的信道響應可以對接收端數據進行信道均衡操作從而恢復數據。IEEE802.11ac協議的信道估計采用定期發送訓練序列的方法,即利用前導碼中VHT-LTF的若干字段在頻域內進行信道估計。信道均衡則是對接收信號進行一定的補償操作,即對信號進行恢復與提取,為后續的解調和信道解碼過程打下基礎。利用之前得到的估計信道進行信道均衡過程,可以減輕或消除碼間干擾,使得系統能夠對抗無線信道衰落,從而提高無線系統的數據傳輸速率和頻譜效率。本原型機采用基于LS算法的信道估計和基于ZF算法的信道均衡。

維特比譯碼

本系統中采用Xilinx的IP Core實現Viterbi譯碼,其輸入采用基于幀形式的傳輸方式,需要重點考慮的是咬尾問題。因此需要在每一幀的最后添加6個零,使譯碼器回到初始狀態。

3.3.4 PC端設計

PC端主要完成視頻流的編碼打包,并加上CRC校驗碼,同時根據不同調制方式改變發送數據包的大小。之所以選擇用兩臺PC分別處理視頻流的收發,是因為考慮到LabVIEW對視頻流處理能力的薄弱,如果采用HOST端作視頻流的編解碼,這會耗用大量的CPU資源。因此NI儀器完全用來處理數據比特部分,而視頻流的一系列處理則用C#編寫的代碼進行。

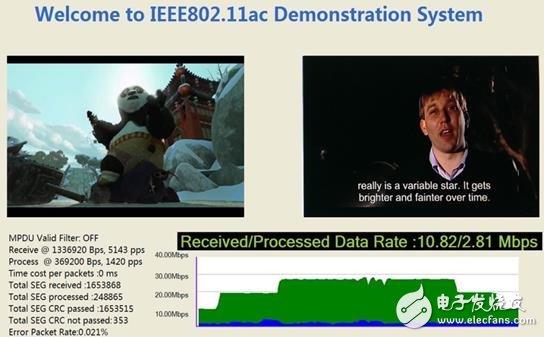

視頻數據發送用戶和接收用戶的用戶界面如圖5、圖6所示。發送用戶界面中可以顯示發送的視頻,當前采取的調制方式MCS,包長的大小,每次請求包的數目(不同調制方式請求的包數不同),HOST中斷請求次數等參數。而接收用戶界面中可以顯示接收到的視頻,傳輸速率、接收到包的總數,誤包率等參數。最主要的參數是Received Data Rate和Processed Data Rate。Processed Data Rate為傳輸的有效數據,也即實際視頻流傳輸數據速率。由于視頻流的包比較小,在其中添加了冗余信息來形成完整的包,Received Data Rate表示這種完整包的傳輸速率,也即物理層傳輸的數據速率。

圖5 PC端發送用戶界面

?

圖6 PC端接收用戶界面

4.基于NI-PXI的11ac原型機系統演示

關于原型系統的演示,分別從接收星座圖演示以及視頻流傳輸兩個角度進行分析,以便更好地測試系統的性能。

電子發燒友App

電子發燒友App

評論