本節(jié)將簡(jiǎn)單介紹在PlanAhead工具中如何應(yīng)用ChipScope核和分析工具進(jìn)行邏輯調(diào)試與驗(yàn)證。先通過(guò)一個(gè)向?qū)hipScope核插入設(shè)計(jì)中,選擇待測(cè)試的網(wǎng)線,并進(jìn)行例化、連接和綜合,最后,導(dǎo)入布局和時(shí)序報(bào)告,產(chǎn)生位流文件,用ChipScope分析器進(jìn)行驗(yàn)證。

1. 打開項(xiàng)目。

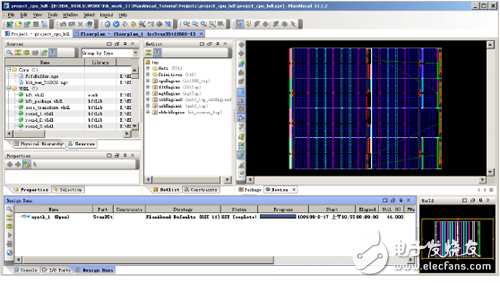

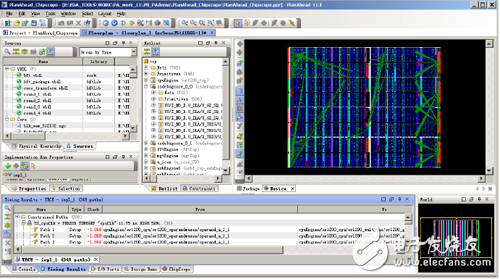

(1) 運(yùn)行PlanAhead,在目錄“PlanAhead_Tutorial\Projects\project_cpu_hdl”下找到“Project_cpu_hdl.ppr”項(xiàng)目并打開,PlanAhead窗口顯示如圖10-86所示。

圖10-86 【PlanAhead】窗口

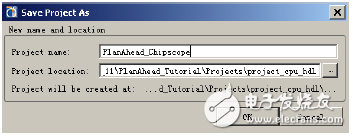

(2) 將項(xiàng)目存儲(chǔ)為另外一個(gè)項(xiàng)目,以確保原始項(xiàng)目不被損壞。運(yùn)行【File】→【Save Project as】,打開【Save Project As】對(duì)話框,按圖10-87中所示設(shè)置項(xiàng)目名和項(xiàng)目存儲(chǔ)路徑。

圖10-87 設(shè)置項(xiàng)目名和存儲(chǔ)路徑

2. 應(yīng)用【Set Up ChipScope】向?qū)А?/h2>

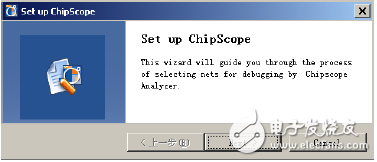

(1) 【Set Up ChipScope】向?qū)б龑?dǎo)設(shè)計(jì)者在綜合后網(wǎng)表中插入ChipScope的ICON核和ILA核,并選擇待測(cè)網(wǎng)線,設(shè)置插入的ChipScope核的數(shù)目,然后例化這些核,最后將所選網(wǎng)線和核連接起來(lái)。

(2) 運(yùn)行【Tools】→【Set Up ChipScope】向?qū)В瑢bArbEngine/m0/wb*網(wǎng)線連接到ChipScope核。如圖10-88所示。

圖10-88 【Set Up ChipScope】窗口

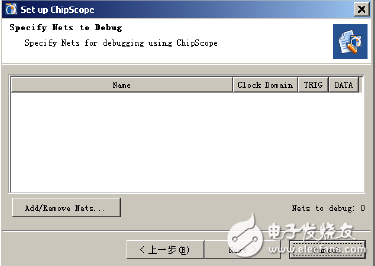

(3) 單擊【Next】,出現(xiàn)圖10-89所示的【Specify Nets to Debug】窗口。

圖10-89 【Specify Nets to Debug】對(duì)話框

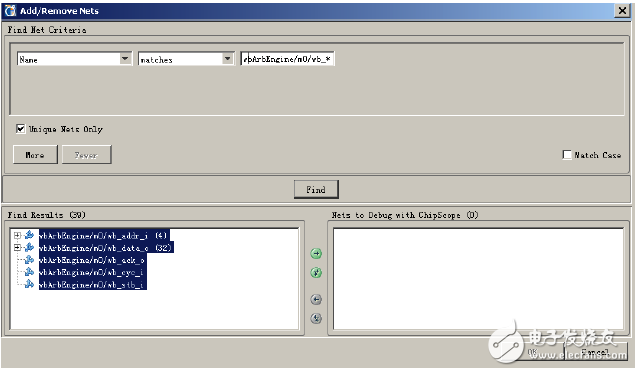

(4) 單擊【Add/Remove Nets】按鈕,出現(xiàn)圖10-90所示【Add/Remove Nets】對(duì)話框,按照?qǐng)D中所示設(shè)置查找匹配條件為wbArbEngine/m0/wb_*,單擊【Find】按鈕,查找結(jié)果會(huì)顯示在【Find Results】中。

圖10-90 查找結(jié)果

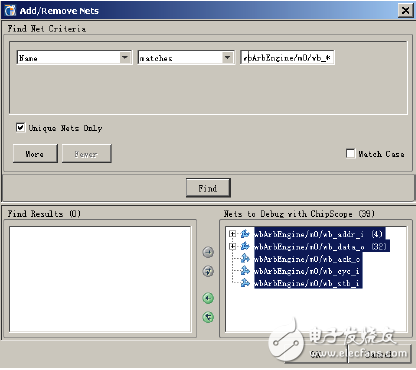

(5) 單擊按鈕,將查找到的網(wǎng)線選為待測(cè)試網(wǎng)絡(luò),如圖10-91所示。單擊【OK】退出網(wǎng)線設(shè)置對(duì)話框。

圖10-91 加入待測(cè)網(wǎng)線

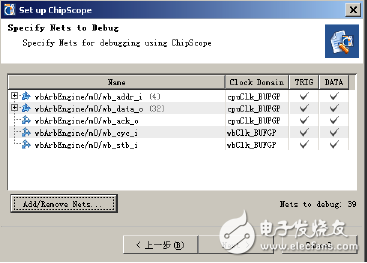

(6) 單擊【OK】退出網(wǎng)線設(shè)置對(duì)話框。這時(shí)的【Specify Nets to Debug】對(duì)話框顯示如圖10-92所示,可以看到,共加入了39個(gè)需要測(cè)試的網(wǎng)線。單擊【Next】按鈕,出現(xiàn)【Set Up ChipScope Summary】對(duì)話框,單擊【Finish】,在PlanAhead的【Netlist】窗口可以看到添加了ChipScope核后增加了csdebugcore_0_0、csdebugcore_0_1和u_icon,如圖10-93所示。

圖10-92 加入網(wǎng)線后的【Specify Nets to Debug】對(duì)話框

圖10-93 增加了ChipScope 核的【Netlist】窗口

3. 修改ChipScope 核和觸發(fā)信號(hào)的屬性。

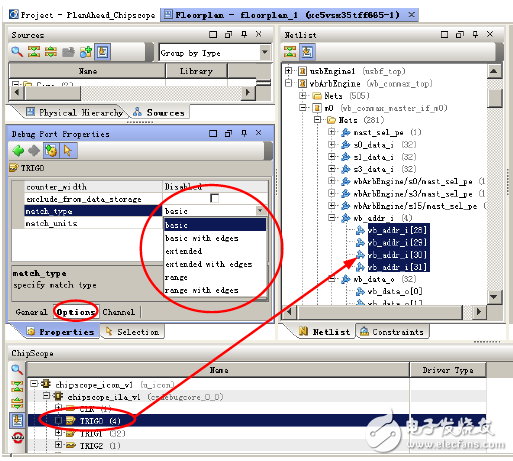

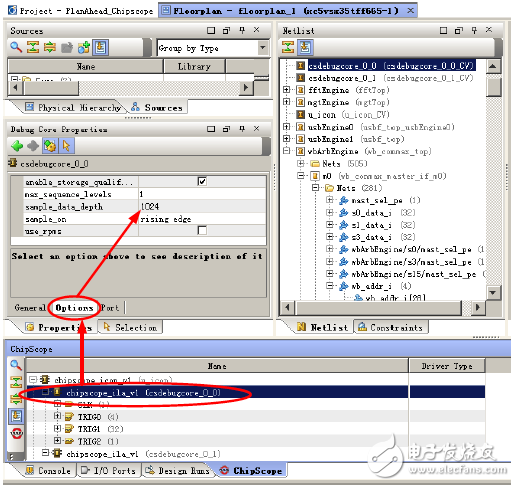

如圖10-94 所示,在【ChipScope】視圖選擇一組觸發(fā)信號(hào)TRIG0,在【Debug Port Properties】中選擇【Options】選項(xiàng)卡,可以改變match_type 屬性,選擇不同的觸發(fā)條件。

圖10-94 改變觸發(fā)屬性

如圖10-95 所示,在【ChipScope】視圖選擇ChipScope 的ILA 核,在【Debug Core Properties】中選擇【Options】選項(xiàng)卡,在這里可以修改該核的屬性,例如采樣深度和采樣時(shí)鐘邊沿。

圖10-95 改變ChipScope 核屬性

4. 實(shí)現(xiàn)ChipScope 核。

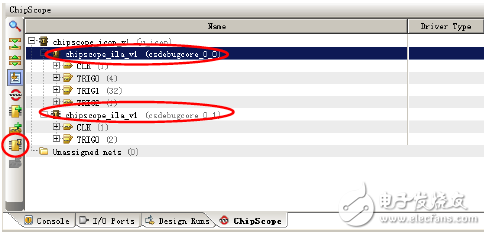

在圖10-96 所示【ChipScope】視窗選擇一個(gè)ILA 核,單擊按鈕,實(shí)現(xiàn)ChipScope 調(diào)試核【Implement ChipScope Debug Cores】,這個(gè)命令調(diào)用COREGen 工具,將黑盒子ChipScope 調(diào)試核轉(zhuǎn)換成綜合后ChipScope 核,然后就可以對(duì)其進(jìn)行翻譯、映射、布局布線。

圖10-96 實(shí)現(xiàn)ChipScope 核

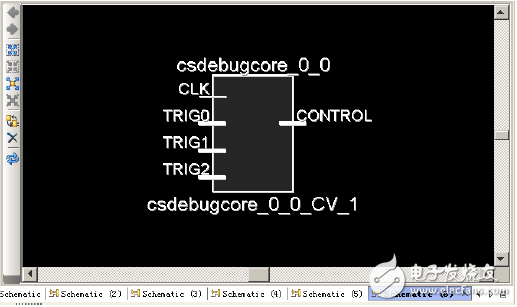

另外, 讀者可以在【ChipScope 】窗口選擇一個(gè)ILA 核, 單擊鼠標(biāo)右鍵選擇【Schematic】,可以看到ChipScope 核的原理圖模塊,如圖10-97 所示。

圖10-97 【Schematic】窗口

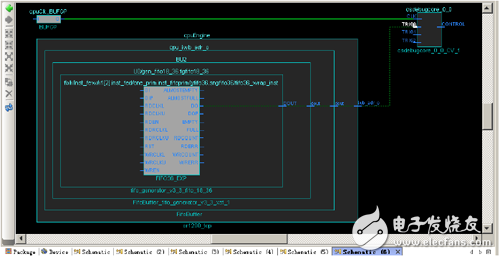

在【Schematic】窗口雙擊CLK和TRIG0引腳,再單擊按鈕,重新生成原理圖,如圖10-98所示。可以看到,TRIG0連接到了設(shè)計(jì)中的cpuEngine的地址端,這些信號(hào)由cpuClk時(shí)鐘控制。

圖10-98 【Schematic】窗口

需要注意的是,在設(shè)計(jì)中插入ChipScope核,會(huì)影響實(shí)現(xiàn)結(jié)果。因此建議將觸發(fā)器的輸出作為測(cè)試點(diǎn),并且使用區(qū)域約束(在PlanAhead中用Pblock),將ChipScope核與關(guān)鍵路徑約束在一起,使ChipScope核對(duì)時(shí)序的影響降至最小。

5. 實(shí)現(xiàn)設(shè)計(jì)。

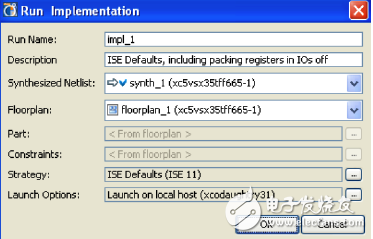

(1) 單擊工具欄的運(yùn)行實(shí)現(xiàn)圖標(biāo),出現(xiàn)【Run Implementation】對(duì)話框,如圖10-99所示,按圖中所示設(shè)置各參數(shù)。

圖10-99 【Run Implementation】對(duì)話框

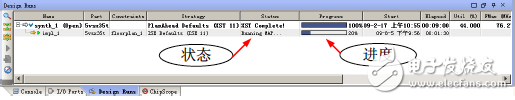

(2) 單擊【OK】按鈕,【Design Runs】窗口會(huì)增加impl_1 進(jìn)程,如圖10-100 所示,該實(shí)現(xiàn)進(jìn)程會(huì)簡(jiǎn)要顯示圖10-99 所示的設(shè)置,并且會(huì)顯示出該實(shí)現(xiàn)的當(dāng)前狀態(tài)及進(jìn)度信息。

圖10-100 【Design Runs】窗口

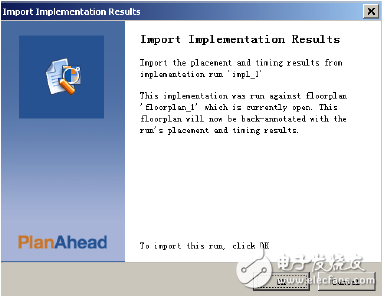

(3) 運(yùn)行結(jié)束后,雙擊impl_1 進(jìn)程,彈出【Import Implementation Results】對(duì)話框,提示是否導(dǎo)入impl_1 的布局和時(shí)序結(jié)果,單擊【OK】按鈕,impl_1 的實(shí)現(xiàn)結(jié)果會(huì)被反標(biāo)注到設(shè)計(jì)中。如圖10-101 所示。

圖10-101 【Import Implementation Results】對(duì)話框

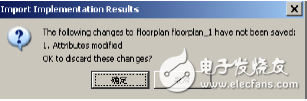

(4) 單擊圖10-101 中的【OK】按鈕,會(huì)彈出一個(gè)確認(rèn)對(duì)話框,如圖10-102,單擊【確定】按鈕,impl_1 的實(shí)現(xiàn)結(jié)果會(huì)被反標(biāo)注到設(shè)計(jì)中。同時(shí),圖10-103 所示【Device】窗口會(huì)顯示這一實(shí)現(xiàn)結(jié)果。

圖10-102 屬性更改確認(rèn)對(duì)話框

圖10-103 【Device】窗口顯示的impl_1實(shí)現(xiàn)結(jié)果

6. 產(chǎn)生.bit位流文件。

在【Design Run】窗口選中impl_1,在右鍵菜單中選擇運(yùn)行【Run Bitgen】命令,彈出圖10-104所示對(duì)話框,單擊【OK】按鈕,生成.bit文件。

圖10-104 【Run Bitgen】對(duì)話框

7. 啟動(dòng)ChipScope分析儀。

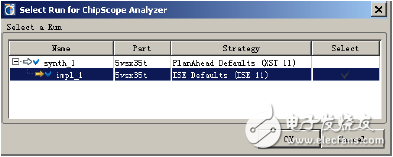

在【Design Run】窗口選中impl_1,在右鍵菜單中選擇運(yùn)行【Launch ChipScope Analyzer】命令,彈出圖10-105所示對(duì)話框,選擇impl_1(如果設(shè)計(jì)中運(yùn)行產(chǎn)生了多個(gè)實(shí)現(xiàn)結(jié)果,這里會(huì)顯示多個(gè)實(shí)現(xiàn)),單擊【OK】啟動(dòng)ChipScope分析器。使用ChipScope分析儀的步驟請(qǐng)參考相關(guān)章節(jié),這里不再贅述。

圖10-105 【Select Run for ChipScope Analyzer】對(duì)話框

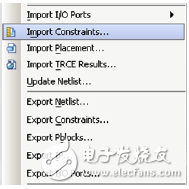

在PlanAhead的【File】菜單欄有一些導(dǎo)入導(dǎo)出功能。設(shè)計(jì)者可以導(dǎo)入I/O引腳文件、約束文件、位置約束文件、時(shí)序文件以及更新網(wǎng)表。設(shè)計(jì)者可以將PlanAhead的實(shí)現(xiàn)結(jié)果,通過(guò)運(yùn)行【Export Netlist…】導(dǎo)出EDIF格式的網(wǎng)表文件,運(yùn)行【Export Constraints…】導(dǎo)出相關(guān)的約束文件,然后將這兩個(gè)文件導(dǎo)入ISE中進(jìn)行布局布線等后續(xù)操作。還可以導(dǎo)出Pblock文件、IP文件、I/O端口文件等。

圖10-106 【File】菜單的導(dǎo)入輸出功能

10.9 小結(jié)

本章重點(diǎn)介紹了如何在PlanAhead中進(jìn)行RTL源代碼開發(fā)與分析,如何進(jìn)行I/O規(guī)劃,如何進(jìn)行時(shí)序分析,如何進(jìn)行布局規(guī)劃,以及在PlanAhead中如何使用ChipScope邏輯分析工具。在PlanAhead中導(dǎo)入綜合網(wǎng)表、約束文件以及ISE的布局布線結(jié)果的操作流程與上述介紹的過(guò)程類似,這里不再贅述。有興趣的讀者可以參考Xilinx相關(guān)的設(shè)計(jì)文檔。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論