基于FPGA的軟件濾波算法設(shè)計(jì)及實(shí)現(xiàn)

隨著數(shù)字電子技術(shù)的發(fā)展,數(shù)字電路已由早期的分立元件逐漸發(fā)展成集成電路,對(duì)電路設(shè)計(jì)的要求越來(lái)越高。尤其是可編程邏輯器件的出現(xiàn),使得以硬件為載體、以計(jì)算機(jī)軟件為開(kāi)發(fā)環(huán)境的現(xiàn)代數(shù)字系統(tǒng)的設(shè)計(jì)方法日趨成熟。可編程邏輯器件設(shè)計(jì)靈活、功能強(qiáng)大、可在線修改、效率高等優(yōu)點(diǎn)深受廣大電子設(shè)計(jì)人員青睞。目前,大多數(shù)現(xiàn)場(chǎng)可編程邏輯陣列( FPGA)芯片是電壓敏感型芯片,基于可重構(gòu)CMOS-SRAM單元結(jié)構(gòu),數(shù)據(jù)具有易失性,工作在低電壓狀態(tài),易受干擾,尤其在工控、軍用場(chǎng)合,外界電磁環(huán)境惡劣,電路耦合、空間輻射的雜波脈沖均會(huì)對(duì)FPGA工作的穩(wěn)定性產(chǎn)生影響。

干擾脈沖和毛刺信號(hào)是影響FPGA穩(wěn)定工作的主要因素,為了保證輸入信號(hào)每變化一次,電路只做出一次正確的響應(yīng),必須對(duì)輸入信號(hào)進(jìn)行濾波處理。要實(shí)現(xiàn)信號(hào)濾波可以采用硬件濾波和軟件濾波兩種方法。與硬件濾波相比,軟件濾波不需要硬件電路的支持,從而可以減少元器件的使用,降低成本,更重要的是軟件濾波更易于修改,所以常采用軟件濾波的方法來(lái)實(shí)現(xiàn)電路中的信號(hào)濾波問(wèn)題。通過(guò)VHDL語(yǔ)言編程實(shí)現(xiàn)信號(hào)濾波功能,介紹了延時(shí)濾波法和判決濾波法,并通過(guò)實(shí)驗(yàn)證明了上述兩種濾波方法的可靠性。

1延時(shí)濾波

延時(shí)濾波法的濾波原理是對(duì)輸入信號(hào)的脈沖寬度進(jìn)行鑒別,對(duì)那些與真實(shí)信號(hào)的寬度相差很大的干擾信號(hào)進(jìn)行有效的抑制。具體的實(shí)現(xiàn)流程為在檢測(cè)到輸入信號(hào)的狀態(tài)發(fā)生變化后,延時(shí)一段時(shí)間T,脈沖寬度小于延時(shí)時(shí)間T的輸入信號(hào)被認(rèn)為是干擾信號(hào),將其濾除;脈沖寬度大于延時(shí)時(shí)間T的輸入信號(hào)則被認(rèn)為是真實(shí)信號(hào),將其輸出。針對(duì)不同脈沖寬度的干擾信號(hào),可以通過(guò)設(shè)置不同的參數(shù)來(lái)實(shí)現(xiàn)相應(yīng)的信號(hào)延時(shí),從而達(dá)到有效濾波的目的。

1. 1延時(shí)時(shí)間T的確定

延時(shí)時(shí)間T取決干擾信號(hào)的脈沖寬度T‘。延時(shí)時(shí)間T太短( T<T’),濾波不完整,脈沖寬度大于T的干擾信號(hào)仍然會(huì)造成電路的誤動(dòng)作;延時(shí)時(shí)間T太長(zhǎng)( T>>T‘),會(huì)造成資源的浪費(fèi),降低電路的工作效率。

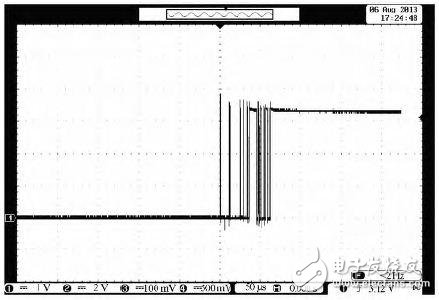

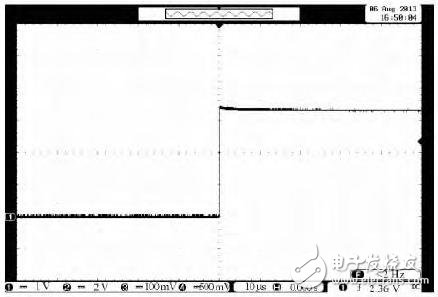

這里以某型號(hào)的扭子開(kāi)關(guān)輸入信號(hào)為例來(lái)介紹如何確定延時(shí)時(shí)間T.由于扭子開(kāi)關(guān)的機(jī)械觸點(diǎn)存在彈性作用,當(dāng)撥動(dòng)開(kāi)關(guān)時(shí),都不可避免地要在觸點(diǎn)閉合及斷開(kāi)的瞬間產(chǎn)生一連串的抖動(dòng)。為了能夠更準(zhǔn)確地估測(cè)撥動(dòng)開(kāi)關(guān)時(shí)產(chǎn)生的干擾脈沖寬度T‘,可以用示波器對(duì)開(kāi)關(guān)信號(hào)進(jìn)行多次測(cè)量,經(jīng)測(cè)量發(fā)現(xiàn)這種扭子開(kāi)關(guān)信號(hào)的抖動(dòng)時(shí)間不會(huì)超過(guò)1.5ms.圖1為沒(méi)有經(jīng)過(guò)濾波處理的開(kāi)關(guān)信號(hào)波形。

圖1中,橫坐標(biāo)表示時(shí)間,每格代表50μs,縱坐標(biāo)表示電壓,每格表示1 V.從圖中可以明顯看出,在開(kāi)關(guān)信號(hào)達(dá)到穩(wěn)定狀態(tài)之前,有一連串的抖動(dòng),抖動(dòng)時(shí)間不到1. 5 ms.這里根據(jù)實(shí)際情況,確定延時(shí)時(shí)間T = 2 ms.

1. 2延時(shí)濾波程序設(shè)計(jì)

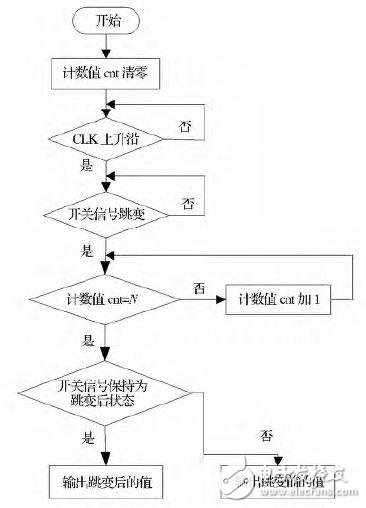

延時(shí)濾波程序采用一個(gè)計(jì)數(shù)器來(lái)實(shí)現(xiàn),計(jì)數(shù)器的模值N取決于延時(shí)時(shí)間T和采樣時(shí)鐘CLK的周期TCLK.若計(jì)數(shù)器的初始值為0時(shí),則N = T /TCLK-1.圖2為編寫(xiě)延時(shí)濾波程序的流程圖。

圖1未經(jīng)過(guò)濾波處理的開(kāi)關(guān)信號(hào)

圖2延遲濾波程序流程圖

當(dāng)檢測(cè)到開(kāi)關(guān)信號(hào)的狀態(tài)發(fā)生變化時(shí)(這里以由‘0’變到‘1’為例),計(jì)數(shù)器開(kāi)始計(jì)時(shí),當(dāng)計(jì)數(shù)器的計(jì)數(shù)值計(jì)到N時(shí),如果開(kāi)關(guān)信號(hào)仍保持為變化之后的狀態(tài)‘1’,則輸出‘1’,否則,認(rèn)為這是一個(gè)干擾脈沖,將其濾除。

當(dāng)采樣時(shí)鐘的頻率為5 kHz時(shí),TCLK = 0. 2 ms,要實(shí)現(xiàn)2 ms的延時(shí)時(shí)間,若計(jì)數(shù)器初始值為0,那么計(jì)數(shù)器模值N = 9.具體的VHDL語(yǔ)言程序進(jìn)程如下:

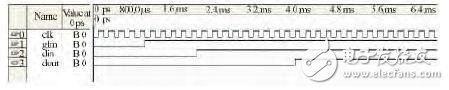

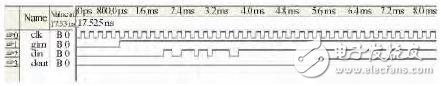

1. 3延時(shí)濾波程序仿真

分別將開(kāi)關(guān)信號(hào)din設(shè)置成理想信號(hào)和抖動(dòng)信號(hào),利用QuartusⅡ8. 0軟件進(jìn)行仿真,圖3和圖4分別為理想信號(hào)和抖動(dòng)信號(hào)的延時(shí)濾波仿真波形圖。

圖3理想開(kāi)關(guān)信號(hào)延時(shí)濾波仿真波形

圖4抖動(dòng)開(kāi)關(guān)信號(hào)延時(shí)濾波仿真波形

圖中clk為采樣時(shí)鐘,glrn為復(fù)位信號(hào),din為開(kāi)關(guān)輸入信號(hào),dout為延時(shí)濾波輸出信號(hào)。從圖3可以看出,從開(kāi)關(guān)信號(hào)發(fā)生變化到輸出發(fā)生變化的時(shí)間延時(shí)為2 ms,從圖4中可以看出,此延時(shí)濾波程序有效消除了扭子開(kāi)關(guān)的抖動(dòng)干擾,驗(yàn)證了其理論可行性。

1. 4延時(shí)濾波程序?qū)嶋H驗(yàn)證

為了驗(yàn)證此延時(shí)濾波程序的實(shí)際濾波效果,將其下載到Xilinx公司的Spartan3系列FPGA芯片XC3S400中,用示波器多次測(cè)量經(jīng)過(guò)濾波后的開(kāi)關(guān)信號(hào),得到圖5所示的輸出信號(hào)波形。圖5中,橫坐標(biāo)表示時(shí)間,每格代表10μs,縱坐標(biāo)表示電壓,每格表示1 V.從圖5可以看出,經(jīng)過(guò)濾波后的開(kāi)關(guān)信號(hào)不再有抖動(dòng)現(xiàn)象,此延時(shí)濾波程序的實(shí)際可靠性得到驗(yàn)證。

圖5延時(shí)濾波后的輸出信號(hào)波形

1. 5延時(shí)濾波程序資源占用率

在電子電路的設(shè)計(jì)中,F(xiàn)PGA的資源占用率是我們應(yīng)該考慮的一個(gè)重要問(wèn)題。如果FPGA的資源占用率太大,會(huì)加重FPGA的負(fù)擔(dān),影響整個(gè)電路的運(yùn)行速度。表1為延時(shí)濾波程序在XC3S400芯片中的資源占用情況。

表1延時(shí)濾波程序的資源占用情況

1. 6延時(shí)濾波的特點(diǎn)

延時(shí)濾波比較適合對(duì)脈沖寬度已知的干擾信號(hào)進(jìn)行濾波,這樣可以更準(zhǔn)確地確定延時(shí)時(shí)間,既不會(huì)因?yàn)檠訒r(shí)時(shí)間太短而導(dǎo)致濾波不理想,又不會(huì)因?yàn)檠訒r(shí)時(shí)間過(guò)長(zhǎng)而導(dǎo)致資源浪費(fèi)。而且,延時(shí)程序不僅可以有效地消除開(kāi)關(guān)類信號(hào)的抖動(dòng),還可以濾去干擾、噪音等其他尖峰波,抗干擾強(qiáng),可靠性高。

如果電路中存在多路輸入信號(hào)時(shí),當(dāng)檢測(cè)到任意一路輸入信號(hào)狀態(tài)發(fā)生變化時(shí)即執(zhí)行延時(shí)程序,在執(zhí)行延時(shí)程序的過(guò)程中將檢測(cè)不到其他輸入狀態(tài)的變化,所以能夠識(shí)別的動(dòng)作間隔不可能小于延時(shí)時(shí)間T,特別是當(dāng)多路輸入信號(hào)的狀態(tài)集中在短時(shí)間內(nèi)變化時(shí),電路的性能會(huì)嚴(yán)重下降。并且,由于頻繁執(zhí)行延時(shí)程序,會(huì)影響系統(tǒng)的效率和實(shí)時(shí)性。

2判決濾波

判決濾波是一種基于概率統(tǒng)計(jì)的濾波方法。在采樣時(shí)鐘CLK的控制下,每隔時(shí)間t對(duì)開(kāi)關(guān)信號(hào)進(jìn)行一次采樣,并對(duì)時(shí)間T0內(nèi)采集到的n個(gè)采樣值進(jìn)行判斷( n = T0 /t),如果這n個(gè)采樣值中高電平‘1’的個(gè)數(shù)百分比大于X,則輸出高電平;相反,如果低電平‘0’的個(gè)數(shù)百分比大于X,則輸出低電平。

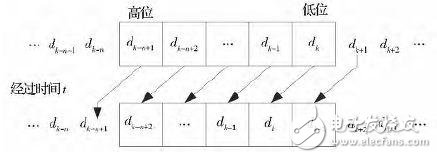

采用一個(gè)n位寄存器來(lái)實(shí)現(xiàn)判決濾波,寄存器各個(gè)位的值依次為采樣得到的n個(gè)采樣值。寄存器的模型如圖6所示。

圖6寄存器模型

在圖6中,n個(gè)格子分別代表寄存器的n個(gè)位,寄存器左側(cè)的數(shù)據(jù)為已經(jīng)處理過(guò)的數(shù)據(jù),寄存器內(nèi)的n個(gè)數(shù)據(jù)為正在處理的數(shù)據(jù),寄存器右側(cè)的數(shù)據(jù)為即將處理的數(shù)據(jù)。每過(guò)一個(gè)采樣時(shí)間間隔t,數(shù)據(jù)依次向高位滑動(dòng)一位,最低位賦值為輸入信號(hào)當(dāng)前的狀態(tài)值。

如上述過(guò)程,寄存器內(nèi)的數(shù)據(jù)在不斷地更新,數(shù)據(jù)每滑動(dòng)一次,即對(duì)n個(gè)采樣值進(jìn)行一次判斷,從而達(dá)到濾波的目的。由于干擾脈沖的隨機(jī)性,采到高電平和低電平的概率是相等的,所以,作為判斷依據(jù)的百分比X不能小于50%.在實(shí)際應(yīng)用中,為了使濾波更可靠,X的取值一般都大于50%.

2. 1判決濾波程序設(shè)計(jì)

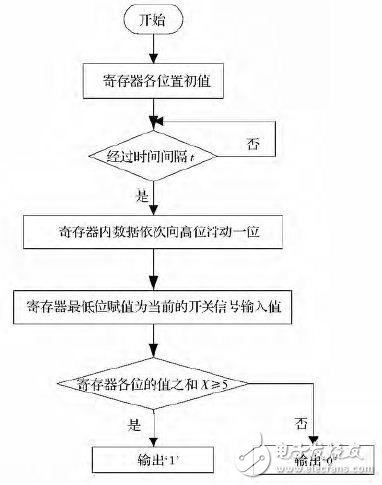

本設(shè)計(jì)采用一個(gè)9位寄存器( n = 9),每次判斷時(shí)只要‘1’的個(gè)數(shù)大于或等于5,則濾波輸出‘1’,否則輸出‘0’( X = 5 /9)。圖7為判決濾波程序的流程圖。

圖7判決濾波程序流程圖

主要的程序進(jìn)程如下:

3 結(jié)論

實(shí)驗(yàn)證明延時(shí)濾波和判決濾波均能達(dá)到很好的濾波效果,在電路的設(shè)計(jì)過(guò)程中,可以根據(jù)干擾信號(hào)的類型選擇合適的濾波方法。在實(shí)時(shí)性要求不是很高、干擾信號(hào)脈沖寬度可估測(cè)的電路中,可以采用延時(shí)濾波法,既節(jié)省資源又能有效濾除干擾信號(hào); 在實(shí)時(shí)性要求比較高、運(yùn)行速度比較快、干擾信號(hào)脈沖寬度很窄的電路中,可以采用判決濾波法,既能有效濾波又能保證電路的效率。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論