1 引言

在信息技術高速發展的今天,電子系統數字化已經成為有目共睹的趨勢,從傳統應用中小規模芯片構造電路系統到廣泛地應用單片機,到今天DSP及FPGA在系統設計中的應用,電子設計技術已邁入了一個全新階段。FPGA不僅具有容量大,邏輯功能強的特點,而且兼有高速、高可靠性。隨著EDA技術的發展和VLSI工藝技術的進步,特別是軟/硬件IP芯核產業的迅猛發展,可編程片上系統(SOPC)己經大量使用。本文通過對高精度數字電源系統的研發,提出了FPGA在數字電源控制器的應用思路。

?

2 系統組成

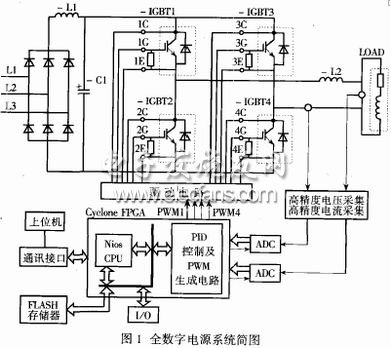

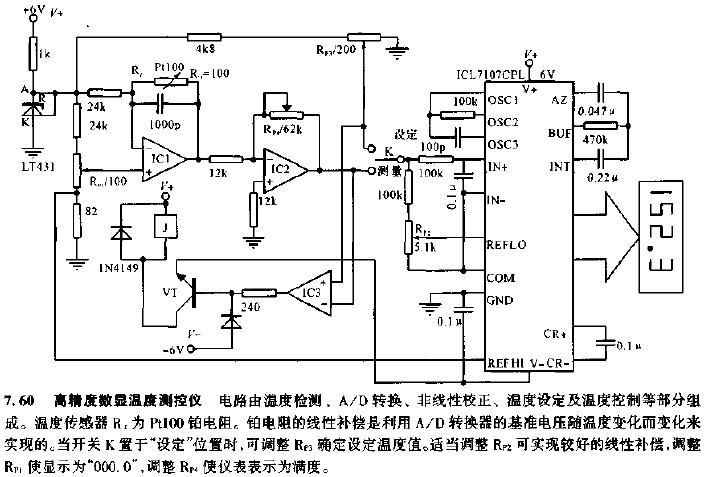

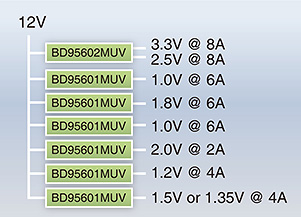

本系統是以單片現場可編程門陣列(FPGA)為基礎的全數字控制的高精度開關電源。數字控制的H橋脈寬調制的DC-DC變換器電源系統如圖1所示。

圖中,功率主電路由三相整流器、低頻LC濾波電路、DC-DC功率變換器、輸出高頻濾波電路等幾部分構成;控制及調節功能主要由基于FPGA的數字電源控制器完成,可以按設計要求來調節電源輸出電壓、電流。

FPGA中主要分兩大模塊,第一個模塊是由軟核CPU組成的通訊管理模塊;第二個模塊由幾個DSP塊組成,主要完成調節器的PI或PID運算、高分辨率PWM信號的產生以及數字濾波等。

在PWM開關電源中,PWM波形的產生及其準確調制至關重要。當使用FPGA數字控制器時,電流環及電壓環的調節方式為數字化的PI(比例積分)或PID(比例積分微分)調節,反饋電流或電壓信號經過A/D(模擬/數字)轉換后輸入到控制器,由控制器調節脈沖的寬度。

采用上述方案的數字化電源相對于傳統的模擬控制方式,具有顯而易見的優勢。對于不同的負載對象,可以通過在軟件中修改調節器參數來滿足指標要求,并且可以按照實際需要自由配置成為單環或雙環控制系統。這些都是在軟件中完成的,系統控制調節單元的硬件無需重復配置。

3 軟核Nios CPU

在QuartusII開發軟件中使用SOPC Builder開發工具可以快速構造一個Nios軟核CPU,嵌入到FPGA器件中,Nios軟核CPU如圖2所示。在本例中構造了UART-RS232、Ethernet通訊功能,LCD液晶屏顯示功能,數字量、開關量I/O及外部數據存儲管理等功能,通過Nios II的集成開發環境Nios II IDE,使用C/C++高級語言對Nios軟核CPU進行編程。就能完成FPGA同上位機RS232口或者Ethernet網的通訊、本地信息采集及顯示、數據存儲管理等。在FPGA內部通過地址總線和數據總線來管理其他DSP塊或IP核的協調工作。

4 調節器算法(PI或PID)

?

調節器的算法在數字電源是一個至關重要的環節,它的好壞直接影響到電源系統的各項性能指標。

以某加速器六極磁鐵所需電源為對象,主要參數如下:

磁鐵:Rm=0.14H,Lm=0.266mΩ

電源:Un=70V,電壓紋波小于1×10-3(1kHz以下);

In=200A,電流紋波小于5×10-5,跟蹤誤差小于1×10-4。

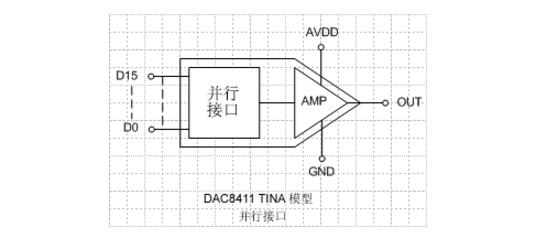

若采用電流單閉環控制,并采用PI調節器,仿真的系統模型如圖3所示。

?

圖3中,上位電流給定信號通過16位DAC轉換后,與DCCT輸出的電流反饋信號進行比較,得到誤差信號,此誤差經過誤差放大器放大后送入PI調節器,由調節器的輸出來控制PWM并驅動功率器件,從而實現負載對象所要求的高精度輸出電流。

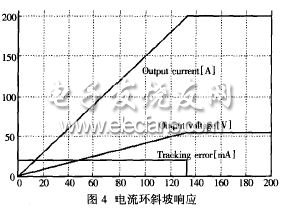

在Matlab/Simulink中對圖3所示系統加以斜坡給定,可仿真得到系統響應如圖4所示。可以看出系統無超調,跟蹤誤差小于0.02A(0.02/200=1×10-4),滿足系統要求的指標。

?

仿真完成后可以通過DSPBuilder系統設計工具構造一個含有HDL語言的PID功能的DSP塊。這個DSP塊可以作為一個IP核供FPGA直接調用。其輸出用于PWM調制。

5 高精度PWM脈沖的生成

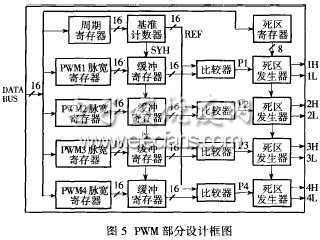

FPGA實現PWM部分設計框圖如圖5所示。

?

PWM的生成主要由脈寬寄存器、緩沖寄存器、周期寄存器、死區寄存器、死區發生器、數值比較器、控制邏輯等部分組成。脈寬寄存器,決定各路PWM信號的脈寬;緩沖寄存器,實現對脈寬數據的緩沖;周期寄存器,決定PWM的斬波周期;死區寄存器,決定H橋臂的死區時間。脈寬寄存器在每個開關周期更新一次,其輸出數據經緩沖后與基準計數器進行數值比較,得到各路PWM信號。再經死區電路處理,最后產生4路PWM驅動信號,驅動相應的功率器件。

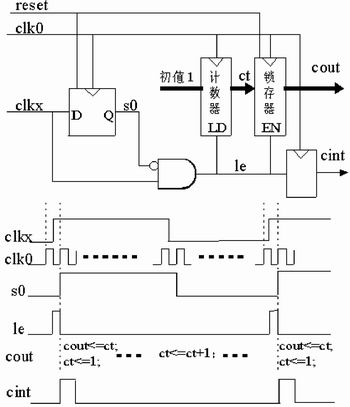

基準計數器,用來產生類似模擬電路中的三角波基準,是一個最小計算值為0,最大計算值為周期寄存器中保存的數值、計數方向交替變換的可逆計數器。基準計數單元在最大計數值時產生一個同步信號SYN,當其有效時將4個脈沖寬度的數據存入各自的緩沖寄存器,實現雙緩沖,使各個脈沖寬度寄存器在SYN無效時可依次更新而不影響最終的功率器件導通。

6 結束語

本文以FPGA芯片EP1C20為核心,敘述了實現數字化電源控制調節器的一種方法,根據現場工藝要求在FPGA中可靈活配置控制方案而無需重新配置硬件,外圍電路(如ADC、DAC等)選用高精度、低溫漂的器件,從而實現高精度的數字化電源,這是模擬系統所不及的。同時,由于控制調節的核心采用了數字化電路,系統自身的抗干擾能力明顯優于模擬系統。

目前,在很多應用領域中,需要數十臺甚至更多電源同時協調工作,即適應網絡化電源應用,而上述方案的數字化電源,通過Nios軟核CPU的強大通訊功能,可以很方便的實現批量電源的網絡化管理。

?

電子發燒友App

電子發燒友App

評論