本文首先提出了一種基于有限狀態機的電梯控制器算法,然后根據該算法設計了一個三層電梯控制器,該電梯控制器的正確性經過了仿真驗證和硬件平臺的驗證。本文的電梯控制器設計,結合了深圳信息職業技術學院的實際電梯的運行情況,易于學生理解和接受,對于工學結合的教學改革,是一個非常好的實踐項目。另外,本文提出的電梯控制器算法適合于任意樓層,具有很強的適應性和實用性。

電子設計自動化技術是19世紀末21世紀初新興的技術,其在數字電路設計和日常的控制系統中已經體現了強大的功能和優勢。隨著EDA技術的高速發展, 電子系統設計技術和工具發生了深刻的變化,大規模可編程邏輯器件FPGA的出現,給設計人員帶來了諸多的方便。HDL(硬件描述語言)是隨著可編程邏輯器件(PLD)發展起來的,主要用于描述數字系統的結構、行為、功能和接口,是電子設計自動化(EDA)的關鍵技術之一。它通常采用一種自上而下的設計方法,即從系統總體要求出發進行設計。

目前從期刊雜志中看到一些采用FPGA實現電梯控制系統的設計文章,在這些文章中看不到針對任意樓層的控制器算法,而針對任意層數的控制器算法是保證控制器實用性和適用性的關鍵。因此,本文嘗試采用EDA技術來設計一個N層電梯控制系統,具體思路是:首先給出電梯控制器的算法,然后在硬件平臺上實現并驗證。

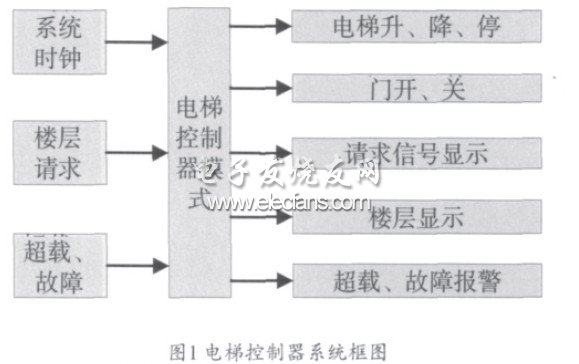

1 電梯控制系統要求

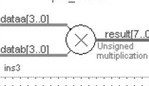

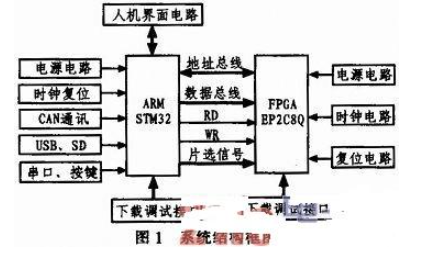

電梯控制系統通常包含圖1中的功能:電梯升、降、停;電梯門開、關;請求信號顯示、樓層顯示;超載、故障報警。其中超載、故障報警需要用到傳感器,該控制相對比較簡單,因此本文不再展開討論。

?

針對深圳信息職業技術學院第一教學樓的電梯,其電梯控制器實現了以下功能:

(1)電梯內部每層均有相應的STop按鈕;電梯外部除頂層外每層都有up按鈕,除底層外每層都有down按鈕;up按鈕被按下表示該層有人要去高層,down按鈕被按下表示該層有人要去低層,stop按鈕被按下表示該層有人要出電梯。對于stop、up、down按鈕,當被按下后,相應的指示燈亮,直到該請求被滿足后,指示燈才滅;

(2)電梯運行過程中,上升、下降、停止時相應的指示燈要亮,樓層隨時顯示;

(3)電梯上升過程中,首先滿足向上的需求,對于低層或者向下的需求,在電梯上升過程中會記錄該需求,然后在電梯向上需求全部滿足后電梯再次下降的過程中給予滿足;

(4)電梯下降過程中,首先滿足向下的需求,對于高層或者向上的需求,在電梯下降過程中會記錄該需求,然后在電梯向下需求全部滿足后電梯再次上升的過程中給予滿足。

本文設計的電梯控制器,其基本要求就是滿足上述實際運行電梯的要求。

2 電梯控制系統實現

2.1 整體方案設計

整體設計由四個模塊組成,各模塊功能具體描述如下:

a. 分頻器模塊:該模塊實現了任意時鐘頻率輸入,任意頻率輸出的功能,輸出頻率精度為1Hz;模塊輸入為系統工作時鐘clk,系統復位信號rst,輸出為分頻時鐘。模塊定義如下:

module freq_div(reset,clk,keyclk,liftclk);

模塊中keyclk為處理按鍵時鐘,liftclk為電梯運行控制時鐘。

b. 按鍵請求模塊:該模塊實現了記錄并處理各樓層的up、down和stop按鈕被按下的情況,模塊端口如下:

module key_req(

reset,keyclk,

stop, //電梯間內部各層按鈕,每1位代表1層,當相應位置1時表示指示該層的按鈕被按下;

up, //各樓層up按鈕(頂層無),每1位代表1層,當相應位置1時表示該層up按鈕被按下

down, //各樓層down按鈕(底層無),每1位代表1層,當相應位置1時表示該層down按鈕被按下;

stop_r, //電梯內各層按鍵信息

up_r, //電梯外各層向上按鍵信息

down_r //電梯外各層向下按鍵信息

);

c. 電梯控制器模塊和指示模塊:該模塊根據各層按鈕被按下的情況,控制電梯運行,并設置指示燈。模塊定義如下:

module Lift_cONtrol(

keyclk, //處理按鍵時鐘

liftclk, //電梯運行控制時鐘

reset, //電梯復位按鈕,復位后電梯停在一樓;

stop_r, //電梯內各層按鍵信息

up_r, //電梯外各層向上按鍵信息

down_r, //電梯外各層向下按鍵信息

position, //當前樓層位置,每1位代表1層,當相應的位置1時表示電梯運行至該層;

stoplight, //內部各層按鈕指示燈,每1位代表1層,當相應位置1時表示指示該層指示燈亮;

uplight, //除頂層外各層外部按鈕指示燈,每1位代表1層,當相應位置1時表示該層up燈亮;

downlight, //除首層外各層外部按鈕指示燈,每1位代表1層,當相應的位置1時表示該層的down指示燈亮;

doorlight); //用于開門指示燈,為1表示開門,為0表示關門

d. 顯示模塊:該模塊用于譯碼顯示當前電梯所在樓層,模塊定義如下:

module Display(liftclk,position,disp);

2.2 模塊設計與實現

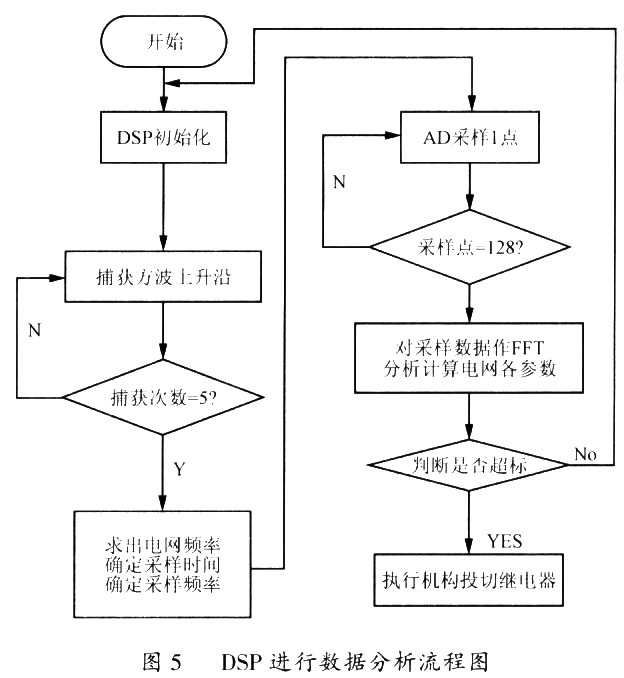

對于分頻器模塊、按鍵請求模塊、電梯控制器模塊和指示模塊和顯示模塊這四個模塊,電梯控制器模塊和指示模塊涉及到電梯各種運行情況的處理,其算法是最復雜的,也是最容易出錯的。本文采用使用有限狀態機來設計該模塊,具體的算法描述如下。

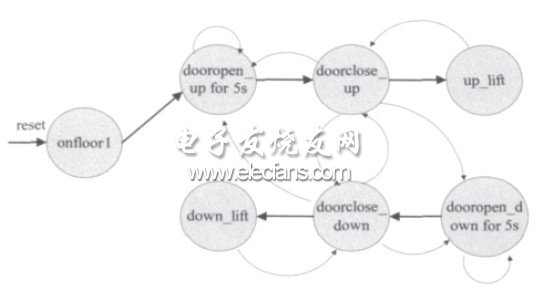

將電梯運行定義為7個狀態,具體的狀態定義如下:

S0:onfloor1,表示在樓層1;

S1:dooropen_up,上升過程中,電梯開門5s;

S2:doorclose_up,上升過程中,電梯關門;

S3:up_lift,表示電梯上升一層;

S4:dooropen_down,下降過程中,電梯開門5s;

S5:doorclose_down,下降過程中,電梯關門;

S6:down_lift,表示電梯下降一層。

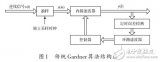

各狀態在滿足一定的條件下轉換,具體狀態轉換如圖2所示。

?

圖2 電梯控制器狀態轉換圖

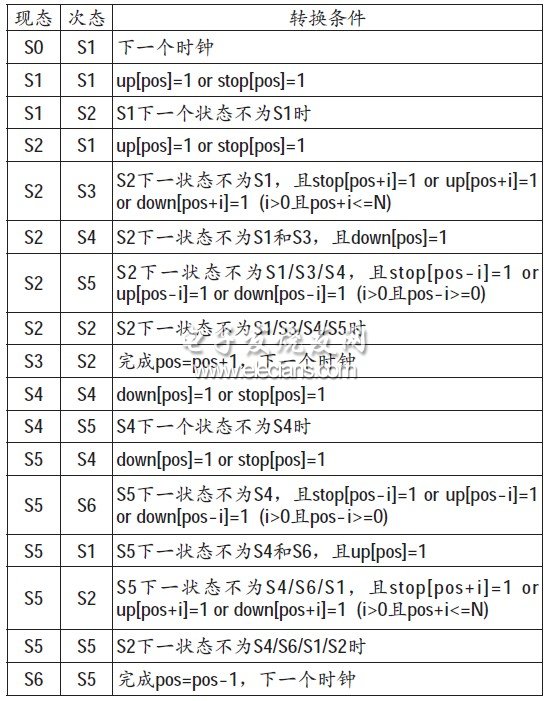

表1 電梯控制器狀態轉換條件

?

上表中, pos 表示當前樓層, up[pos ] 、down[pos]、stop[pos]分別表示當前樓層的向上、向下、和停止銨鈕的狀態。

顯然,上述算法并未對樓層數作限制,也就是說該算法適合于任意樓層的電梯控制器。

2.3 仿真驗證

本文根據上述算法,采用Verilog HDL語言在FPGA上實現了一個三層電梯控制器。對于實現來說,三層電梯或者多層電梯的控制器只是Verilog代碼數量的不同,其算法則完全是本文提出的算法,沒有區別。本文只所以實現了一個三層電梯控制器,是因為硬件開發環境的資源(包括按鈕的數量、指示燈的數量)僅滿足三層電梯控制器的驗證。

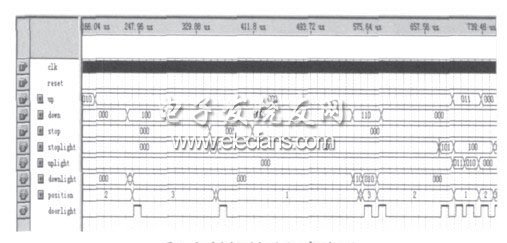

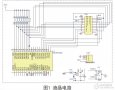

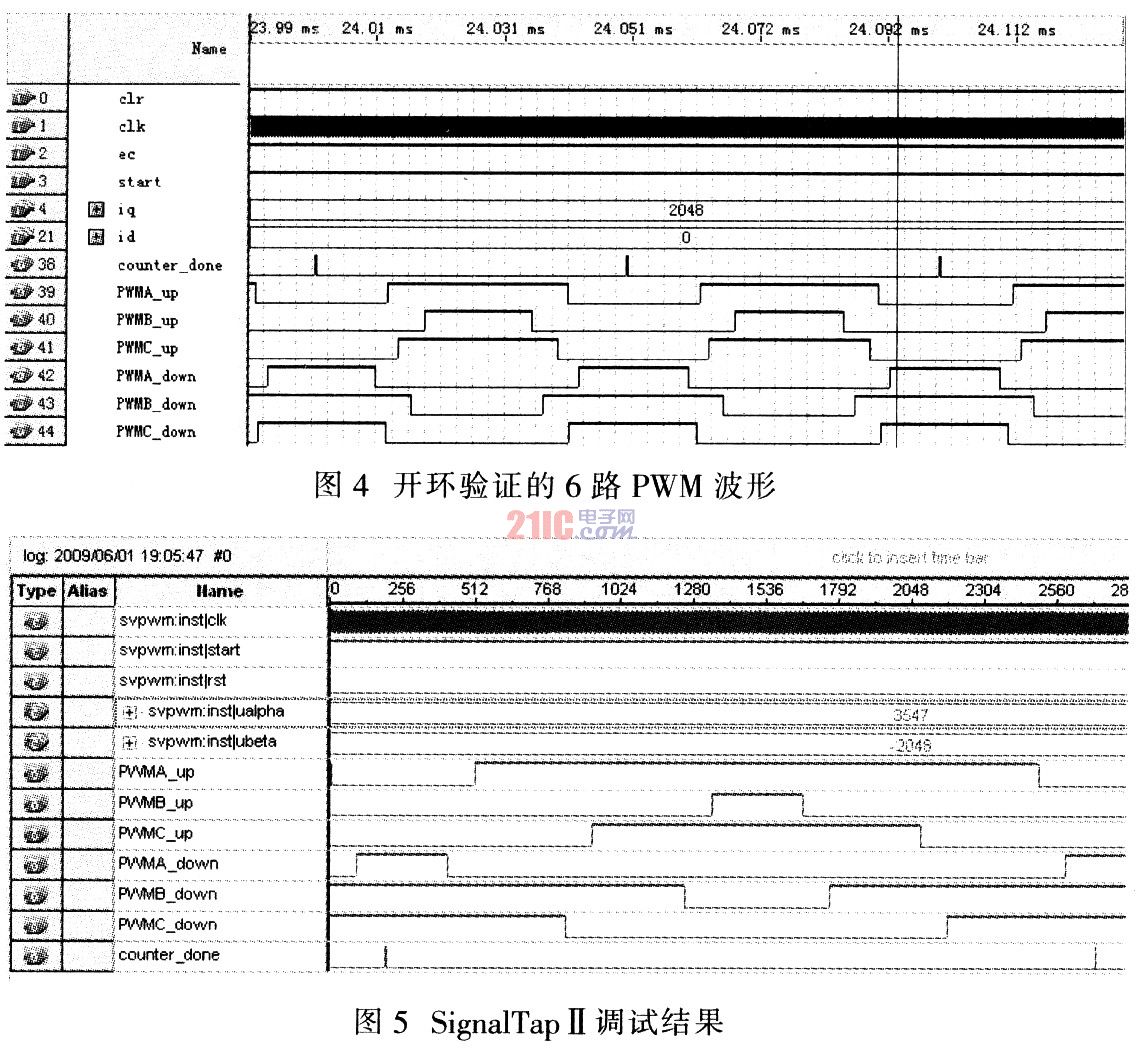

三層電梯控制器的仿真波形如圖3所示。

?

圖3 三層電梯控制器的仿真波形

仿真波形說明:電梯內外按鈕,當其值由0變為1即表示被按下。圖中,各層電梯間內外的銨鈕被按下是隨機發生的。

由仿真波形可以看出,電梯的運行符合設計要求。

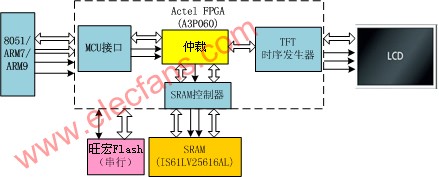

2.4 硬件驗證

本文的設計經引腳鎖定并下載到硬件開發環境中,經測試完全正確。

具體硬件開發環境為GW48-PK2實驗開發系統。

CLK選擇clk0,頻率可選擇為256Hz。

鍵1、2、3對應電梯內各層的按鈕;鍵4、5對應一二樓層電梯外的向上銨鈕;鍵6、7對應二三樓層電梯外的向下銨鈕;鍵8對應系統復位鍵;燈1、2、3指示電梯內各層的按鈕被按下;燈4、5指示一二樓層電梯外的向上銨鈕被按下;燈6、7指示二三樓層電梯外的向下銨鈕被按下;燈8指示開門。

電梯所在層數由數碼管1指示。

3 結論

本文的電梯控制器設計,結合了深圳信息職業技術學院的實際電梯的運行情況,易于學生理解和接受,對于工學結合的教學改革,是一個非常好的實踐項目。另外,本文提出的電梯控制器算法適合于任意樓層,并在FPGA開發環境中進行了驗證,具有很強的適應性和實用性。

電子發燒友App

電子發燒友App

評論