這是一個AVR DDS信號發(fā)生器V2.0新的實施 很明顯,對于原原理圖和固件完全歸功于它的原創(chuàng)者

2011-06-27 18:26:08 5327

5327 信號發(fā)生器又稱信號源或振蕩器,在生產(chǎn)實踐和科技領域中有著廣泛的應用。能夠產(chǎn)生多種波形,如三角波、鋸齒波、矩形波(含方波)、正弦波的電路被稱為函數(shù)信號發(fā)生器。函數(shù)信號發(fā)生器的實現(xiàn)方法通常是采用分立元件

2020-10-19 11:50:17 5295

5295

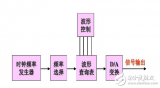

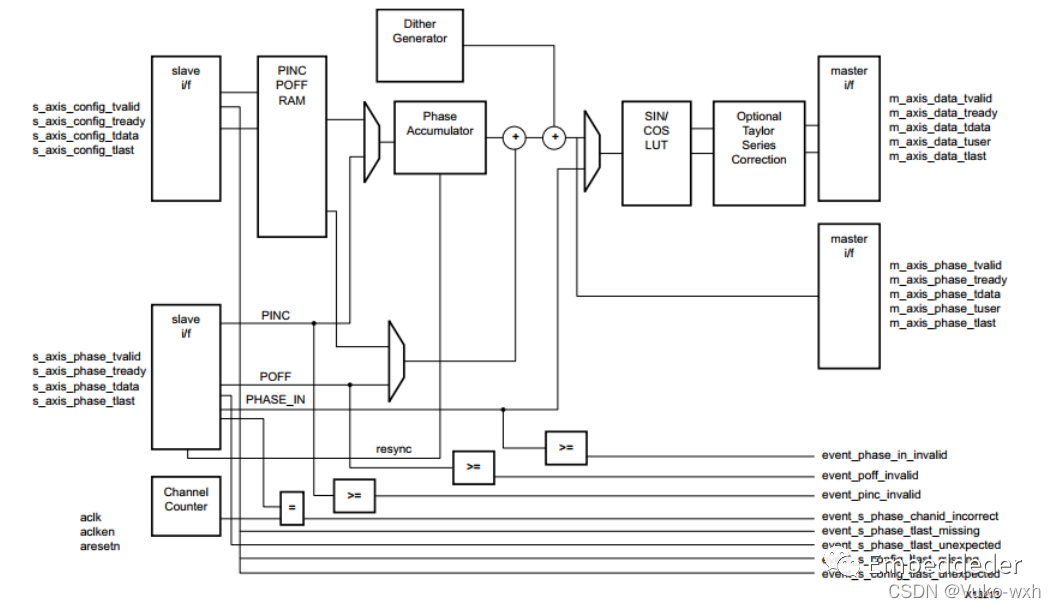

調(diào)用內(nèi)部鎖相環(huán)由輸入的12M時鐘得到120MHZ工作時鐘,驅(qū)動DDS控制模塊,輸出作為DAC的轉(zhuǎn)換時鐘。

2022-07-10 16:21:03 2525

2525 現(xiàn)在用到DDS芯片做個信號發(fā)生器,可是不知道用DDS產(chǎn)生的波形的幅度是怎么得到的,要是想改變波形的幅度該怎么做?求解答。

2014-04-15 23:06:36

單片機設計DDS信號發(fā)生器模塊制作資料描述

2015-07-10 15:13:13

`本專題匯集了四十種DDS信號發(fā)生器各部分資料,包括信號發(fā)生器原理,DDS芯片及應用,信號發(fā)生器電路圖及DDS信號發(fā)生器設計,為你免除大量自行搜索的時間,讓你深入了解DDS信號發(fā)生器。更多精彩資料:http://m.1cnz.cn/zhuanti/dds.html`

2015-06-23 14:02:38

DDS直接數(shù)字頻率合成器、信號發(fā)生器、函數(shù)發(fā)生器1.DDS直接數(shù)字頻率合成器、信號發(fā)生器、函數(shù)發(fā)生器他們之間有哪些異同?2.目前只發(fā)現(xiàn)ADI有相關的產(chǎn)品,國產(chǎn)有哪些品牌可以推薦3.如果要輸出的頻率和功率是實時可調(diào)的,用MCU控制DDS芯片是否可以實現(xiàn)?

2022-03-24 18:10:02

本設計以FPGA為控制核心,采用直接數(shù)字頻率合成(DDS)設計了一款信號可調(diào)的信號發(fā)生器,采用的FPGA是Altera公司研發(fā)的的Cyclnoe II系列,所選用的型號是EP4C6F17C8,外圍

2021-10-28 16:49:26

` 本帖最后由 明德?lián)P吳老師 于 2020-6-15 11:27 編輯

基于FPGA的DDS信號發(fā)生器設計信號發(fā)生器是一種能提供各種頻率、輸出電平的電信號的設備,又稱信號源或振蕩器。其在各種電信

2020-06-15 11:25:38

可以用數(shù)字化顯示或者直接設置。早期的高精度信號發(fā)生器為了得到較小的頻率步進,將鎖相環(huán)做得非常復雜,成本很高,體積和重量都很大。目前的中高端信號發(fā)生器采用了更先進的DDS頻率直接合成技術,具有頻率輸出

2016-02-23 14:52:52

Arlyb-DDS信號發(fā)生器 By Arlyb StudioDDS是直接數(shù)字式頻率合成器(Direct Digital Synthesizer)的英文縮寫。與傳統(tǒng)的頻率合成器相比,DDS具有低成本

2013-07-07 19:07:37

DAC模擬乘法器、DDS(頻率合成器)、信號發(fā)生器1.DAC模擬乘法器構成的混頻器是否可以和DDS(頻率合成器)、信號發(fā)生器一樣?可以生成任意目前波形?2.DDS(頻率合成器)、信號發(fā)生器它倆之間有存在哪些異同?

2022-03-24 17:24:37

我在用Protues 做DDS信號發(fā)生器,同步寄存器應該用什么器件啊?還有一個32位的加法器,應該怎么畫?該用什么芯片呢?

2012-05-03 16:59:38

基于FPGA的簡易DDS信號源設計設計方案背景信號發(fā)生器又稱信號源或振蕩器,在生產(chǎn)實踐和科技領域中有著廣泛的應用。能夠產(chǎn)生多種波形,如三角波、鋸齒波、矩形波(含方波)、正弦波的電路被稱為函數(shù)信號

2012-05-12 23:01:54

芯片的可編程性和實現(xiàn)方案易改動的特點,提出了一種基于FPGA和DDS技術的任意波形發(fā)生器設計方案。目前任意波形發(fā)生器的設計還在進行中。本文只給出實驗階段的三相正弦波的產(chǎn)生代碼和仿真波形,產(chǎn)生的并不是任意波形了。DDS設計要求:頻率分辨率

2015-05-30 10:50:36

`之前一直有網(wǎng)友反映我們的《FPGA自學筆記——設計與驗證》一書中雙通道DDS信號發(fā)生器做板級驗證有點麻煩,新手可能不適應,因為需要發(fā)送的指令比較多,使用串口調(diào)試助手不是很方便,因此小梅哥特意

2018-06-01 09:57:34

求大佬分享一款基于DDS器件AD9851的信號發(fā)生器設計方案

2021-04-12 06:35:26

現(xiàn)在很多信號發(fā)生器是基于 DDS 技術開發(fā)的。但是看其性能指標有些不明白的地方,不知道是怎么實現(xiàn)的?比如 采樣率是 500MSa/s, 輸出頻率 100MHz那么他是怎么做到最大頻率下不失真的呢?假如是基于 DDS的話,按照上面的指標,一個正弦周期是用5個點來描繪的。波形應該不會很好的才是。

2020-10-13 16:21:42

最近在做DDS信號發(fā)生器,請教一下大神有沒有能使發(fā)生器輸出的方波信號升降沿可調(diào)的

2020-06-24 10:16:48

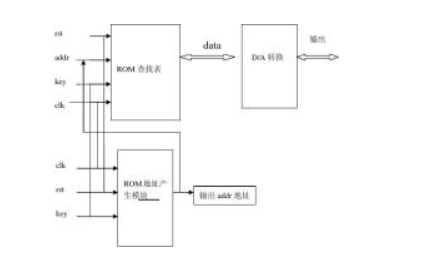

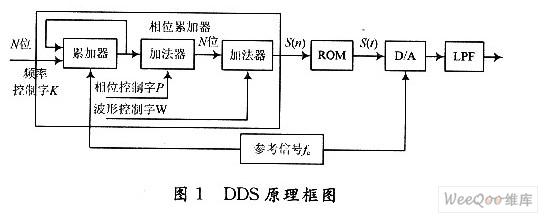

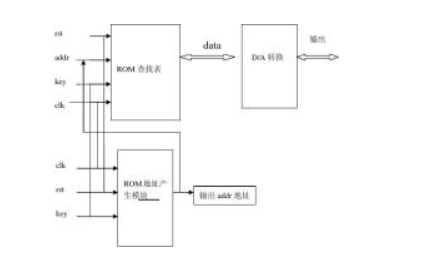

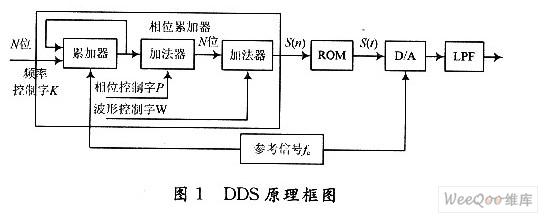

摘要:本設計基于DDS原理和FPGA技術按照順序存儲方式,將對正弦波、方波、三角波、鋸齒波四種波形的取樣數(shù)據(jù)依次全部存儲在ROM波形表里,通過外接設備撥扭開關和鍵盤控制所需波形信號的輸出,最終將波形

2019-06-21 07:10:53

DDS基本原理是什么?DDS的基本參數(shù)有哪些?基于DDS技術的任意波形發(fā)生器是怎樣設計的?

2021-04-30 07:19:15

最近在做基于DDS的信號發(fā)生器,MCU用的是STC12C5A60S2單片機,可以發(fā)生正弦波0~50Mhz內(nèi)都很穩(wěn)定,頻率可步進,但是不知道如何去產(chǎn)生一個占空比可控的方波,求大神指導代碼,用的DDS是AD9854模塊。

2016-08-05 21:26:44

信號發(fā)生器種類很多,按是否利用頻率合成技術來分,可分為非頻率合成式信號發(fā)生器與頻率合成式信號發(fā)生器。其中頻率合成式信號發(fā)生器的頻率準確度和穩(wěn)定度都很高,且頻率連續(xù)可調(diào),是信號發(fā)生器的發(fā)展方向。頻率

2019-09-26 06:45:26

求一個基于FPGA的DDS信號發(fā)生器設計,最好有DA模塊和相位累加器模塊的代碼。

2019-03-18 22:09:03

http://pan.baidu.com/s/1i3jPrCx

2015-11-17 20:03:28

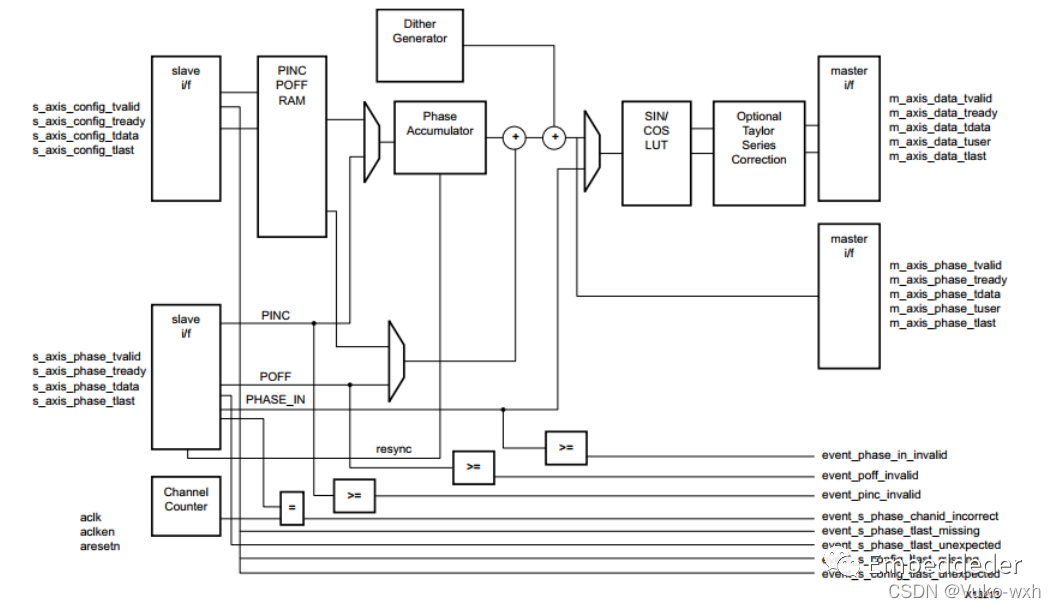

我畢業(yè)設計要做一個基于FPGA的IP核的DDS信號發(fā)生器,但是我不會用DDS的IP核,有沒有好人能發(fā)我一份資料如何用IP核的呀。我的瀏覽器下載不了網(wǎng)站上的資料,所以只能發(fā)帖求幫忙了。

2015-03-10 11:46:40

基于FPGA的雙路低頻信號發(fā)生器設計摘要 本設計是基于Altera公司的Cyclone II系列EP2C8Q208C8N芯片的雙路低頻信號發(fā)生器。系統(tǒng)應用FPGA內(nèi)部特有的可配置IP核和鎖相環(huán)等

2018-08-23 15:32:05

基于ALTERA實現(xiàn)的DDS信號發(fā)生器設計

2017-05-12 15:08:10

支持最高125 MSPS的更新速率。該DDS信號發(fā)生器采用STM32VET6作為主控制芯片,DDS芯片采用AD9708,外部接口支持手動按鍵、SD卡、USB接口等。電路主要有STM32最小系統(tǒng)和電源

2018-08-28 17:18:01

基于labview和fpga的信號發(fā)生器要求:【1】正弦波、方波、鋸齒波、三角波。【2】頻率、幅值、相位可調(diào),調(diào)節(jié)步進值:頻率0.1,幅值0.1,相位1;【3】頻率最高:20k;峰值最高:3.3

2022-01-18 07:35:42

,可分為音頻信號發(fā)生器、射頻信號發(fā)生器;依據(jù)內(nèi)部原理不同,可分為模擬型信號發(fā)生器、基于直接數(shù)字合成(DDS)技術的信號發(fā)生器;依據(jù)產(chǎn)生信號類型,可分為脈沖信號發(fā)生器,邏輯信號發(fā)生器以及通用...

2021-08-09 09:18:26

DDS電路的工作原理是什么如何利用FPGA和DDS技術實現(xiàn)正弦信號發(fā)生器的設計

2021-04-28 06:35:23

DDS的工作原理和基本結(jié)構基于FPGA的DDS信號發(fā)生器的設計如何建立頂層模塊?

2021-04-09 06:46:42

信號發(fā)生器又稱信號源或振蕩器,在生產(chǎn)實踐和科技領域中有 著廣泛的應用。能夠產(chǎn)生多種波形,如三角波、鋸齒波、矩形波(含方波)、正弦波的電路被稱為函數(shù)信號發(fā)生器。

2019-11-11 08:07:57

看了挺多文獻了,現(xiàn)在僅僅有一點VerilogHDL的知識,之前了解過一點FPGA的設計,但是還是有很多地方看不懂。想問一下DDS信號發(fā)生器和函數(shù)信號發(fā)生器的區(qū)別。

2020-02-19 21:25:01

本文在討論DDS的基礎上,介紹利用FPGA設計的基于DDS的信號發(fā)生器。

2021-05-06 09:54:10

怎么實現(xiàn)信號發(fā)生器系統(tǒng)的FPGA設計?

2021-09-30 06:35:31

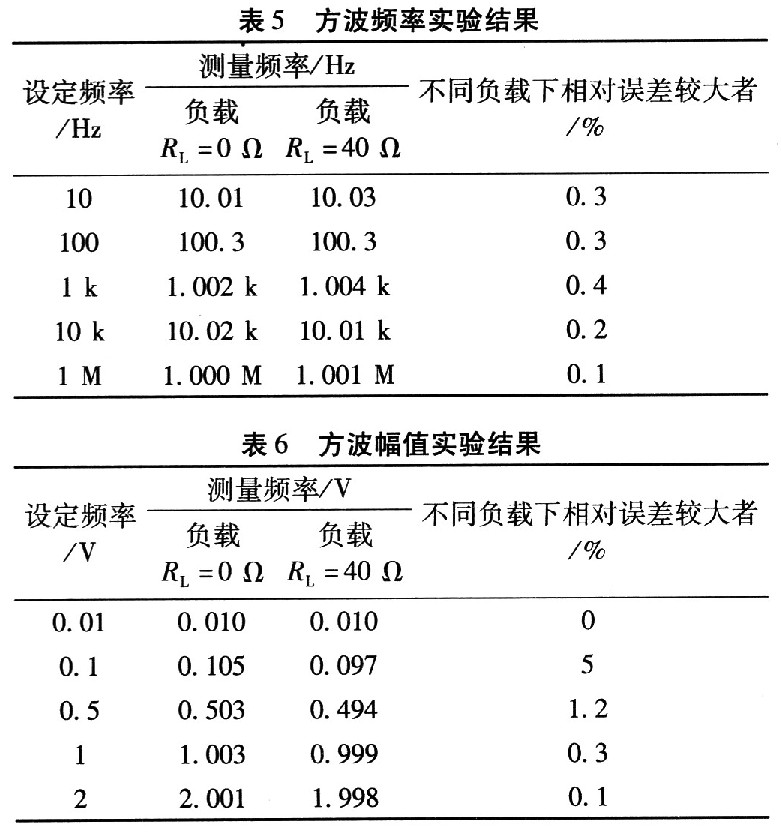

介紹了DDS的發(fā)展歷史及其兩種實現(xiàn)方法的特點,論述了DDS的基本原理,并提出一種基于FPGA的DDS信號發(fā)生器的設計方法,使DDS信號發(fā)生器具有調(diào)頻、調(diào)相的功能,最后對其性能進行了分析。實驗表明該系統(tǒng)具有設計合理、可靠性高、結(jié)構簡單等特點,具有很好的實用價值。

2021-05-11 06:58:58

本文介紹一種基于DDS器件AD9851的信號發(fā)生器設計方案。

2021-05-13 07:04:10

)。DDS是開環(huán)系統(tǒng),無反饋環(huán)節(jié),輸出響應速度快,頻率穩(wěn)定度高。因此直接數(shù)字頻率合成技術是目前頻率合成的主要技術之一。文中的主要內(nèi)容是采用FPGA結(jié)合虛擬儀器技術,進行DDS信號發(fā)生器的開發(fā)。

2019-09-29 08:08:12

本帖最后由 eehome 于 2013-1-5 10:06 編輯

有沒有什么專用

DDS芯片設計

信號發(fā)生器,可以產(chǎn)生三角波、鋸齒波、梯形波啊?大家?guī)兔ο胍幌耄檬裁葱酒媚兀?/div>

2012-11-23 10:25:18

DDS信號發(fā)生器采用直接數(shù)字頻率合成(Direct Digital Synthesis,簡稱DDS)技術,把信號發(fā)生器的頻率穩(wěn)定度、準確度提高到與基準頻率相同的水平,并且可以在很寬的頻率范圍內(nèi)進行

2021-08-04 06:09:37

本文提出了一種以直接數(shù)字頻率合成(DDS)技術為基礎的信號發(fā)生器的設計。采用單片機AT89C51 控制DDS 芯片AD9850 產(chǎn)生頻率可調(diào)的正弦信號,并通過低通濾波器得到純正的信號,最

2009-06-03 11:42:31 65

65 以混合信號單片機C8051F020 及DDS 芯片AD9834 為核心,采用直接數(shù)字合成(DDS)技術完成多功能高頻正弦信號發(fā)生器的設計。該正弦信號發(fā)生器可輸出可調(diào)頻穩(wěn)定正弦信號,頻率最高

2009-08-10 15:27:03 107

107 本文介紹了由AVR 單片機ATmega8 控制DDS 芯片AD9832 開發(fā)的一種高頻率精度信號發(fā)生器,著重討論了DDS 技術的基本工作原理、特點,以及ATmega8 控制系統(tǒng)的硬件結(jié)構和基于BASCOM-AVR

2009-09-08 10:11:03 60

60 以混合信號單片機C8051F020 及DDS 芯片AD9834 為核心,采用直接數(shù)字合成(DDS)技術完成多功能高頻正弦信號發(fā)生器的設計。該正弦信號發(fā)生器可輸出可調(diào)頻穩(wěn)定正弦信號,頻率最高

2009-12-18 15:32:15 111

111 基于FPGA的DDS信號源設計與實現(xiàn)

利用DDS和 FPGA 技術設計一種信號發(fā)生器.介紹了該信號發(fā)生器的工作原理、 設計思路及實現(xiàn)方法.在 FPGA 器件上實現(xiàn)了基于 DDS技

2010-02-11 08:48:05 223

223 在直接數(shù)字頻率合成器(DDS)的基礎上,利用現(xiàn)場可編程門陣列(FPGA)設計一款數(shù)字移相正弦信號發(fā)生器,并通過Altera公司的DE2開發(fā)板來驗證.在輸入環(huán)節(jié)加入一個數(shù)據(jù)鎖存器,用“

2010-10-20 16:37:02 129

129 提出了一種基于DDS (Direct Digital Synthesize) AD9850的頻率、相位、幅值均可調(diào)節(jié)的正弦信號發(fā)生器。該正弦信號發(fā)生器采用AT89S52單片機為控制器,D/A轉(zhuǎn)換器TLC5615與乘法器AD534相結(jié)合,實

2010-12-16 16:14:38 0

0 基于DDS的波形發(fā)生器設計

0 引 言

隨著信息技術的發(fā)展及測試對象不斷豐富,現(xiàn)代電子系統(tǒng)對波形發(fā)生器也提出了更高的要求。傳統(tǒng)的模

2010-01-27 10:49:51 1601

1601 基于DDS技術的信號發(fā)生器研究與實現(xiàn)策略

研究了一種基于DDS芯片AD9850和單片機AT89S52的信號發(fā)生器系統(tǒng),能夠產(chǎn)生正弦波、三角波和方波三種波形。該系統(tǒng)頻率、幅值

2010-04-23 11:41:56 2219

2219

本文主要介紹的是微型的DDS信號發(fā)生器的原理和設計,整個系統(tǒng)是以AT89S51為控制,外部ROM為存儲,AD9850芯片和溫度補償晶體振蕩器構成的微型DDS信號發(fā)生器,采用DM-162點陣液晶顯示模塊

2011-05-05 15:55:36 121

121 文中提出一種基于FPGA的DDS信號發(fā)生器。信號發(fā)生電路采用直接數(shù)字頻率合成技術,即DDS(Direct Digital Frequency Synth-esis)。它是以全數(shù)字技術,從相位概念出發(fā),直接合成所需波形的一種新的

2011-07-16 10:24:22 1678

1678

本設計基于DDS原理和FPGA技術按照順序存儲方式,將對正弦波、方波、三角波、鋸齒波四種波形的取樣數(shù)據(jù)依次全部存儲在ROM波形表里,通過外接設備撥扭開關和鍵盤控制所需波形信號的

2012-07-12 14:23:15 0

0 將虛擬儀器技術同FPGA技術結(jié)合,設計了一個頻率可控的DDS任意波形信號發(fā)生器。在闡述直接數(shù)字頻率合成技術的工作原理、電路構成的基礎上,分別介紹了上位機虛擬儀器監(jiān)控面板的功

2012-08-13 17:24:27 93

93 首先介紹了采用直接數(shù)字頻率合成(DDS)技術的正弦信號發(fā)生器的基本原理和采用FPGA實現(xiàn)DDS信號發(fā)生器的基本方法,然后結(jié)合DDS的原理分析了采用DDS方法實現(xiàn)的正弦信號發(fā)生器的優(yōu)缺點

2012-11-26 16:23:32 49

49 設計采用Altera公司CycloneII系列EP2C5Q208作為核心器件,采用直接數(shù)字頻率合成技術實現(xiàn)了一個頻率、相位可控的基本信號發(fā)生器。該信號發(fā)生器可以產(chǎn)生正弦波、方波、三角波和鋸齒波四種波形。仿真及硬件驗證的結(jié)果表明,該信號發(fā)生器精度高,抗干擾性好,此設計方案具有一定的實用性。

2013-01-22 14:45:33 472

472 為了提高數(shù)字調(diào)制信號發(fā)生器的頻率準確度和穩(wěn)定度,并使其相關技術參數(shù)靈活可調(diào),提出了基于FPGA和DDS技術的數(shù)字調(diào)制信號發(fā)生器設計方法。利用Matlab/Simulink、DSP Builder、QuartusⅡ 3個

2013-04-27 16:50:59 183

183 本專題匯集了四十種DDS信號發(fā)生器各部分資料,包括信號發(fā)生器原理,DDS芯片及應用,信號發(fā)生器電路圖及DDS信號發(fā)生器設計,為你免除大量自行搜索的時間,讓你深入了解DDS信號發(fā)生器。

2015-06-23 10:41:36

2015-08-24 19:06:58 37

37 基于FPGA的正弦信號發(fā)生器的 技術論文

2015-10-30 10:39:05 20

20 給予DDS可編程的波形發(fā)生器,對三個不同頻段的波形信號進行分析

2015-11-02 17:22:44 3

3 基于ARM與DDS的高精度正弦信號發(fā)生器設計

2016-01-04 15:02:29 0

0 基于dds函數(shù)信號發(fā)生器,用單片機及dds實現(xiàn)正玄波,三角波,矩形波的產(chǎn)生

2016-01-11 14:55:21 19

19 詳細介紹了直接數(shù)字頻率合成器(DDS)的工作原理、基本結(jié)構。在參考DDS 相關文獻的基礎上,提出了符合結(jié)構的DDS 設計方案,利用DDS 技術設計了一種高頻率精度的多波形信號發(fā)生器,此設計基于可編程邏輯器件FPGA,采用Max+PlusⅡ開發(fā)平臺,由Verilog_HDL 編程實現(xiàn)。

2016-11-22 14:35:13 0

0 DDS芯片AD9851在頻率合成信號發(fā)生器中的應用

2016-12-17 21:16:26 46

46 電子發(fā)燒友網(wǎng)站提供《iBoard教程之(dds信號發(fā)生器)任意波發(fā)生器硬件電路分析.pdf》資料免費下載

2017-10-29 09:25:05 0

0 FPGA和51單片機信號發(fā)生器設計

2017-10-31 09:15:37 22

22 DDS( Direct digital synthesis)直接數(shù)字頻率合成是從相位概念出發(fā)直接合成所需波形的一種新的顏率合成技術,它將先進的數(shù)字處理理論與方法引入信號合成領域。 DDS信號發(fā)生器

2017-11-03 09:56:55 10947

10947 介紹了用數(shù)字方式實現(xiàn)頻率合成技術的基本原理和 DDS 芯片 AD9854 的內(nèi)部結(jié)構及工作模式。設計了一種采用單片機控制 AD9854 為核心的信號發(fā)生器, 它具有輸出信號波形種類多、精度高、可程控

2017-11-16 14:49:41 45

45 基于運放的信號發(fā)生器精度低且穩(wěn)定性和可調(diào)節(jié)性差,而基于DDS的信號發(fā)生器則成本高、電路復雜。為此提出了基于FPGA+PWM的多路信號發(fā)生器設計方法。該方法硬件上無需DAC與多路模擬開關,由FPGA產(chǎn)生調(diào)制輸出波形信號所需的PWM脈沖波,經(jīng)二階低通濾波和放大電路后即可得到所需波形信號。

2017-11-18 09:42:01 6332

6332

將虛擬儀器技術同FPGA技術結(jié)合,設計了一個頻率可控的DDS任意波形信號發(fā)生器。在闡述直接數(shù)字頻率合成技術的工作原理、電路構成的基礎上,分別介紹了上位機虛擬儀器監(jiān)控面板的功能和結(jié)構,以及實現(xiàn)DDS

2017-12-04 11:40:09 33

33 DDS信號發(fā)生器采用直接數(shù)字頻率合成(DirectDigitalSynthesis,簡稱DDS)技術,把信號發(fā)生器的頻率穩(wěn)定度、準確度提高到與基準頻率相同的水平,并且可以在很寬的頻率范圍內(nèi)進行精細的頻率調(diào)節(jié)。采用這種方法設計的信號源可工作于調(diào)制狀態(tài),可對輸出電平進行調(diào)節(jié),也可輸出各種波形。

2018-01-08 10:26:51 18741

18741

本文對DDS函數(shù)信號發(fā)生器的結(jié)構原理、優(yōu)點、主要功能特性、主要技術指標四個方面進行了簡單的介紹。

2018-01-08 10:41:50 13728

13728

本文檔內(nèi)容介紹了基于fpga實現(xiàn)信號發(fā)生器,供參考

2018-04-20 15:23:35 65

65 某型導彈測試設備電路板檢測儀主要完成該測試設備的電路板的故障檢測。該檢測系統(tǒng)要求激勵信號產(chǎn)生電路體積小,配置靈活,且精度高、轉(zhuǎn)換速度快。基于FPGA的DDS信號發(fā)生器較傳統(tǒng)信號發(fā)生器能夠更好地滿足檢測儀要求。

2019-01-10 09:15:00 4025

4025

論述了DDS的基本原理,給出了利用FPGA實現(xiàn)基于DDS的2ASK/2FSK信號發(fā)生器的設計方法,重點介紹了其原理和電路,最后給出了基于.FPGA設計的實驗結(jié)果.

2021-03-24 09:12:00 19

19 為了對直接數(shù)字頻率合成技術進行直觀的研究,同時滿足對信號源可配置性及靈活操作的目的,采用了基于嵌入式系統(tǒng)與FPGA為從機,以PC機作為虛擬儀器操作界面的方法設計了直接數(shù)字頻率合成信號發(fā)生器,系統(tǒng)

2021-05-11 10:27:22 43

43 基于FPGA和DAC設計的dds發(fā)生器(普德新星電源技術有限公司的LoGo)-該文檔為基于FPGA和DAC設計的dds發(fā)生器總結(jié)文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-09-16 12:09:10 40

40 DDS信號發(fā)生器采用直接數(shù)字頻率合成(Direct Digital Synthesis,簡稱DDS)技術,把信號發(fā)生器的頻率穩(wěn)定度、準確度提高到與基準頻率相同的水平,并且可以在很寬的頻率范圍內(nèi)進行

2021-12-02 18:51:18 29

29 電子發(fā)燒友網(wǎng)站提供《基于AD9833的DDS單通道三信號發(fā)生器.zip》資料免費下載

2022-08-09 09:17:44 11

11 DDS信號發(fā)生器采用直接數(shù)字頻率合成(Direct Digital Synthesis,簡稱DDS)技術,把信號發(fā)生器的頻率穩(wěn)定度、準確度提高到與基準頻率相同的水平,并且可以在很寬的頻率范圍內(nèi)進行精細的頻率調(diào)節(jié)。采用這種方法設計的信號源可工作于調(diào)制狀態(tài),可對輸出電平進行調(diào)節(jié),也可輸出各種波形。

2022-09-01 15:21:32 1969

1969 本設計以FPGA為控制核心,采用直接數(shù)字頻率合成(DDS)設計了一款信號可調(diào)的信號發(fā)生器,采用的FPGA是Altera公司研發(fā)的的Cyclnoe II系列,所選用的型號是EP4C6F17C8,外圍

2022-12-22 11:08:05 5

5 本文是本系列的第六篇,本文主要介紹FPGA常用運算模塊-DDS信號發(fā)生器,xilinx提供了相關的IP以便于用戶進行開發(fā)使用。

2023-05-24 10:37:18 3733

3733

電子發(fā)燒友App

電子發(fā)燒友App

評論