在眾多的調制方式中,連續相位調制信號(CPM 信號)具有恒包絡特性,它用于承載信息的相位軌跡連續變化,因此該類信號擁有較高的帶寬效率。基于CPM信號的恒包絡、帶寬緊湊和能量利用率高等優點,近幾年來,它受到廣泛的研究與應用。文中分析了二進制,部分響應L=2 的連續相位調制方式,提出了一種該調制方式下解調器的FPGA 設計方法,并運用VHDL 硬件描述語言實現。

1 CPM 的基本原理

連續相位調制信號可以用式(1)表示:

?

式(1)中, b E 表示信號的碼元能量,T 是碼元間隔,

?

即表示信號幅度。c f 是載波頻率,φ (t, I )是帶有傳輸信息的信號相位函數,其中I 表示發生的符號序列。φ (t, I )的表達式如下:

?

其中n I 是M (M = 2,4,8,16……) 進制的符號信息,取值為{±1,±3,……,±(M -1)}。文中M 為二進制調制, n I 的取值為+1、-1。h 是調制指數,g(t)是成形脈沖函數。脈沖函數g(t)采用升余弦脈沖RC:

?

式(3)中, L 又稱為關聯長度。

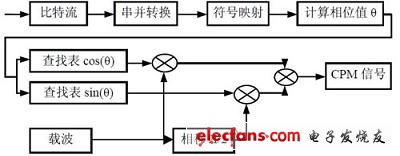

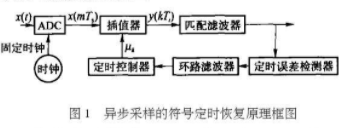

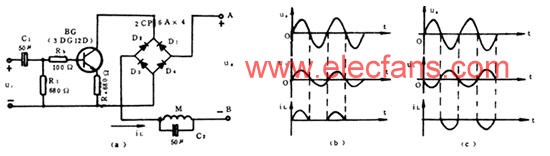

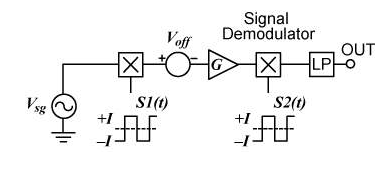

根據式(2)計算CPM 信號的基帶相位,根據相位計算基帶信號的I/Q 兩路,之后使用兩路信號相加就可以得到調制后的CPM 信號,見圖1。

?

圖1 CPM 信號調制

2 CPM 解調模塊的原理及其實現

2.1 解調器實現原理

對CPM 信號的接收、解調,常采取的步驟為:解調-最大似然序列估計-Viterbi 譯碼-判決。首先將接收到的復包絡信號分為I,Q兩路,下變頻為基帶信號,分別與cos(ψ (t, a))和sin(ψ (t, a))相關后相加,從而得到節點的度量值。對于t時刻每個狀態,可以根據其輸入值的不同,計算來自前一級節點的兩條路徑的路徑度量,并分別加上前一級節點的節點度量,然后從中選擇一個最小的度量值作為節點度量,并存儲前一級節點的信息。

2.2 解調器實現框圖

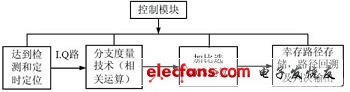

這里仿真采用二進制2RC 的調制方式,根據Viterbi 譯碼方式可知,調制信號共有8 個狀態,將這些狀態分別編碼為000,001,010,011,100,101,110,111。輸入數據與狀態間轉移關系見表1。筆者在設計中將其分為四個模塊:分支度量模塊、加比選模塊、回溯模塊和控制模塊。其結構設計如圖2 所示。

?

圖2 解調過程

(1)分支度量模塊

此模塊根據輸入數據計算分支度量值。在FPGA設計中,預先將每種基準狀態抽樣時刻的值存入STD 寄存器中,在計算分支度量時通過查表得到基準狀態的值。將輸入I,Q 兩路數據進行串/并轉換,得到一個碼元持續時間內的調制信號后,與每種基準狀態的抽樣值相乘并相加,從而得到I,Q 兩路的路徑度量值。最后將I,Q 兩路度量值相加,便可以得到各狀態的分支度量值。

(2)加比選ACS 模塊

此模塊分為兩部分:①計算路徑度量值;②選擇當前時刻最佳路徑。當前狀態的路徑度量值為該狀態下所有可能的路徑度量值中的最大值。最佳路徑為最大路徑度量值對應的上一狀態。在設計中采用確定CPM 調制的起始狀態的方法。復位時將起始狀態的路徑度量值賦值為0;將其他狀態的路徑度量值賦值為一個較小的負數。采用這種方式有效避免解調時起始狀態的不確定性。

CPM 的解調在一定的譯碼數量后,路徑度量值的存儲器便會飽和溢出。該設計采用一種簡單方法防止溢出:每次路徑度量值計算完成后,判斷其最大值,如果最大值超過某一確定的正值,則所有的路徑度量值減去一個正值。再判斷是否有度量值小于一個確定的負數,如果有,則將其值重新賦值為一個較小的負數。仿真中,證明了這種方法的可行性。

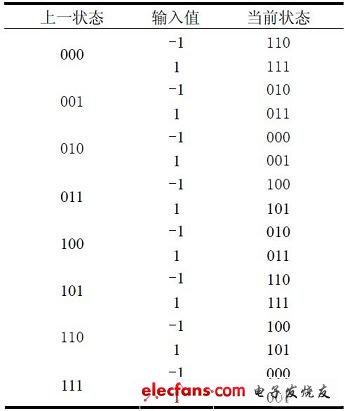

表1 輸入數據與狀態間轉移關系

?

(3)回溯模塊

此模塊包括幸存路徑存儲和判決輸出。在模塊中比較當前時刻各狀態的路徑度量值,求得最大路徑度量值,以及對應的當前狀態。從表1 可知,狀態的最低位可以表現上一時刻的輸入值,最低位為0 時,表示上一時刻的輸入碼字為-1;最低位為1 時表示上一時刻的輸入碼字為1。

3 硬件實現、時序仿真和性能

這里選擇的FPGA 是Xilinx 公司的Virtex5 系列的XC5VSX95T 芯片,設計軟件為ISE, Synplify, Modelsim,Matlab,設計語言采用VHDL 硬件描述語言。

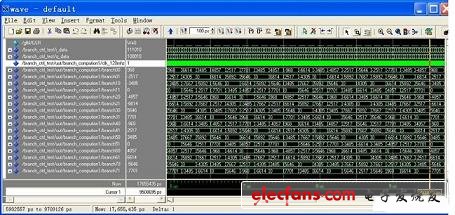

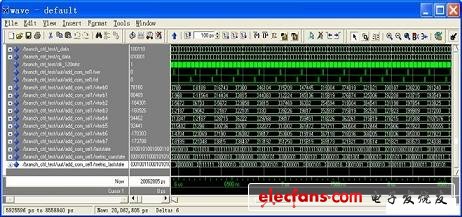

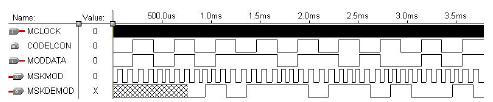

仿真中選擇二進制,關聯長度L 取2,升余弦脈沖的調制方式。仿真中波特率為5 MHz, 采用8 倍采樣,系統時鐘為120 MHz。假設輸入到調制器的雙極性比特流為{ } n b :1,1,1,-1,1,1,-1,-1,1,1,1,-1,1,1,-1,1……分支度量仿真結果如圖3 所示。

?

圖3 分支度量仿真結果

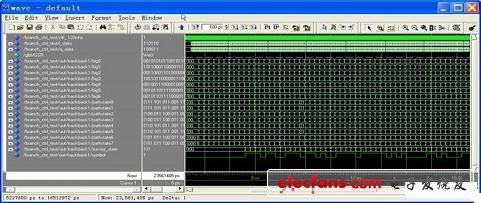

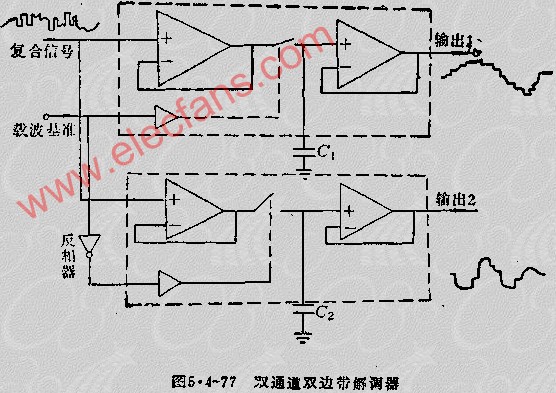

加比選模塊仿真結果如圖4 所示。

?

圖4 加比選模塊仿真結果

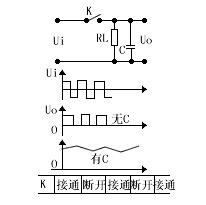

幸存路徑存儲和判決輸出模塊仿真結果如圖5 所示。

?

圖5 幸存路徑存儲和判決輸出模塊仿真結果

譯碼碼字:1,1,1,-1,1,1,-1,-1,1,1,1,-1,1,1,-1,1……當調制信號不加高斯白噪聲時,實現了誤碼率為0 的解調。仿真結果表明這里所設計的性能達到設計的要求。

4 結語

文中主要設計了該二進制2RC CPM 信號基于FPGA 的解調器。該方法針對Viterb 譯碼方法,提出了一種新的防止路徑度量值溢出方法。該設計的優點是:幸存路徑存儲器中存入的只是路徑信息,不需要存儲路徑度量值,節省了存儲空間;當譯碼輸出時只需要讀出最大路徑度量值的狀態所對應的幸存路徑存儲單元的最低位狀態值,提高了譯碼速度。該方法有效地防止路徑度量值溢出。

電子發燒友App

電子發燒友App

評論