眾所周知,串口,是嵌入式人員最熟悉的東西,非常方便,上到PC(現在是USB轉串口),下到MCU51等等,都有,但是,現在的FPGA/CPLD等,卻獨獨沒有,用JTAG代替下載固件.

本身來說,JTAG沒什么,然而確讓開發人員增加了成本,成本不僅僅只是物料成本,而且還包括入門成本,因為沒有JTAG下載工具,可能放棄了使用這顆FPGA.

這個里面,入門成本是最高的,因為一個FPGA下載線便宜的可能只有幾十元,但卻讓多少開發人員的入門成本增加到難以進入,因為還要去買,有一個心里障礙等等.

本人也熟悉FPGA/CPLD之類的,卻很少用,為什么,經常因為找不到了JTAG之類的東西,那就用MCU51算了,因為它太方便了.

任何一個產品,必需要降低它的入門成本,只有這樣,才能獲得大量的客戶,才能很好的推廣,這類的例子很多,比如STC的MCU51,因為ISP只需要串口下載調試,獲得巨大的成功,ARM類加一個串口的bootloader,也獲得大量普及.

相反,S3C2440之類的,bootloader卻需要jtag下載,不僅僅給開發帶來很多問題,而且給生產也帶來了很多問題,所以手機方案MTK/展迅之類的,都是采用串口升級,非常方便.

本人親身的感受是,3年前推出P1200手持機,集RFID/條碼功能于一身,卻碰到了推廣難問題,客戶無從下手,去年,推出旋風001手機開發平臺,采用java開發,讓客戶非常容易入門,并且把旋風001手機開發平臺的價格降低很低,結果導致很多客戶進來,他們入門了之后,都轉向尋求P1220(P1200升級版),于是P1220的市場極大的打開了.

FPGA/CPLD等完全可以集成一個串口下載調試的功能,IDE也專門留一個,這樣讓FPGA/CPLD跟MCU51一樣開發方便,我相信這樣做,起碼可以大大降低客戶的入門成本.

?

FPGA/CPLD等為什么不能用串口下載?

- FPGA(591969)

- cpld(168088)

相關推薦

CPLD/FPGA有哪些設計工具?

它們的基本設計方法是借助于 EDA 設計軟件,用原理圖、狀態機和硬件描述語言等方法,生成相應的目標文件,最后用編程器或下載電纜,由 CPLD/FPGA 目標器件實現。 生產 CPLD/FPGA

2019-03-04 14:10:13

FPGA/CPLD同步設計若干問題淺析

FPGA CPLD同步設計若干問題淺析摘要:針對FPGA/CPLD同步設計過程中一些容易被忽視的問題進行了研究,分析了問題產生的原因、對可靠性的影響,并給出了解決方案。關鍵詞:FPGA/CPLD

2009-04-21 16:42:01

FPGA串口調試不能正常接收

FPGA自己寫了一個串口程序,串口助手能一個8位自己發送,但是在串口中發一連串數據時,不能正常接收,誰能提供一個完好的,經過驗證的FPGA串口程序!謝謝,我的郵箱是feixiangzhf@[url=]@163.com[/url]

2019-02-14 06:35:20

FPGA與CPLD怎么區分

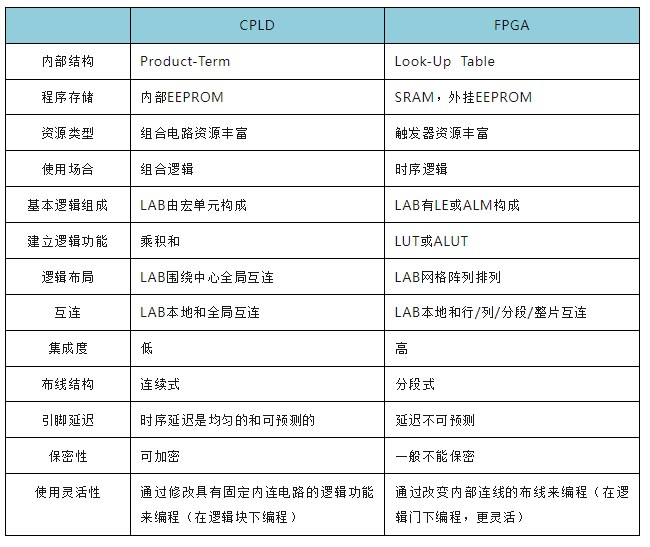

或ACEX1K系列等。盡管FPGA和CPLD都是可編程ASIC器件,有很多共同特點,但由于CPLD和FPGA結構上的差異,具有各自的特點:

2019-07-01 07:36:55

FPGA與CPLD的區別

FPGA與CPLD的區別

盡管很多人聽說過CPLD,但是關于CPLD與FPGA之間的區別,了解的人可能不是很多。雖然FPGA與CPLD都是“可反復編程的邏輯器件”,但是在技術上卻有一些差異。簡單

2011-09-27 09:49:48

FPGA與CPLD的區別

FPGA與CPLD(特權同學版權所有)本文節選自特權同學的圖書《FPGA設計實戰演練(邏輯篇)》(特權同學版權所有)配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt

2019-02-21 06:19:27

FPGA與CPLD的區別

可以很快進入市場。許多設計人員已經感受到CPLD容易使用、時序可預測和速度高等優點,然而,在過去由于受到CPLD密度的限制,他們只好轉向FPGA和ASIC。現在,設計人員可以體會到密度高達數十萬門

2012-10-26 08:10:36

FPGA與CPLD的概念及基本使用和區別

的主要區別1、邏輯結構不同 CPLD:類似 PAL、GAL,擁有豐富的組合邏輯電路資源。 FPGA:類似門陣列,擁有豐富的觸發器、存儲器資源;CPU、DSP等IP核。2、集成度不同 CPLD:500

2020-08-28 15:41:47

FPGA實戰演練邏輯篇3:FPGA與CPLD

FPGA與CPLD(特權同學版權所有)本文節選自特權同學的圖書《FPGA設計實戰演練(邏輯篇)》(特權同學版權所有)配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt

2015-03-12 13:54:42

cpld與flash配置fpga

用vhdl實現cpld配置fpga,配置成功后在usermode下設置一個重新配置信號,當信號有效時對fpga進行重新配置;fpga配置程序放在flash內;現在遇到的問題是,上電cpld能夠正常配置fpga并且進入usermode ,但是加上重新配置語句過后就不能成功配置fpga,求高人指點~

2013-01-17 22:35:39

Altera FPGA/CPLD經典教材

Altera FPGA/CPLD設計與Verilog數字系統設計教程從網上找到了一些Altera FPGA/CPLD經典教材,包含夏宇聞老師的Verilog數字系統設計教程(第2版)Altera FPGA/CPLD設計與Verilog數字系統設計教程

2014-02-17 09:22:18

MES50HP——FPGA與CPLD的下載與固化

1. FPGA&CPLD 的下載

(1)生成位流文件(.sbit)后,可以把.sbit 文件下載到 FPGA 或 CPLD 中,首先將 JTAG下載器與 PCB 板連接并上

2023-06-26 10:52:38

STM32F103RC程序燒錄為何不能用485工具或者串口?而只能用專門的下載軟件J-LINK或者其他下載軟件

STM32F103RC程序燒錄為何不能用485工具或者串口?而只能用專門的下載軟件J-LINK或者其他下載軟件?誰能詳細說下,謝謝

2018-06-26 18:02:49

XILINX FPGA/CPLD ISE詳細下載教程

XILINX FPGA/CPLD ISE下載教程 第一章 XILINX FPGA/CPLD ISE下載教程——下載.bit文件第二章 XILINX FPGA/CPLD ISE下載教程——燒錄Flash 圖文詳細資料!

2019-08-15 00:32:31

[推薦]FPGA/CPLD開發板及下載工具

XILINX(spartan,virtex系列等)altrea(max,cyclone系列等)cpld/fpga芯片,全型號開發板及開發套件。并可提供ADI,TI的DSP,FREESCALE單片機等

2009-05-06 09:48:25

[推薦]FPGA/CPLD開飯套件及芯片

XILINX(spartan,virtex系列等)altrea(max,cyclone系列等)cpld/fpga芯片,全型號開發板及開發套件。并可提供ADI,TI的DSP,FREESCALE單片機等

2009-06-19 14:25:08

multisim12能不能進行FPGA/CPLD的VHDL仿真??

如題,multisim12能不能進行FPGA/CPLD的VHDL仿真??各位大神,multisim12到底能不能進行VHDL的仿真呢?看上multisim的直觀,可惜好像不能使用里面的FPGA器件。。各種憂傷啊。。。。。求助。。。

2013-09-22 17:09:04

《FPGA 和 CPLD入門教程》

本帖最后由 nilwade 于 2014-5-11 20:47 編輯

之前剛學FPGA時在網上下載的一個教程,該教程定位于FPGA/CPLD的快速入門,適合初學者:“以ALTERA公司的芯片

2014-05-11 20:44:00

【下載】《CPLD/FPGA的開發與應用》

與數字信號處理等領域中的應用。本書內容新穎目錄· · · · · ·第1章 可編程ASIC與EDA技術第2章 Xilinx CPLD系列器件第3章 Xilinx FPGA系列器件第4章 CPLD/FPGA

2018-03-29 17:11:59

【招聘】聘兼職FPGA,CPLD,ASIC等相關講師

本公司招FPGA,CPLD,ASIC等相關兼職講師,短期技術培訓,要求有實際項目經驗,兩年以上項目經歷,表達力強,有親和力,日薪千可日結 ,可只在北京,周末。有意者請聯系QQ:***soft-xiang@foxmail.com簡歷主題請寫: 課程名+學歷+性別+姓名+年齡+聯系方式

2012-12-03 17:18:45

為什么STM32F103RC不能用485工具或者串口燒錄程序?

STM32F103RC程序燒錄為何不能用485工具或者串口?而只能用專門的下載軟件J-LINK或者其他下載軟件

2018-09-10 09:50:37

關于CPLD串口的問題,誰能幫我看下為什么

我用特權同學的CPLD做的串口自收發程序,不能向其發送連續的兩個字符,只能一次發送一個。如果發送兩個,則后面的字符會丟掉。例如,我發送1可以,發送11就亂碼了,同樣a可以,aa就亂碼了。這是為什么啊

2015-03-04 15:08:41

如何利用CPLD/FPGA設計多功能分頻器?

分頻器在CPLD/FPGA設計中使用頻率比較高,盡管目前大部分設計中采用芯片廠家集成的鎖相環資源 ,但是對于要求奇數倍分頻(如3、5等)、小數倍(如2.5、3.5等)分頻、占空比50%的應用場合卻往往不能滿足要求。利用CPLD/FPGA設計多功能分頻器,我們具體該怎么做呢?

2019-08-12 07:50:25

如何通過處理機用CPLD和Flash實現FPGA配置文件的下載更新?

從外部存儲器將FPGA配置文件下載更新的方式有哪幾種?如何用CPLD和Flash實現FPGA配置?

2021-04-08 06:07:22

常用的FPGA/CPLD設計思想與技巧有哪些?

本文討論的四種常用FPGA/CPLD設計思想與技巧:乒乓操作、串并轉換、流水線操作、數據接口同步化,都是FPGA/CPLD 邏輯設計的內在規律的體現,合理地采用這些設計思想能在FPGA/CPLD設計工作種取得事半功倍的效果。

2021-04-29 06:04:14

用FPGA/CPLD設計UART

),有時我們不需要使用完整的UART的功能和這些輔助功能。或者設計上用到了FPGA/CPLD器件,那么我們就可以將所需要的UART功能集成到FPGA內部。使用VHDL將UART的核心功能集成,從而使整個設計更加緊湊、穩定且可靠。本文應用EDA技術,基于FPGA/CPLD器件設計與實現UART。

2012-05-23 19:37:24

詳解CPLD/FPGA設計流程

只要有數字電路的基礎,還是能較容易和快速地學會利用 CPLD/FPGA 設計數字系統的。 數字系統的基本部件比較簡單,它們是一些與門、或門、非門、觸發器和多路選擇器等,宏器件是一些加法器、乘法器等

2019-02-28 11:47:32

請問FPGA/CPLD怎么驗證是否正常工作?

,示波器卻沒量到都是高電平,不知道FPGA/CPLD電路到底有沒有正常工作,現在借了一個仿真器(下載器),ISE軟件也下載了,能通過軟件、下載器判斷芯片是不是正常的嗎?還是必須要有工程文件才能判斷?

2020-06-14 09:04:40

請問POWER_SAVING之后串口怎么不能用了?

在POWER_SAVING之后串口怎么不能用了,如果想開啟POWER_SAVING而且串口也能用 該怎么做有沒有官方的例程啊

2019-10-21 10:26:56

這里有電子高手的FPGA/CPLD經驗,快來拿~

技巧,都是FPGA/CPLD邏輯設計內在規律的體現。如何合理地運用好這些設計思想?如何讓我們的FPGA/CPLD設計工作更有效率?看完這篇文章,相信我們會有所收獲。附件下載:本文摘自網絡哈~

2017-02-27 16:24:10

Altera FPGA/CPLD設計(高級篇)

《Altera FPGA/CPLD設計(高級篇)》結合作者多年工作經驗,深入地討論了Altera FPGA/CPLD的設計、優化技巧。在討論FPGA/CPLD設計指導原則的基礎上,介紹了Altera器件的高級應用;引領讀者

2009-02-12 09:19:12 4799

4799

4799

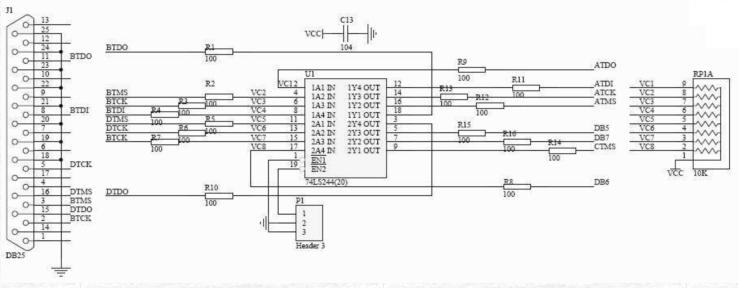

4799FPGA/CPLD下載方式 (ISP下載線接口電路)

FPGA/CPLD下載方式 (ISP下載線接口電路)

SP功能提高設計和應用的靈活性未編程前先焊接安裝系統內編

2009-03-08 10:47:02 129

129

129

129USB-Blaster下載/仿真/調試器-北京革新創展科技有限公司

USB-Blaster的特性: 支持USB Blaster下載仿真調試,通過計算機的USB接口可對Altera的FPGA/CPLD以及配置芯片進行編程、調試等操作

2022-07-27 10:31:29

altera fpga/cpld設計

altera fpga/cpld設計 基礎篇結合作者多年工作經驗,系統地介紹了FPGA/CPLD的基本設計方法。在介紹FPGA/CPLD概念的基礎上,介紹了Altera主流FPGA/CPLD的結構與特點,并通過豐富的實例講解

2009-07-10 17:35:45 57

57

57

57用FPGA/CPLD設計UART

UART 是廣泛使用的串行數據通訊電路。本設計包含UART 發送器、接收器和波特率發生器。設計應用EDA 技術,基于FPGA/CPLD 器件設計與實現UART。關鍵詞 :FPGA/CPLD;UART;VHDLUART(即U

2009-09-29 08:01:20 23

23

23

23基于單片機的CPLD/FPGA被動串行下載配置的實現

基于單片機的CPLD/FPGA被動串行下載配置的實現:介紹采用AT89S2051單片機配合串行E2PROM存儲器,實現CPLD/FPGA器件的被動串行模式的下載配置,闡述了其原理及軟硬件設計。 &nb

2009-10-29 21:57:22 19

19

19

19CPLD器件的配置與編程下載

當利用CPLD/FPGA開發系統完成數字電路或系統的開發設計并仿真校驗通過之后,就需要將獲得的CPLD/FPGA編程配置數據下載到CPLD/FPGA芯片中,以便最后獲得所設計的硬件數字電路或系

2010-06-01 10:14:46 23

23

23

23常用FPGA/CPLD四種設計技巧

常用FPGA/CPLD四種設計技巧

FPGA/CPLD的設計思想與技巧是一個非常大的話題,本文僅介紹一些常用的設計思想與技巧,包括乒乓球操作、串并轉換、流水線操作和數據接口

2010-05-12 11:10:43 766

766

766

766FPGA/CPLD設計思想與技巧

本文討論的四種常用FPGA/CPLD設計思想與技巧:乒乓操作、串并轉換、流水線操作、數據接口同步化,都是FPGA/CPLD邏輯設計的內在規律的

2010-11-04 10:11:28 625

625

625

625

使用CPLD和Flash實現FPGA的配置

本文介紹了通過處理機用CPLD和Flash實現FPGA配置文件下載更新的方法。與傳統的JTAG或PROM串行下載配置方法相比,此方法具有更新配置文件靈活方便、易于操作、適用于大容量FPGA下載的特點

2018-10-25 05:51:00 8194

8194

8194

8194

基于CPLD/FPGA的多串口設計

在工業控制中如何提高一對多的串口通訊可靠性和系統的集成性成為研究熱點。本文利用嵌入式技術,提出基于CPLD/FPGA的多串口擴展設計方案。實現并行口到多個全雙工異步通訊口之間

2011-04-27 11:17:15 111

111

111

111如何解決allegro16.3的stroke不能用的問題

如何解決allegro16.3的stroke不能用的問題.用習慣了allegro里面的stroke,安裝了allegro16.3發現stroke不能用了

2011-11-22 11:03:11 5051

5051

5051

5051關于CPLD和FPGA的區別

CPLD和FPGA都是我們經常會用到的器件。有的說有配置芯片的是FPGA,沒有的是CPLD;有的說邏輯資源多的是FPGA,少的是CPLD;有的直接就不做區分,把他們都叫做FPGA。那么兩者到底有什么區別呢?下面我們就以Altera公司的CPLD和FPGA為例來說說兩者的區別。

2017-09-18 16:35:32 5

5

5

5FPGA和CPLD的區別及其用途介紹

FPGA/CPLD能完成任何數字器件的功能,上至高性能CPU,下至簡單的74電路,都可以用FPGA/CPLD來實現。 FPGA/CPLD如同一張白紙或是一堆積木,工程師可以通過傳統的原理圖輸入法

2017-10-09 09:52:20 14

14

14

14cpld和fpga的區別,cpld和fpga的優缺點

FPGA(Field-Programmable Gate Array),即現場可編程門陣列,它是在PAL、GAL、CPLD等可編程器件的基礎上進一步發展的產物。它是作為專用集成電路(ASIC)領域

2017-10-24 10:04:00 46702

46702

46702

46702CPLD的優勢 FPGA的產生

FPGA LAB和CPLD的LAB設計不同。CPLD LAB由宏單元構成,包括自己的本地可編程陣列,而FPGA LAB由大量的邏輯模塊構成,這些模塊被稱為邏輯單元,即LE,而且本地互連和邏輯分開。LE看起來可能和CPLD宏單元相似,但更容易配置,有更豐富的特性來提高性能,減少邏輯資源的浪費。

2018-04-17 17:02:00 1979

1979

1979

1979

CPLD和FPGA兩者的區別

CPLD和FPGA都是我們經常會用到的器件。有的說有配置芯片的是FPGA,沒有的是CPLD;有的說邏輯資源多的是FPGA,少的是CPLD;有的直接就不做區分,把他們都叫做FPGA。那么兩者到底有什么區別呢?下面我們就以Altera公司的CPLD和FPGA為例來說說兩者的區別。

2018-05-24 02:03:00 49472

49472

49472

49472

FPGA教程之CPLD與FPGA的基礎知識說明

本文檔詳細介紹的是FPGA教程之CPLD與FPGA的基礎知識說明主要內容包括了:一、復雜可編程邏輯器件簡介二、CPLD的組成與特點三、FPGA的組成與特點四、CPLD與FPGA的異同五、主要的PLD廠商

2019-02-27 17:09:32 32

32

32

32FPGA教程之CPLD和FPGA的配置與下載的詳細資料說明

本文檔詳細介紹的是FPGA教程之CPLD和FPGA的配置與下載的詳細資料說明主要內容包括了:一、CPLD/FPGA器件的配置,二、MAX系列非易失性器件的下載配置,三、FLEX/ACEX系列FPGA的下載配置,四、ALTERA的編程文件

2019-02-28 09:56:18 17

17

17

17FPGA和CPLD最好的入門教程的電子書免費下載

本文檔的主要內容詳細介紹的是FPGA和CPLD最好的入門教程的電子書免費下載包括了:1.FPGA/CPLD概述,2.HS102型FPGACPLD實驗板,3.Max+plus1110.2 的使用,Quartus4.2 軟件的使用

2019-03-22 17:04:09 78

78

78

78FPGA的用途以及它與CPLD的不同之處

FPGA/CPLD能完成任何數字器件的功能,上至高性能CPU,下至簡單的74電路,都可以用FPGA/CPLD來實現。

2020-01-20 09:29:00 3264

3264

3264

3264CPLD和FPGA的基本結構

本文主要介紹CPLD和FPGA的基本結構。 CPLD是復雜可編程邏輯器件(Complex Programable Logic Device)的簡稱,FPGA是現場可編程門陣列(Field

2020-09-25 14:56:33 12233

12233

12233

12233

了解FPGA和CPLD架構的基礎知識資料下載

電子發燒友網為你提供了解FPGA和CPLD架構的基礎知識資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-14 08:41:17 13

13

13

13Altera FPGA CPLD學習筆記

Altera FPGA CPLD學習筆記(肇慶理士電源技術有限)-Altera FPGA CPLD學習筆記? ? ? ? ? ? ? ? ?

2021-09-18 10:54:41 79

79

79

79FPGA CPLD數字電路設計經驗分享.

FPGA CPLD數字電路設計經驗分享.(電源技術發展怎么樣)-FPGA CPLD數字電路設計經驗分享? ? ? ? ? ? ? ? ? ??

2021-09-18 10:58:03 51

51

51

51FPGA CPLD中的Verilog設計小技巧

FPGA CPLD中的Verilog設計小技巧(肇慶理士電源技術有限)-FPGA CPLD中的Verilog設計小技巧? ? ? ? ? ? ? ? ?

2021-09-18 16:49:18 35

35

35

35常用FPGA/CPLD設計思想與技巧

都是FPGA/CPLD邏輯設計的內在規律的體現,合理地采用這些設計思想能在FPGA/CPLD設計工作種取得事半功倍的效果。

2023-05-18 08:56:57 350

350

350

350

CPLD與FPGA之間的區別在哪呢?

CPLD和FPGA都是由邏輯陣列模塊構成的,但是CPLD的LAB基于乘積和宏單元,而FPGA的LAB使用基于LUT的邏輯單元。

2023-06-28 11:28:04 862

862

862

862

CPLD和FPGA的區別是什么

可編程邏輯包括 PAL、GAL、PLD 等。通過不斷發展,它已經發展成為現在的CPLD/FPGA。CPLD(復雜可編程邏輯器件)和FPGA(現場可編程門陣列)的功能基本相同,只是實現原理略有不同

2023-07-03 14:33:38 6041

6041

6041

6041

CPLD和FPGA的區別

CPLD和FPGA都是由邏輯陣列模塊構成的,但是CPLD的LAB基于乘積和宏單元,而FPGA的LAB使用基于LUT的邏輯單元。CPLD的LAB圍繞中心全局互連排列,隨著器件中邏輯數量的增加,呈指數

2024-01-23 09:17:04 280

280

280

280 電子發燒友App

電子發燒友App

評論