FIR 濾波器廣泛應用于數字信號處理中,主要功能就是將不感興趣的信號濾除,留下有用信號。##全并行FIR濾波器結構

2014-06-27 10:02:56 8178

8178 FIR 濾波器廣泛應用于數字信號處理中,主要功能就是將不感興趣的信號濾除,留下有用信號。##脈動型(Systolic)FIR濾波器設計

2014-06-30 09:47:40 1872

1872 169數字FIR濾波器

2010-04-07 14:44:08

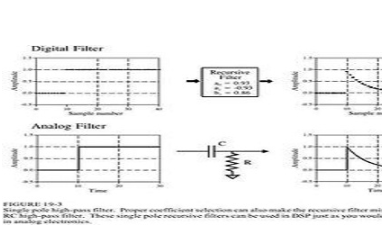

1、FIR 濾波器是在數字信號處理(DSP)中經常使用的兩種基本的濾波器之一,另一個為IIR濾波器。 2、FIR代表有限沖激響應(Finite Impulse Response)的簡稱。 3

2011-09-24 16:05:53

matlab下設計IIR濾波器程序流程框圖IIR與FIR數字濾波器的比較:1、從性能上比較 從性能上來說,IIR濾波器傳輸函數的極點可位于單位圓內的任何地方,因此可用較低的階數獲得高的選擇性,所用的存貯單元少

2016-08-08 08:49:32

與FIR數字濾器的比較FIR和IIR比較(有限沖擊響應和無限沖擊響應)從性能上進行比較 從性能上來說,IIR濾波器傳輸函數的極點可位于單位圓內的任何地方,因此可用較低的階數獲得高的選擇性,所用的存貯單元少

2018-03-12 13:21:07

輸入數據和歷史輸入數據,IIR的濾波輸出取決于當前輸入數據、歷史輸入數據和歷史輸出數據。以基于FPGA硬件的數字濾波器為例,FIR在處理信號時不需等待前一個信號的濾波輸出,只需要考慮輸入數據便可實時

2019-06-27 04:20:31

數字濾波器的類型有FIR(有限長沖擊與IIR(無限長。離散數字系統中,濾波器的表述為差分方程。FIRFIR基本特性:FIR 濾波器永遠是穩定的(系統只有零點);FIR 濾波器的沖激響應是有限長序列

2021-08-17 06:19:17

第一個問題的基礎上,我是設置unsigned還是signed?3、濾波器的設計,我要給他什么樣子的輸入,仿真看得出什么樣子的結果?部分代碼如下

2017-05-09 14:18:17

使用iir濾波器相對fir濾波器可以在使用更小的階數的情況下實現更好的效果。實驗證明,可能20階的iir效果堪比500階左右的fir濾波器效果。首先放出iir的matlab仿真代碼:%本程

2021-12-22 08:29:40

fpga實現濾波器fpga實現濾波器在利用FPGA實現數字信號處理方面,分布式算法發揮著關鍵作用,與傳統的乘加結構相比,具有并行處理的高效性特點。本文研究了一種16階FIR濾波器的FPGA設計方法

2012-08-12 11:50:16

嗨,大家好,我對具有可重載系數的FIR濾波器的行為有疑問。在使用FIR編譯器v6.3生成FIR濾波器之后,我嘗試根據ds795_fir_compiler.pdf文檔的第26頁上的圖10來模擬我

2019-02-27 13:49:35

文章主要講CIC理論基礎,下個文章講FPGA實現。級聯積分梳狀濾波器又稱CIC。這是多速率信號處理中一種結構簡單的濾波器,只需要加法器和寄存器即可實現,可以靈活的設置抽取因子和插值因子,并且CIC是一種

2021-08-17 08:27:40

由200HZ及800HZ單點頻信號疊加的輸入信號。 案例補充說明FIR濾波器,即有限脈沖響應濾波器,顧名思義,是指單位脈沖響應的長度是有限的濾波器。而根據FIR濾波器的結構形式,分為直接型、級聯型

2017-08-02 17:35:24

請教各位大師,quartus ii 中調用fir數字濾波器IP核,可不知道如何設置參數,比如如何設置濾波器的系數

2013-11-23 20:54:41

最近在做一個FPGA的課程設計,遇到一個比較煩人的問題,希望大神們可以指點迷律。一個16階的FIR濾波器,采用分布式算法實現的,采樣率1M,fc=100K,頻率到了30K以上時就會出現那些尖刺,很

2018-02-25 19:25:50

使用verilog設計的FIR濾波器,該濾波器采用了串行結構,占用資源少。雖然FIR濾波器可以用IP核實現,但通過本代碼,可以了解FIR濾波器的結構特點,有助于項目選擇合適的參數。一、功能描述FIR

2017-04-14 15:20:31

FIR濾波器如何定義?為什么要使用FIR濾波器?

2021-04-06 07:48:45

最近進行FPGA學習,使用FIR濾波器過程中出現以下問題:使用FIR濾波器IP核中,輸入數據為1~256,濾波器系數為,coef =-1469,-14299 ,-2185,10587

2018-11-02 17:17:57

基于FPGA的FIR濾波器IP仿真實例 AT7_Xilinx開發板(USB3.0+LVDS)資料共享 騰訊鏈接:https://share.weiyun.com/5GQyKKc 百度網盤鏈接

2019-07-16 17:24:22

設計要求: 利用所學知識,采用VHDL語言完成FIR濾波器的設計仿真。要求用VHDL編程設計底層文件,頂層文件可任意(可用原理圖方式或文本方式);完成仿真文件(包括MATLAB和QUARTUSII

2015-09-18 14:54:46

本帖最后由 eehome 于 2013-1-5 09:50 編輯

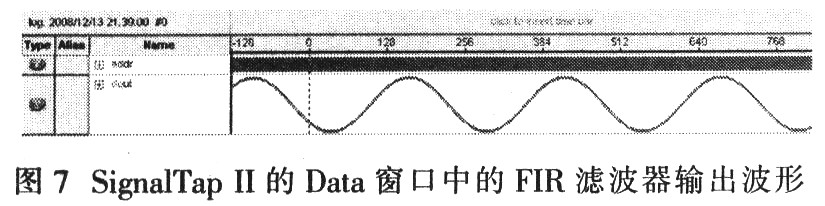

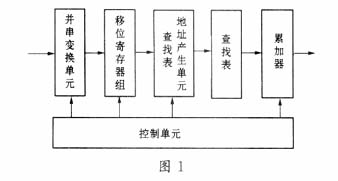

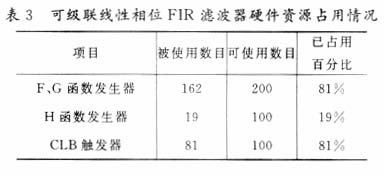

基于FPGA的FIR濾波器設計與實現 文章研究基于FPGA、采用分布式算法實現FIR濾波器的原理和方法,用

2012-08-11 15:32:34

基于FPGA的FIR數字濾波器的優化設計

2012-08-17 23:55:09

(FIR)濾波器和無限脈沖響應(IIR)濾波器兩種。其中FIR數字濾波器具有嚴格的線性相位,而且非遞歸結構也保證了運算的穩定性。

2019-09-29 07:45:43

基于FPGA的fir濾波器實現

2017-08-28 19:57:36

設計一般采用CIC、HB、FIR級聯的形式組成。同時,由于CIC濾波器的通帶性能實在太差,所以中間還要加上一級PFIR濾波器以平滑濾波器的通帶性能。

2019-09-20 06:13:11

本帖最后由 eehome 于 2013-1-5 09:59 編輯

基于FPGA的高階FIR濾波器設計

2012-08-20 18:42:15

Programmable Gate Array,現場可編程門陣列)基于查找表的結構和全硬件并行執行的特性,如何用FPGA 來實現高速FIR 數字濾波器成了近年來數字信號處理領域研究的熱點。目前,全球兩大PLD 器件供應商都提供了加速FPGA 開發的IP(IntelligentProperty,知識產權)核。

2019-09-05 07:21:15

本帖最后由 eehome 于 2013-1-5 09:50 編輯

基于fpga的fir濾波器的實現

2012-08-17 16:42:33

信號,頻率響應特性可做成非常接近于理想的特性,且精度可以達到很高,容易集成等。和IIR 濾波器相比,FIR 濾波器可以得到嚴格的線性相位。而且FIR 濾波器可以用非遞歸方法實現,有限精度的計算不會產生

2008-05-14 23:30:12

系統兼具實時性和靈活性,而現有設計方案(如DSP)則難以同時達到這兩方面要求。而使用具有并行處理特性的FPGA實現FIR濾波器,具有很強的實時性和靈活性,因此為數字信號處理提供一種很好的解決方案。

2019-11-04 08:08:24

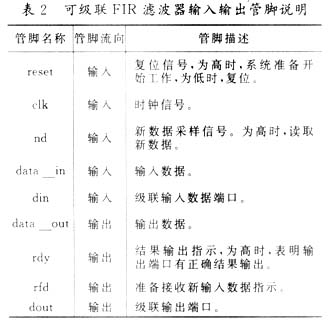

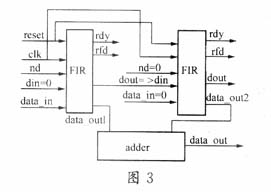

的各個領域。采用INMOS公司的IMS A100級聯型信號處理器為模板,以FIR濾波器設計為核心,用FPGA技術開發設計級聯型信號處理器,能夠應用于數字FIR濾波、高速自適應濾波、相關和卷積、離散

2019-07-30 07:22:48

本文首先介紹了FIR濾波器和脈動陣列的原理,然后設計了脈動陣列結構的FIR濾波器,畫出電路的結構框圖,并進行了時序分析,最后在FPGA上進行驗證。結果表明,脈動陣列的模塊化和高度流水線的結構使FIR

2021-04-20 07:23:59

相位,簡單可擴展到多速率情況,以及充足的硬件支持除了其他原因之外。此示例展示了DSP System Toolbox?中用于設計具有各種特性的低通FIR濾波器的功能。內容獲得低通FIR濾波器系數最小階低通濾波器

2018-08-23 10:00:16

實現FPGA數字下變頻的多類濾波器分組級聯技術分析1 引 言 本文針對以下高效算法做了總結,進行合理的分組級聯并引入流水線技術以便于在FPGA上實現。數字下變頻(DDC)就是通過混頻、抽取和濾波等

2009-10-23 10:26:53

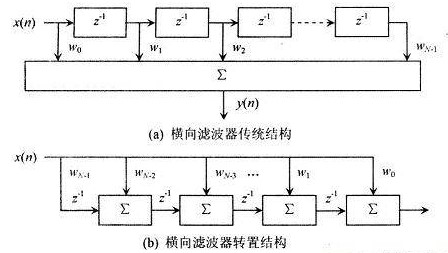

本文將簡單介紹FIR濾波器的原理,詳細介紹使用Verilog HDL設計并行FIR濾波器的流程和方法。接下來幾篇會介紹串行結構FIR的Verilog設計、使用Quartus和Vivado的IP核

2020-09-25 17:44:38

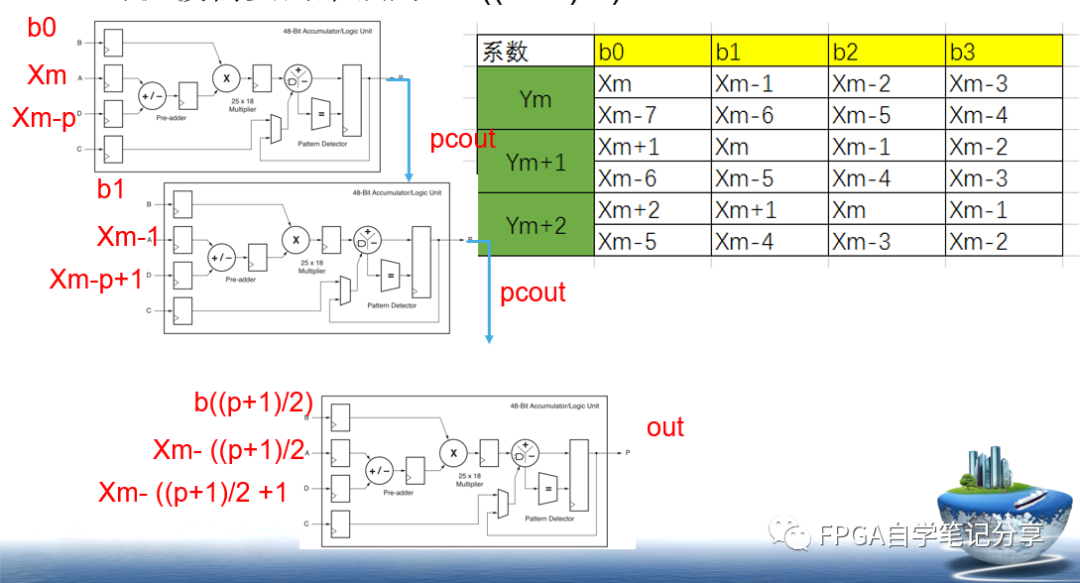

并行流水結構FIR的原理是什么基于并行流水線結構的可重配FIR濾波器的FPGA實現

2021-04-29 06:30:54

目前FIR濾波器的硬件實現的方式有哪幾種?怎么在FPGA上實現FIR濾波器的設計?

2021-05-07 06:03:13

本文以實現抽取率為2的具有線性相位的3階FIR抽取濾波器為例,介紹了一種用XC2V1000型FPGA實現FIR抽取濾波器的設計方法。

2021-05-07 06:02:47

相對無限沖擊響應(IIR)濾波器,有限沖擊響應(FIR)能夠在滿足濾波器幅頻響應的同時獲得嚴格的線性相位特性,而數據通信、語音信號處理等領域往往要求信號在傳輸過程中不能有明顯的相位失真,所以FIR

2019-08-23 06:39:46

相對無限沖擊響應(IIR)濾波器,有限沖擊響應(FIR)能夠在滿足濾波器幅頻響應的同時獲得嚴格的線性相位特性,而數據通信、語音信號處理等領域往往要求信號在傳輸過程中不能有明顯的相位失真,所以FIR

2019-08-27 07:16:54

分方程如下所示:由差分方程可知IIR濾波器存在反饋,因此在FPGA設計時要考慮到有限字長效應帶來的影響。差分方程中包括兩個部分:輸入信號x(n)的M節延時網絡,相當于FIR的網絡結構,實現系統的零點

2020-09-27 09:22:58

最近在學習全相位濾波器,請問有人做過全相位FIR濾波器嗎?能不能用matlab程序來比較一下全相位FIR濾波器與傳統方法設計的FIR濾波器有什么區別??希望有人能幫我解答。。。感激不盡。。。。

2011-05-10 15:34:03

求解答怎么利用IP core設計收音機的FIR濾波器

2013-08-09 17:41:36

具有嚴格的線性相頻特性,同時其單位抽樣響應是有限長的,因而濾波器是穩定的系統。因此,FIR濾波器在通信、圖像處理、模式識別等領域都有著廣泛的應用。Vivado集成的FIR IP核可以實現如下公式所示的N

2020-01-14 09:39:45

的濾波輸出取決于當前輸入數據、歷史輸入數據和歷史輸出數據。以基于FPGA硬件的數字濾波器為例,FIR在處理信號時不需等待前一個信號的濾波輸出,只需要考慮輸入數據便可實時濾波;IIR需要等待上一個信號

2023-05-29 16:47:16

AD9361的FIR濾波器是否可以配置成RRC濾波器?只能用作低通濾波器嗎?另外,FIR濾波器的2/4倍插值是對原信號進行補0嗎?

2019-01-07 11:31:53

利用matlab設計一個線性相位FIR帶通濾波器,并在FPGA上實現。要求:1、濾波器指標:過渡帶帶寬分別為100~300HZ,500~700HZ,阻帶允許誤差為0.02,通帶允許誤差為0.01,采樣

2015-06-16 19:25:35

II 給我們提供的IP 核來做就沒有原來那么麻煩了,所有的工作都交給IP核來工作,我們只需要做的是生成符合要求的濾波器系數,然后仿真正確無誤后交給FPGA處理。上面我們設計完了前兩級的FIR半帶

2015-08-29 15:33:49

用窗函數設計FIR濾波器一、實驗目的1、熟悉FIR濾波器設計的基本方法。2、掌握用窗函數設計FIR數字濾波器的原理及方法,熟悉相應的計算機高級語言編程。3、熟悉線性

2009-05-10 10:02:15 97

97 基于FPGA對稱型FIR濾波器的設計與實現:在基于FPGA的對稱型FIR數字濾波器設計中,為了提高速度和運行效率,提出了使用線性I相位結構和加法樹乘法器的方法,并利用Altera公I司的FPG

2009-09-25 15:38:38 30

30 在軟件無線電的下變頻模塊中,級聯梳狀積分濾波器有著重要的應用,其主要作用是信號的抽取與低通濾波。文中總結了級聯梳狀積分抽取濾波器的理論要點,并介紹了采用FPGA

2010-01-06 15:16:45 31

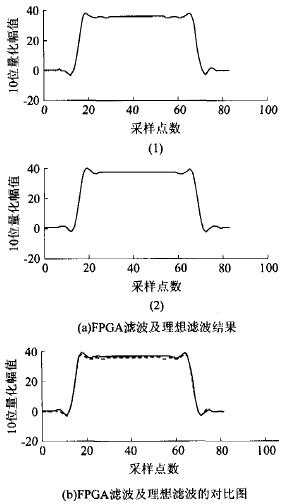

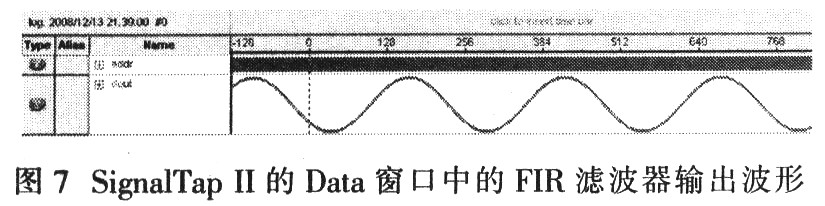

31 基于MATLAB與QUARTUS II的FIR濾波器設計與驗證

FIR濾波器是一種應用廣泛的基本數字信號處理元件。

2010-05-13 17:16:17 53

53 什么是fir數字濾波器

Part 1: Basics1.1 什么是FIR濾波器?FIR 濾波器是在數字信號處理(DSP)中經常使用的兩種

2008-01-16 09:42:22 16243

16243 高效FIR濾波器的設計與仿真-基于FPGA

摘要:該文在介紹有限沖激響應(FIR)數字濾波器理論及常見實現方法的基礎上,提出了一種基于FPGA的高效實現方案。

2008-01-16 09:56:02 1456

1456

如何用用FPGA實現FIR濾波器

你接到要求用FPGA實現FIR濾波器的任務時,也許會想起在學校里所學的FIR基礎知識,但是下一步該做什么呢?哪些參數是重

2009-03-30 12:25:45 4503

4503

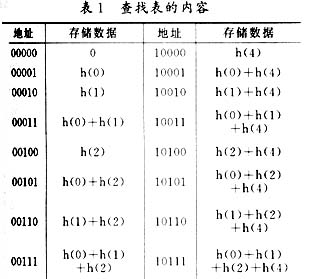

摘要: 針對在FPGA中實現FIR濾波器的關鍵--乘法運算的高效實現進行了研究,給了了將乘法化為查表的DA算法,并采用這一算法設計了FIR濾波器。通過FPGA仿零點驗證

2009-06-20 14:09:36 677

677

FIR 濾波器FAQ (基本知識問答)

1.1 什么是FIR濾波器?

FIR 濾波器是在數字信號處理(DSP)中經常使用的兩種基本的濾波器之一

2009-10-30 08:06:45 1301

1301

FIR帶通濾波器的FPGA實現

引 言??? 在FPGA應用中,比較廣泛而基礎的就是數字濾波器。根據其單位沖激響應函數的時域特性可分為無限沖擊響應(Infinite

2009-11-13 09:55:18 6564

6564

基于MATLAB與QUARTUS II的FIR濾波器設計與驗證

1 引言 FIR數字濾波器能夠滿足濾波器對幅度和相位特性的嚴格要求,避免模擬濾波器的溫漂和噪聲等問題,

2009-12-12 11:23:42 2399

2399

目前FIR濾波器的一般設計方法比較繁瑣,開發周期長,如果采用設計好的FIR濾波器的IP核,則開發效率大為提高。本方案基于Altera公司的Cyclone II系列芯片EP2C8Q208C8N,首先利用MATLAB中的濾

2011-05-06 16:01:30 84

84 基于流水線技術,利用FPGA進行并行可重復配置高精度的 FIR濾波器 設計。使用VHDL可以很方便地改變濾波器的系數和階數。在DSP中采用這種FIR濾波器的設計方法可以充分發揮FPGA的優勢。

2011-07-18 17:09:28 63

63 目前數字濾波器的硬件實現方法通常采用專用DSP芯片或FPGA,本文從FIR濾波器的系數考慮,采用CSD編碼,對FIR數字濾波器進行優化設計。

2011-08-16 10:54:41 3632

3632

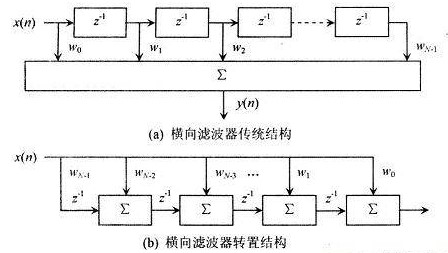

描述了基于FPGA的FIR濾波器設計。根據FIR的原理及嚴格線性相位濾波器具有偶對稱的性質給出了FIR濾波器的4種結構,即直接乘加結構、乘法器復用結構、乘累加結構、DA算法。在本文中給

2012-11-09 17:32:37 121

121 FIR(Finite Impulse Response,有限沖擊響應)數字濾波器具有穩定性高、可以實現線性相位等優點,廣泛被應用于信號檢測與處理等領域。由于FPGA(Field Programmable Gate Array,現場可編程門陣

2012-12-03 11:50:23 5499

5499 fir濾波器的有關資料 fir_濾波器sourc.rar

2015-12-14 14:12:56 24

24 基于matlab和fpga的FIR濾波器設計,有興趣的同學可以下載學習

2016-04-27 15:51:58 56

56 基于FPGA的FIR濾波器設計與實現,下來看看

2016-05-10 11:49:02 38

38 基于MATLAB的FIR濾波器設計與濾波。

2016-12-14 22:08:25 63

63 基于FPGA實現變采樣率FIR濾波器的研究

2017-01-08 15:59:09 19

19 FIR濾波器,即有限脈沖響應濾波器,顧名思義,是指單位脈沖響應的長度是有限的濾波器。而根據FIR濾波器的結構形式,分為直接型、級聯型、頻率取樣型和快速卷積型。其中直接型又可以采用串行結構、并行結構、分布式結構。本案例實現了具有線性相位的半串行結構的FIR濾波器。

2017-04-20 14:42:14 2186

2186 數字濾波器廣泛應用于硬件電路設計,一般分為FIR濾波器和IIR濾波器。那么FIR濾波器和IIR濾波器有什么區別呢?本文通過幾個例子做一個簡單的總結。

2017-05-03 11:36:31 19

19 基于MATLAB與QUARTUS+II的FIR濾波器設計與驗證

2017-09-18 10:17:37 11

11 研究了一種采用FPGA實現32階FIR濾波器硬件電路方案;討論了窗函數的選擇、濾波器的結構以及系數量化問題;研究了FIR濾波器的FPGA實現,各模塊的設計以及如何優化硬件資源,提高運行

2017-11-10 16:41:57 15

15 摘要:有限沖擊響應(FIR)濾波器是數字通信系統中常用的基本模塊。文章設計了一種流水結構的FIR濾波器,通過FPGA對其進行硬什加速控制。仿真結果驗證了所設計的FIR流水結構濾波器功能的正確性

2017-11-18 06:15:02 1259

1259

針對傳統的FIR 濾波器的缺點,介紹了一種基于FPGA 乘法器的FIR 濾波器設計方法,該濾波器利用FPGA 自帶的18位乘法器MULT18 × 18SIO 進行乘法計算,利用寄存器對相乘結果進行

2017-11-22 07:39:45 2735

2735

本文針對快速、準確選擇參數符合項目要求的濾波器設計方法的目的,通過系統的介紹有限脈沖響應( Finite Impulse Response,FIR)濾波器的原理、結構形式以及幾種FIR濾波器設計方法

2017-12-21 14:53:14 14

14 文介紹了FIR抽取濾波器的工作原理,重點闡述了用XC2V1000實現FIR抽取濾波器的方法,并給出了仿真波形和設計特點。

2018-04-19 11:34:00 1846

1846

用FPGA實現抽取濾波器比較復雜,主要是因為在FPGA中缺乏實現乘法運算的有效結構,現在,FPGA中集成了硬件乘法器,使FPGA在數字信號處理方面有了長足的進步。本文介紹了一種采用Xilinx公司的XC2V1000實現FIR抽取濾波器的設計方法。

2018-04-28 11:50:00 1073

1073

基于靈活自適應的空口波形技術FOFDM(Filtered OFDM)是現代通信技術的研究熱點,設計并實現可調FIR濾波器是實現該技術的核心工作之一。本文設計的基于FPGA的可調節FIR濾波器系數

2018-07-23 17:21:00 2372

2372

在數字信號處理領域,濾波器無疑是個非常重要的環節。而在數字濾波器中,有限脈沖響應(FIR)濾波器因為其線性相位的特點,應用尤為廣泛。實際應用中FIR濾波器分為常系數FIR濾波器和變系數FIR濾波器

2019-04-22 08:07:00 5006

5006

用FPGA實現抽取濾波器比較復雜,主要是因為在FPGA中缺乏實現乘法運算的有效結構,現在,FPGA中集成了硬件乘法器,使FPGA在數字信號處理方面有了長足的進步。本文介紹了一種采用Xilinx公司的XC2V1000實現FIR抽取濾波器的設計方法。

2020-09-25 10:44:00 3

3 你知道FIR濾波器與IIR濾波器的不同點嗎?它有有什么特點?濾波器是工程師工作中必不可少的器件,濾波器分為很多種,本文詳細介紹一下FIR濾波器與IIR濾波器之間的區別。

2020-08-09 14:15:00 31385

31385

提出一種新的高階FIR濾波器的FPGA實現方法。該方法運用多相分解結構對高階FIR濾波器進行降階處理,采用改進的分布式算法來實現降階后的FIR濾波器。設計了一系列階數從8到1 024的FIR濾波器

2021-03-23 15:44:54 30

30 數字濾波器從實現結構上劃分,有FIR和IIR兩種。FIR的特點是:線性相位、消耗資源多;IIR的特點是:非線性相位、消耗資源少。由于FIR系統的線性相位特點,設計中絕大多數情況都采用FIR濾波器。

2022-04-24 14:40:16 2492

2492 本文介紹了設計濾波器的FPGA實現步驟,并結合杜勇老師的書籍中的串行FIR濾波器部分進行一步步實現硬件設計,對書中的架構做了簡單的優化,并進行了仿真驗證。

2023-05-24 10:56:34 552

552

本文介紹了設計濾波器的FPGA實現步驟,并結合杜勇老師的書籍中的并行FIR濾波器部分進行一步步實現硬件設計,對書中的架構做了復現以及解讀,并進行了仿真驗證。

2023-05-24 10:57:36 653

653

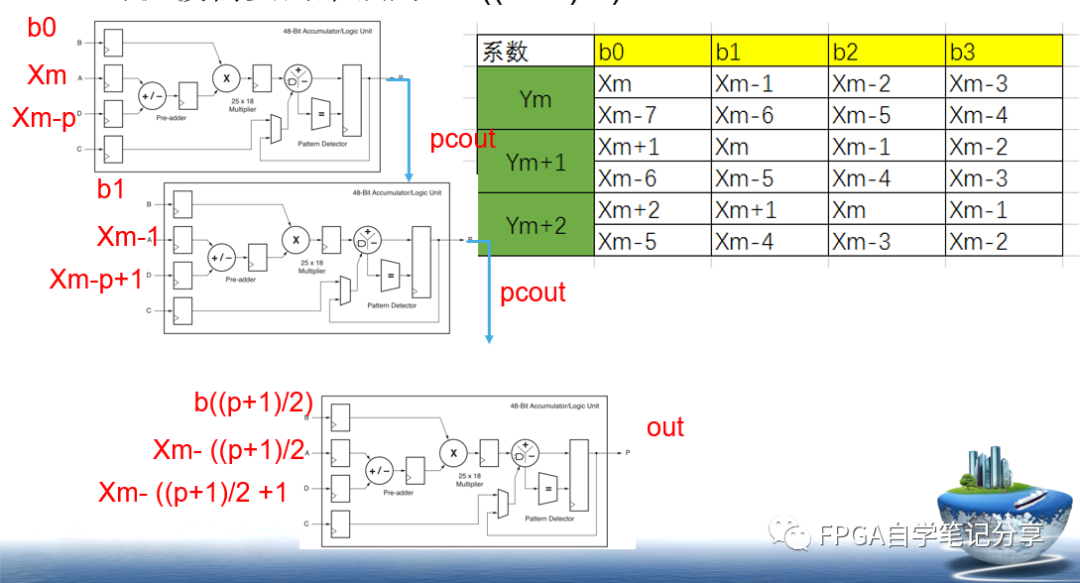

上文 FPGA數字信號處理之濾波器2_使用dsp48e1的fir濾波器設計完成了結構設計。

2023-06-02 12:36:22 718

718

數字濾波器是數字信號處理中最常用的一種技術,可以對數字信號進行濾波、降噪、增強等處理,其中最常見的兩種數字濾波器是IIR濾波器和FIR濾波器。本文將從IIR濾波器和FIR濾波器的原理、特點和應用等方面進行詳細介紹,以便更好地理解兩種濾波器的區別。

2023-06-03 10:21:43 12909

12909 電子發燒友網站提供《如何使用HLS加速FPGA上的FIR濾波器.zip》資料免費下載

2023-06-14 15:28:49 1

1

![]()

![]()

![]()

電子發燒友App

電子發燒友App

評論