在當今要求最苛刻的數字信號處理(DSP)系統設計和開發中,賽靈思的FPGA產品扮演著越來越重要的角色,這一點并非偶然。經過二十多年的研究和工程開發,以及與數百家DSP客戶的密切合作,賽靈思的FPGA產品已經演化為高價值的DSP解決方案平臺,在性能、靈活性、上市時間以及產品壽命方面都提升到了極高的水平,同時還大大降低了總體系統成本和功耗。

眾所周知,FPGA能夠利用高度并行結構在單個時鐘周期內完成復雜算法。目前的FPGA在單個器件內能夠提供每秒數百上千(MSPS)和每秒數十億乘法累加操作(GMACS)的性能。擁有如此高的DSP性能水平,設計人員可以選擇降低FPGA的時鐘速率來節省功耗,也可以選擇實現更多通道來降低系統成本并降低材料清單成本(BOM)。

盡管如此,FPGA解決方案不僅具有如此大的成本/性能優勢,而且在靈活性、上市時間以及產品壽命方面的價值同樣非常誘人。對那些對高性能DSP技術有高需求且發展迅速的市場,包括通信、多媒體、視頻與圖像(MVI)以及國防行業等,都處于快速變化之中。不斷變化的標準、市場需求和客戶要求,瞬息萬變的經濟形勢和競爭態勢為能夠通過創新和靈活性跟上變化步伐的企業帶來了巨大的商業機會。對于越來越多的系統設計師和DSP設計人員來說,FPGA成為首選的平臺。

賽靈思XtremeDSP計劃

2000年11月,賽靈思公司啟動了XtremeDSP?計劃,旨在為滿足通信、多媒體、視頻與圖像以及國防行業對高性能DSP的需求提供不斷演化的、針對應用優化的DSP解決方案產品線。其首要任務包括:

不斷擴展為DSP設計提供的高性能器件產品線

提供開發板和開發套件、參考設計和IP

推出用于不同DSP系統設計方法的設計和開發工具

與業界和大學建立戰略合作伙伴關系,提供培訓和支持

極高的性能和靈活性

性能、系統級成本和功效、更快的上市時間和靈活性是基于FPGA進行DSP設計的標志。所有這些價值優勢都是通信等行業中的領導廠商所迫切需要的。

全球對于更高質量、更大帶寬和更低成本的有線和無線話音、計算機和視頻數據通信的需求空前高漲。受此推動,新通信標準的數量和復雜性都在以指數級的速度增加。這很大原因是需要在傳統網絡和下一代網絡中的眾多通信層之間實現互操作性和數據交換。而且,通過無線方式提供新服務的需求不斷增加,這也是推動當今標準發展熱潮的重要原因。對于系統供應商來說,跟上這些標準的演進并且滿足極為關鍵的性能-價格-功耗比要求并不是一件容易的事。

對于高性能DSP解決方案所服務的動態市場來說,FPGA的靈活性意味著:

更高層次的集成以降低系統成本

領先的算法解決方案和標準實施支持更快速的上市時間,從而可大大提高市場份額

遠程調節易操作,適應無法預測的環境和功能變化(從而降低運營成本)

延長現有設計的生命周期(從而降低資本支出)

創新產品設計和移植的完美平臺,從而可跟上不斷變化的客戶需求和市場要求。

XtremeDSP器件產品線

XtremeDSP產品線包括 Virtex?-DSP 和 Spartan-DSP系列產品,為滿足廣泛的應用需求提供了豐富的價格、性能、功效、帶寬和IO組合。Virtex-5 SXT和Spartan-3A DSP產品是最近增加的新成員。

圖 1.XtremeDSP器件產品線

Virtex-5 SXT –最高的性能和連接功能

Virtex-5 SXT平臺進一步拓展了賽靈思公司的XtremeDSP?產品線,其中的三款新器件可滿足下一代無線、國防以及多媒體、視頻和圖像等應用對超高DSP帶寬和更低系統成本的要求。SXT是四個65nm Virtex-5 FPGA平臺中的第三個。隨著SXT平臺的推出,現在賽靈思FPGA可在550MHz時鐘下提供超過350 GMACS的DSP性能,同時與先前的90nm一代產品相比,動態功耗降低35%。Virtex-5 SXT平臺還是業界第一個通過低功耗收發器(達3.2 Gbps)提供串行連接功能的DSP優化的FPGA系列產品。

除了利用65nm ExpressFabric?技術提升邏輯性能以外,所有Virtex-5 FPGA都集成了用戶可配置的DSP48E邏輯片。

DSP48E邏輯片是乘法累加(MAC)功能模塊的新發展。這些DSP引擎可在高達550 MHz的頻率下執行MAC操作。FPGA能夠實現高度并行的架構,從而使DSP性能比分立DSP處理器提高了兩個數量級以上,并且每個通道的成本和功耗達到了最低。

Virtex-5 SXT器件的邏輯密度范圍為35,000至95,000邏輯單元,同時專用DSP48E邏輯片的數量為192至640。集成多達11.6 Mbit嵌入式BlockRAM 和分布式RAM,這些器件提供了最高的存儲器邏輯資源比,可以高效地實現視頻處理和醫療圖像市場中DSP應用所需要的存儲器密集功能。

Virtex-5 SXT平臺還集成了低功耗RocketIO? GTP收發器 (典型規格為《100mW @ 3.2 Gbps)以及在Virtex-5 LXT平臺首次內建的PCI Express?端點和以太網MAC模塊。兩個平臺均支持所有主要的串行I/O 協議 (PCIe?、CPRI、OBSAI、SRIO、GbE和XAUI),能夠為芯片與芯片、板與板以及機箱與機箱之間的高速大帶寬連接提供功耗最低的解決方案。

Spartan-3A DSP 平臺 –突破性的性價比

在為特定應用尋求最佳DSP解決方案的過程中,設計人員通常要在價格、性能和功耗之間進行大量的折衷,通常需要犧牲一項或多項性能來滿足另外一些方面的要求。Spartan-3A DSP平臺是賽靈思XtremeDSP產品線中的另一個新成員,同時也是第一個針對DSP優化的Spartan FPGA系列產品。Spartan-3A DSP將這三項關鍵的性能完美地結合起來,為大量應用提供了最佳組合。

信號處理容量

Spartan-3A DSP平臺量產時的單價低于30美元 ,在小尺寸封裝中可提供30 GMACS以上的DSP性能和高達2,200 Gbps的存儲器帶寬。這代表著前所未有的性能/價格突破,滿足了大量對價格和功耗都很敏感的應用的要求。這些應用包括單通道微蜂窩無線基站中的數字頭端(DFE)和基帶解決方案、軍用移動軟件定義無線電(SDR)、超聲系統、輔助駕駛/多媒體系統、高分辨率(HD)視頻以及智能IP相機等。

而且,擁有多達53,712邏輯單元、2,268 Kb BlockRAM、373 Kb分布式RAM、519個I/O引腳以及DeviceDNA安全技術和新的休眠/待機電源管理功能,Spartan-3A DSP器件提供了足夠的信號處理容量,可以將價格/性能/功耗比降到更低水平。此外,基于FPGA的DSP解決方案所提供的設計靈活性以及快速上市時間進一步降低了風險,因此Spartan-DSP系列的價值變得越來越明顯(參見表1)。

表1:Spartan-DSP平臺填補了XtremeDSP產品線中的1-30 GMACS性能范圍

注意:1)在低速度級器件中。2)在高速度級器件中

將DSP性能提升到極限

過去二十年里算法復雜性的快速提升是推動FPGA在DSP應用中使用的最重要市場動力。 固定架構的處理器如DSP和通用處理器(GPP)面臨的問題是,固有的架構無效性使它們的性能限制在摩爾定律規定的理論限定值以下 。

此外,由于通信系統將數據傳輸效率不斷推向香家定理(Shannon’s Law ) (參見圖2)所限制的上限,里德-所羅門(Reed-Solomon)編碼以及最近的Turbo碼等高級技術也越來越靠近其理論極限,當然代價就是更高的計算復雜性。

這就導致了算法性能要求和處理器性能之間的差距越來越大。因此,設計人員必須尋找新的設計解決方案(不局限于傳統DSP范圍),在固定結構處理器之外選擇FPGA。

圖 2.賽靈思FPGA填補算法復雜性和固定架構處理器無效性造成的性能差距

由于FPGA并行處理機制可提供極高性能的信號處理能力,因此非常適于來填補這一性能差距。FPGA靈活的架構使得可以方便地在相似系列器件之間進行設計移植,因此可以將標準甚至環境條件變化帶來的風險降到最低。

DSP48E邏輯片

在XtremeDSP產品線所有器件中最有價值的資源之一就是DSP48邏輯片,它不僅幫助提升DSP設計的總性能,同時還可以提高實現所需要性能的設計和資源效率。DSP48是面向應用的組合模塊(ASMBL?),可增強Virtex-DSP 和 Spartan-DSP器件中的DSP功能。這些DSP49邏輯片可幫助DSP設計人員設計出滿足復雜挑戰的解決方案,例如:成百上千的中頻-基帶下轉換信道、3G擴頻系統中的128X片碼速處理、高分辨率H.264和MPEG-4編碼/解碼算法。

一個DSP48基本片(也稱為 XtremeDSP基本片)包含兩個DSP48邏輯片,構成通用粗粒度DSP架構的基礎。DSP48邏輯片支持多種獨立功能,包括乘法器、乘法-累加器(MACC)、加法乘法器、三端輸入加法器、桶狀移位寄存器、寬總線多路復用器、幅度比較器或寬輸入加法器。不需要使用通用可編程邏輯構造資源,這一架構就可支持將多個DSP48 邏輯片連接起來完成更寬輸入的數字功能、DSP濾波器和復雜算法。這可以帶來更低的功耗、極高的性能和更高的芯片資源使用效率。

DSP邏輯片帶來的另一項重要優點是可以從一個平臺系列移植到另一個平臺系列,例如,從Virtex-4 SX或Virtex-5 SXT 器件移植到Spartan-3A DSP器件。由于DSP48是Virtex-DSP和Spartan-DSP系列的基本DSP構造模塊,因此從一個系列移植到另一個系列器件是很直接的過程,設計需要做的更改很小。

XtremeDSP設計工具

通過XtremeDSP計劃,賽靈思及其第三方合作伙伴構成的業界生態系統達成了這樣的共識,即將DSP的所有潛力和靈活性盡可能方便地提供給三類不同的設計人群:系統設計師、DSP工程師和FPGA/硬件工程師。每一類設計人員承擔的職責不同(還有偏好),從而造成了他們對特定設計環境的要求不同。

系統設計師必須快速確定如何在可用的處理資源之間最好地劃分不同的系統級功能。他們關注的重點是選擇滿足產品性能和吞吐能力要求的處理資源,同時滿足尺寸、成本和功耗方面的預算。

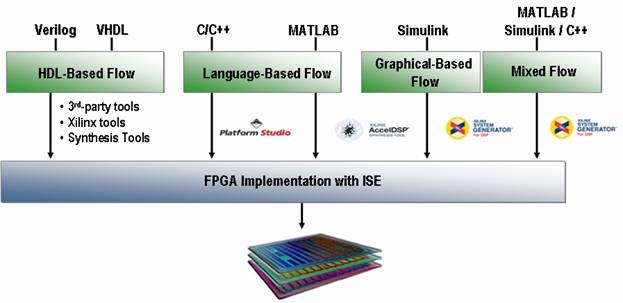

圖 3.XtremeDSP設計工具滿足所有三類設計用戶群體的設計環境要求(喜好)-系統設計師、DSP工程師和FPGA/硬件工程師

DSP工程師更關注DSP算法的創建和改進。他們通常不熟悉硬件設計細節,要依賴工具將細節抽象掉,這樣他們才能夠更專注于更高層的設計探索和驗證。

硬件工程師通常采用VHDL 或 Verilog來從設計中獲得最高的性能。他們通過需要在同一設計環境中與更高層功能模塊以及自己的寄存器傳輸級(RTL)設計協同工作的能力,并且可以運行測試基準進行功能和性能驗證。

因此XtremeDSP計劃是否能夠取得成功的一個關鍵標志就是在于設計工具滿足所有三類設計群體的程度。XtremeDSP工具,如SystemGenerator for DSP 和 AccelDSP? 綜合軟件提供了系統建模、算法開發和探索、自動生成測試基準向量、設計驗證和調試以及HDL生成和仿真等功能。無論某個設計師是喜歡使用VHDL、Verilog、C/C++、MATLAB、Simulink和HDL,還是這些工具的任何組合,賽靈思的XtremeDSP工具都可以幫助他/她快速高效地充分發揮FPGA的所有潛力(參見圖3)。

結論

FPGA填補了高性能應用對高性能DSP的需求與傳統DSP處理器能夠提供的性能之間巨大且不斷增加的差距。有許多原因促使設計人員采用基于FPGA的DSP解決方案,其中四條最基本的原因歸納如下:

處理極高的計算工作量 - FPGA支持工程師設計高度并行的架構,因此可支持與時鐘頻率相同的采樣速率。系統因此可以保持高達500MSPS的高性能水平 – 適于構建超高速單通道系統或慢速率數百通道系統。

從DSP處理器分流計算密集的任務,將寶貴的執行周期讓給其它功能。

定制適用于特定算法的架構 - FPGA提供的一系列MAC或乘法器可用于實現單抽頭或多抽頭的算法架構。FPGA的可重配置特點意味著工程師可以快速構建和修改設計架構。

降低系統成本和功耗 - FPGA支持集成其它組件(如Serial RapidIO 收發器、PCI Express接口、膠合邏輯以及低速率控制任務),因此可以降低總體系統成本和功耗。此外,與傳統DSP器件相比,并行機制提供了一個至幾個數量級的性能優勢,因此對于同樣的性能,可以在更低的頻率下工作。更低的頻率可降低MOPS/mW(功效的最關鍵指標)。正如加州伯克利大學電子工程和計算機科學系Bob Brodersen教授所證明的,與當今的基準微處理器相比,FPGA的功率效率可高達其1000倍。

自啟動以來,賽靈思 XtremeDSP計劃已經推出了一系列針對應用優化的DSP解決方案,這些解決方案結合了專用硬件平臺、設計工具、參考設計、系統級應用知識、軟件算法以及IP庫。這些XtremeDSP解決方案提供如此強大的設計平臺和環境,可為通信、多媒體、視頻和圖像以及國防應用提供性能接近極限的DSP設計。

責任編輯:gt

電子發燒友App

電子發燒友App

評論