1.引言

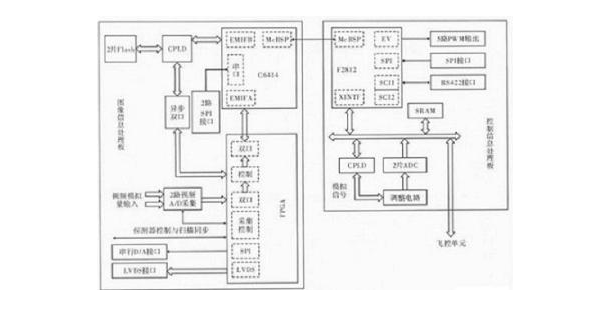

本文針對紅外圖像處理系統的實時性要求,提出了基于DSP+FPGA+ASIC的圖像處理架構。

隨著紅外焦平面陣列技術的快速發展,紅外成像系統實現了高幀頻、高分辨率、高可靠性及微型化,在目標跟蹤、智能交通監控中得到了越來越多的應用,并向更加廣泛的軍事及民用領域擴展。實時紅外圖像處理系統一般會包括非均勻校正、圖像增強、圖像分割、區域特征提取、目標檢測及跟蹤等不同層次的實時圖像處理算法,由于圖像處理的數據量大,數據處理相關性高,因此實時紅外圖像處理系統必須具有強大的運算能力。目前有些紅外圖像處理系統使用FPGA實現可重構計算系統[1],運算速度快,但對于復雜算法的實現難度比較高,且靈活性差。大多數紅外圖像處理系統則采用DSP+FPGA的硬件架構[2],其中DSP負責實現圖像處理算法,FPGA負責實現各種接口電路,但諸如圖像多級濾波等處理算法復雜度高,只使用DSP處理會耗費大量時間,一般采用并行多DSP系統以滿足實時性要求[3],但系統比較復雜,體積和功耗也不好控制,實現成本高。因此需要在硬件結構上合理分配處理任務,比如FPGA可以完成輸入圖像的預處理工作,減輕DSP的負擔,本實驗室自主研制的ASIC芯片可以對輸入紅外圖像進行多級濾波處理,進一步解放DSP。

2.實時紅外圖像處理系統

? 由于實時紅外小目標檢測算法的前端處理數據量大、實時性強且算法復雜度高,我們的系統結構需要保證靈活性,能夠適應各種復雜的算法,同時又要保證高速處理能力,因此實時紅外圖像處理系統采用DSP+ FPGA+ASIC的架構來滿足設計的要求。其中,DSP具有高度的可編程性,可以完成比較復雜的任務。FPGA的處理速度稍遜于ASIC,但具有一定的靈活性,它可以實時接收紅外小目標檢測算法前端的數據,完成輸入圖像的一些預處理工作。ASIC芯片處理速度快、性能強且可靠性好,可以完成圖像濾波等特定的任務。

? FPGA采用ALTERA公司的Stratix系列的EP1S10芯片。該芯片提供多達10,570個邏輯單元(LEs),存儲器容量為920,448016 bits,同時提供了高速DSP模塊以及乘法器,專用乘法器適合于作協處理器,可以分擔DSP復雜和耗時的算術運算,提升系統的性能。

? DSP選用TI公司的TMS320C6414芯片[4]。該芯片主頻為600MHz,數據處理能力峰值可達4800MIPS(每秒48億條指令)。由8個相互獨立的功能單元構成。包含兩組通用寄存器組,每組含有32個32位寄存器。片內采用2級存儲器結構。

? ASIC使用本實驗室自主研制的多級濾波芯片[5]。該芯片采用SMIC 0.35?m工藝,芯片內部工作頻率可達50MHz。有三個數據通道,分別級連不同數量的1*3基本濾波模板,每路數據通道采用流水線結構。采用定點運算,計算精度為8位二進制小數,可處理位寬為8-16位的數據,吞吐量為5M-10M像素/秒,支持128*128,256*256,320*240三種幀格式的圖像濾波。

3.處理任務的合理分配

? 紅外探測器輸出圖像數據到信號處理板,先進入FPGA進行預處理,預處理包括非均勻性校正和圖像增強等。ASIC對輸入圖像數據進行多級濾波處理。FPGA在后續算法中也能協同DSP工作,算法中對運行速度要求很高,而算法結構不太復雜的處理均可在FPGA 中實現,從而使得該FPGA 成為DSP 的協處理器。經過預處理后的紅外圖像數據輸出到DSP中進行后續算法處理,DSP的處理包括紅外潛在小目標檢測算法。DSP 處理后的潛在小目標和圖像數據通過FPGA傳輸到DPRAM中存儲。

? 該實時紅外圖像處理系統主要由三部分組成:FPGA模塊,DSP模塊和ASIC模塊。在滿足紅外圖像數據處理的實時性和高速可靠性要求的前提下,各處理模塊所處理的任務要盡量達到平衡。

? 從資源角度看,算法用硬件處理速度快,占內存空間小,但靈活性差;用軟件剛好相反,處理速度慢,但靈活性好。由于設計要滿足實時性要求,希望硬件承擔的任務越多越好。PGA作為一種可編程的硬件資源,雖然它有相當強的設計靈活性,但是考慮到設計、實現調試的難度,不適合做全局、復雜的操作。ASIC芯片處理速度快,但靈活性差,只適合處理一些特定的占用大量處理器資源的運算。DSP作為軟件資源,特點是靈活性好,適合復雜的算法,但速度慢。

? 從算法角度考慮,一個完整的算法在處理上是有層次的,算法對原始數據的操作是簡單的、規則的,對后續數據的處理往往比較復雜,同時算法在實現前會被預先分成幾個相互獨立的功能模塊。因此低層的、簡單的操作可以由FPGA中的邏輯單元模塊或ASIC芯片硬件來完成,高層的、復雜的操作則由DSP軟件來完成。

? 根據上述分析,本設計中FPGA主要完成與各個外部設備的接口控制邏輯,同時完成一些數據量大、運算結構簡單、速度要求高的算法;DSP完成后續結構復雜的目標檢測算法;ASIC芯片對輸入圖像進行多級濾波處理。此方案保證了系統有足夠的處理速度,能夠達到紅外圖像處理系統的實時性要求。

3.1 FPGA模塊

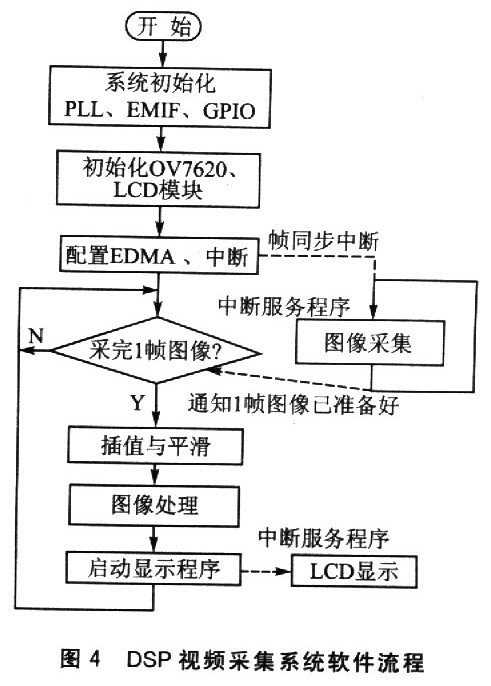

? FPGA內部邏輯結構框圖如圖2所示。 圖2 FPGA內部邏輯結構框圖

? FPGA主要完成以下幾方面的工作:圖像數據接收邏輯,圖像數據預處理模塊,輸入緩存FIFO,DSP接口控制邏輯,ASIC接口控制邏輯,DPRAM接口控制邏輯,算法處理模塊。

? (1) 圖像數據接收邏輯:根據探測器輸出的數字視頻信號的場同步,行同步以及時鐘信號,發送控制信號接收圖像數據。

? (2) 圖像數據預處理模塊:對接收的圖像數據進行非均勻性校正和圖像增強等預處理。

? (3) 輸入緩存FIFO:由FPGA內部配置輸入緩沖存儲器FIFO。預處理后的圖像數據可以連續不間斷地寫入FIFO中,以供DSP讀取進行后續的圖像處理。

? (4) DSP接口控制邏輯:DSP 接口時序控制邏輯必須嚴格按照TMS320C6414的EMIFA可編程同步接口的時序來編寫,并且滿足相應的建立保持時間要求。DSP啟動EDMA通道讀取紅外圖像數據,通過FPGA的內部FIFO進行連續的圖像傳輸。

? (5) ASIC接口控制邏輯:按照ASIC芯片的時序編寫其控制邏輯,將圖像數據導入ASIC芯片進行圖像多級濾波處理。

? (6) DPRAM接口控制邏輯:編寫DPRAM的控制邏輯,將DSP 處理后的數據通過FPGA傳輸到DPRAM中存儲。??

(7) 算法處理模塊:根據具體算法的需要,協同DSP完成算法中速度要求高,結構不太復雜的運算。

3.2 DSP模塊

DSP主要完成紅外小目標的檢測和跟蹤算法,功能如下:

? (1) 啟動EDMA通道不斷讀取FPGA輸出的紅外圖像數據。

? (2) 對輸入的紅外圖像數據,運行目標檢測和跟蹤算法,檢測運動目標,并確定其方位。

? (3) 與FPGA建立連接,將算法中比較規則的運算交給FPGA處理。

? (4) DSP將處理后的運算結果通過FPGA傳輸至DPRAM中存儲。

3.3 ASIC模塊

? ASIC芯片從FPGA中接收預處理后的圖像數據進行處理,處理后的三路數據同步寫入內部三個同步FIFO,DSP可以根據需要選擇輸出多級濾波處理后的結果,進行后續算法的處理。

4.實驗結果與分析

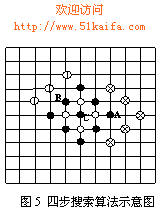

實時紅外圖像處理板已成功應用于多個紅外探測系統中,效果良好。圖3為實驗時采用 高德IR108D探測器獲得的原始紅外圖像,圖4為經過多級濾波處理后標識的圖像,圖5為經過目標檢測算法處理后輸出的跟蹤圖像。可以看到,該系統能夠實時檢測并跟蹤紅外圖像中的運動小目標。 圖3 原始紅外圖像 圖4 多級濾波處理后標識的圖像 圖5 目標跟蹤圖像

5.結語

? 本文使用高性能的DSP(TMS320C6414),可編程邏輯器件FPGA(Stratix系列的EP1S10) 和專用ASIC多級濾波芯片,提出了DSP + FPGA + ASIC的圖像處理平臺架構,設計了處理能力強、接口可靠穩定的紅外圖像處理系統,并在系統中實現了非均勻性校正、小目標檢測等算法。實驗測試表明,該實時紅外圖像處理系統對每場320×240有效像素,每個像素14bit,場頻50Hz的輸出數字視頻信號能夠進行實時處理,對視場中的運動小目標完成檢測和跟蹤功能,滿足系統主要性能指標要求,成功應用于紅外探測系統中。

? 本文作者創新點:采用自主研制的ASIC芯片對紅外圖像進行多級濾波處理,速度快,可靠性好,為DSP后續的目標檢測跟蹤算法節約時間。

參考文獻:

? [1] L.Kessal, N.Abel, D.Demigny. Real-time image processing with dynamically reconfigurable architecture[J]. Real-Time Imaging, 2003,9:297-313.

[2] 應家駒,何永強. 基于DSP和FPGA的超大視場紅外目標檢測圖像處理系統設計[J]. 微計算機信息,2006,22(3-2):161-165.

[3] 顏露新,張天序,鄒勝,鐘勝. 用FPGA實現互聯的多DSP并行系統結構[J]. 系統工程與電子技術, 2005,27(10):1757-1759.

[4] TMS320C6414, TMS320C6415, TMS320C6416Fixed-point Digital Signal Processors[R]. Texas Instruments Inc., 2003.

[5] 陳朝陽,孫劍偉,鄭兆青,張天序. 多級濾波算法的ASIC實現[J]. 華中科技大學學報, 2006, 34(2):4-7.

電子發燒友App

電子發燒友App

評論